Преобразователь синусно-косинусных сигналов в последовательность импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1381705

Авторы: Дробышевский, Снигирь, Ярухин

Текст

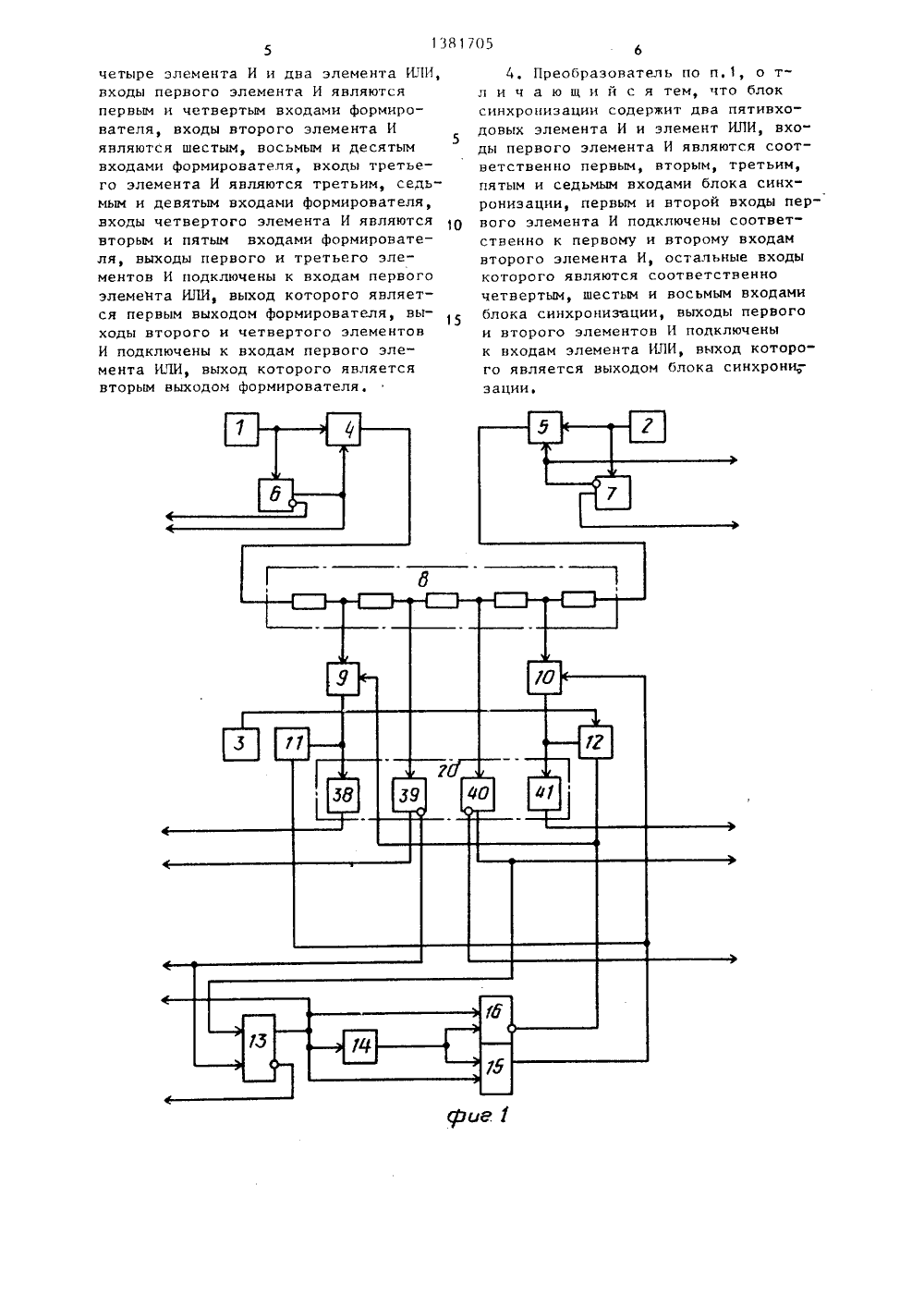

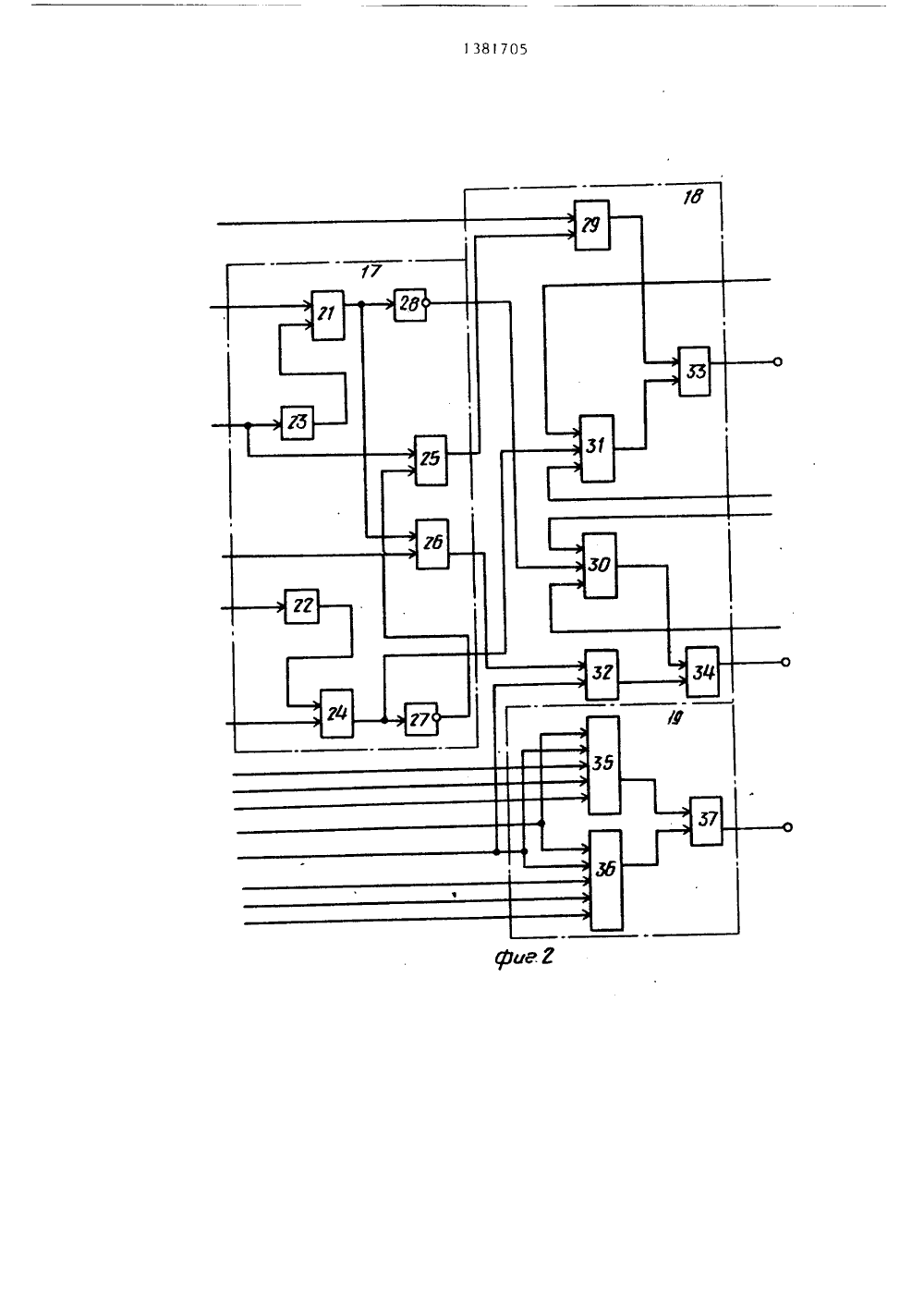

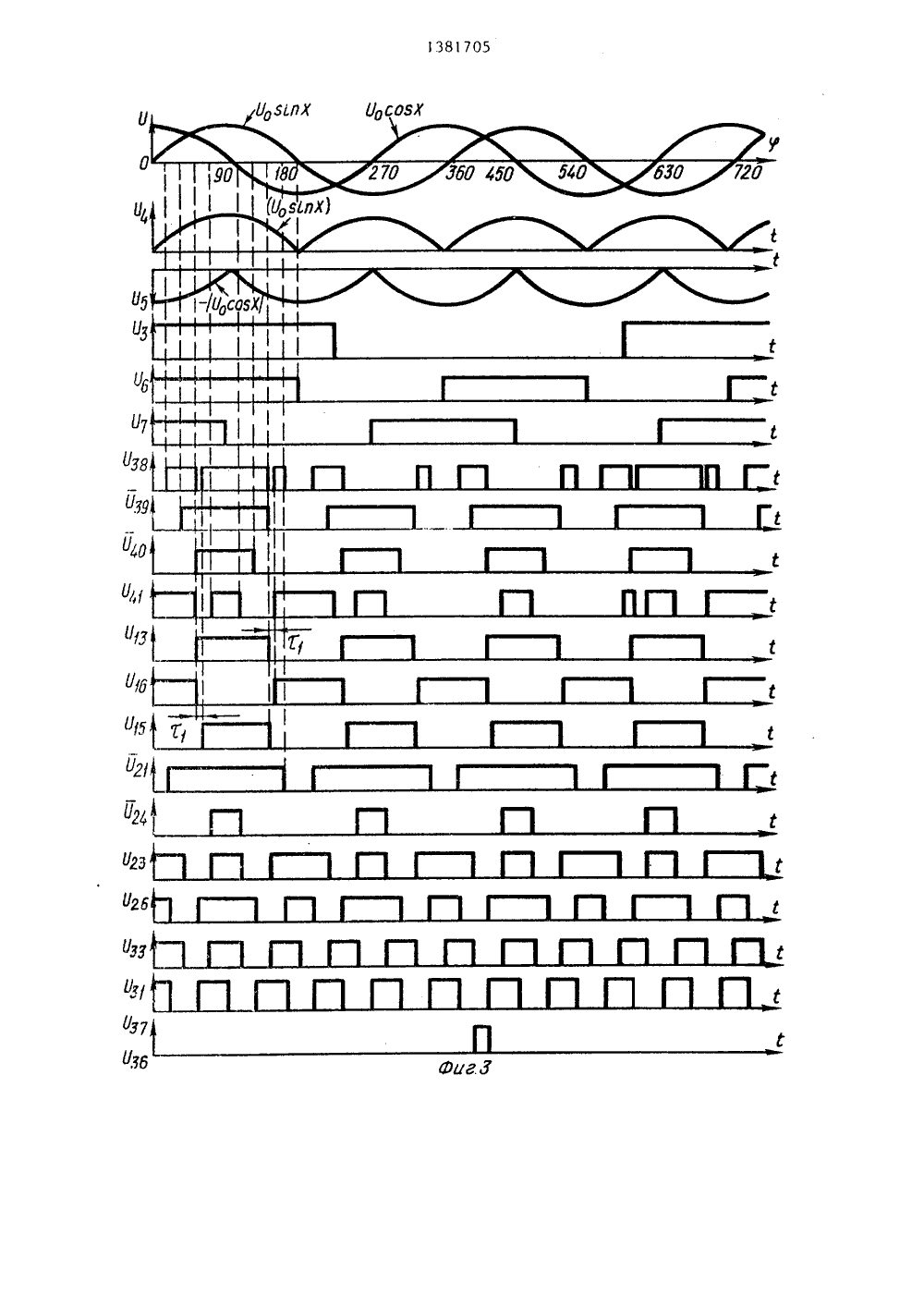

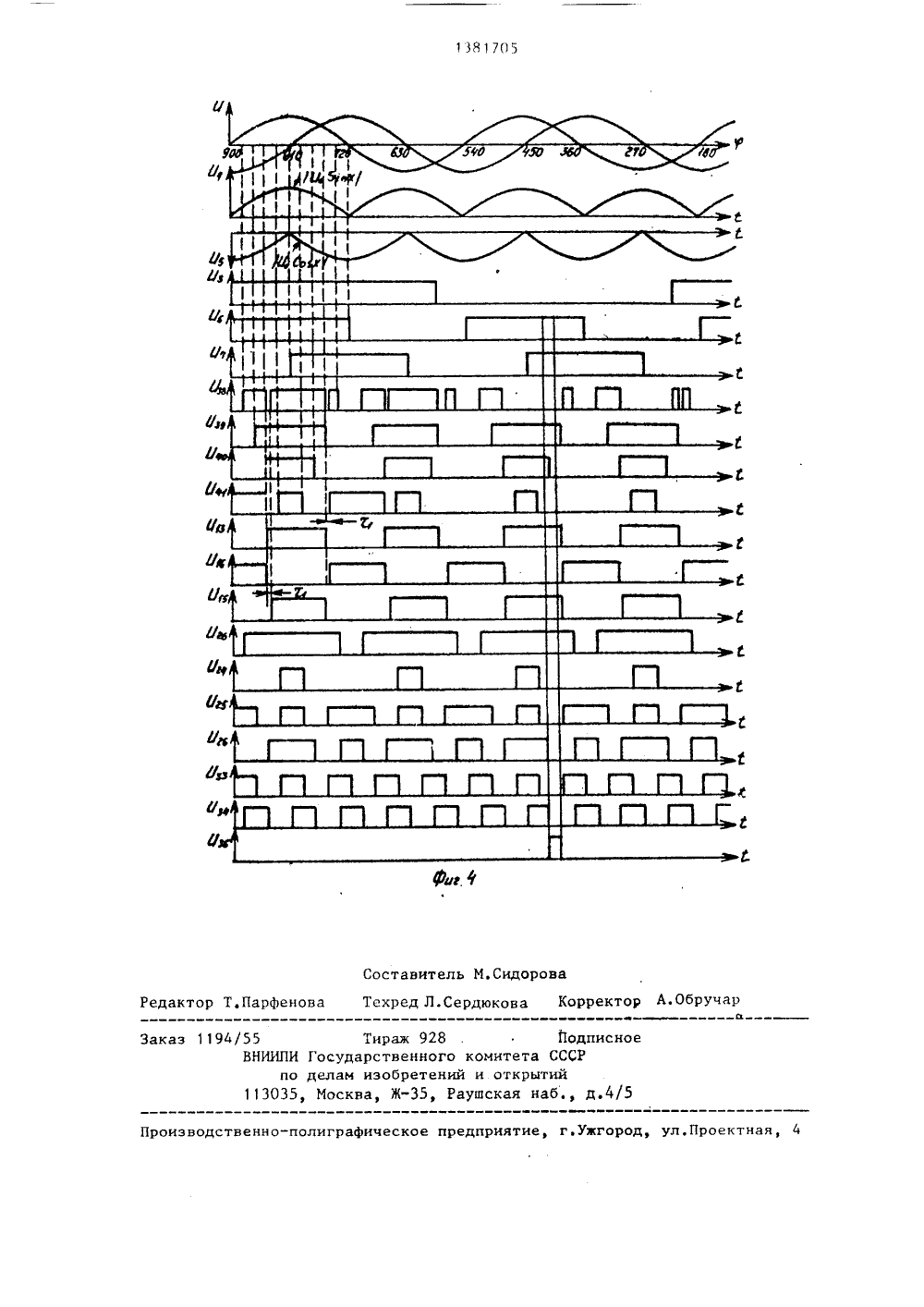

(54 НИХ ПРЕОБРАЗОВА ИГНАЛОВ В П ЬСОВ Изобретение и вычислите(21) (22) (46) (72) и В. (53) (56) сист с.95 ВЕННЫЙ КОМИТЕТ СССР ИЗОБРЕТЕНИЙ И ОТКРЫТ САНИЕ ИЗОБР ТОРСКОМУ СВИДЕТЕЛ 4044114/24-2427.03.8615.03.88. БюлА.И.Ярухин, Н.Дробьппевский681.325 (088.Дж.Вульвет, Дмах. М,: Энер96, рис. 44,торское свиде9310, кл. Н 0 Ь СИНУСНО-КОСИНУС- СЛЕДОВАТЕЛЬНОСТЬ относится к автомальной технике и моает быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. Сцелью повьппения достоверности путемформирования сигнала начала отсчетав преобразователь сииусно-косинусныхсигналов в последовательность импульсов, содерващий формирователи синусного и косинусного сигналов, выпрямители, компараторы, реэистивныйделитель напряаения, ключи, триггер,элемент И, блок управления, формирователь выходных импульсов, введены формирователь сигнала начала отсчета, элемент .задержки, элемент ИЛИ,блок синхронизации и блок компараторов. 3 з.п. ф-лы, 4 ил, 138170530 толя.Преобразователь работает следующим образам.1 а выходах формирователей 1 и 2 вырабатываются напряжения: 11 оз 1 п Х, - 45 (1 сиз Х(фиг,3 и 4), На вьиоде формирователь 3 вырабатывает импульс нуо ленога уровня в диапазоне 225-585 Камиаратары 6 и 7 срабатывают при нулевом уровне входных сигналов. Кампаратор 6 управляет ключевым выпрямителем 4, на выходе которого Формируетсч сигнал (11,зп Х), Выпрямитель 5 имеет идентйчную структуру и управляется инверсным выходным сигналом компаратора 7, На выходе выпрямителя 5 вырабатывается напряжение - 10 саз Х), Номиналы резисторов делителя 8 выбраны так, чтобы 11 зобретение относится к автоматике и вычислительной технике и можетбыть использовано для связи аналоговых источников информации с цифровымвычислительным устройством,5Целью изобретения является повышение достоверности преобразователяпутем формирования сигнала началаотсчета, что позволяет создатьквазиабсолютную систему отсчета.На фиг.1 и 2 представлена структурная схема преобразователя; нафиг,З и 4 - временные диаграммы егоработы при перемещении в прямом иобратном направлениях соответственно,Преобразователь содержит формирователи 1 и 2 соответственно синуснага и касинуснога сигналов и формирователь 3 сигнала начала отсчета,выпрямители 4 и 5, компараторы 6 ирезистивный делитель 8 напряжения,ключи 9 - 12, триггер 13, элемент14 задержки, элемент И 15, элементИЛ 11 6 блок 17 управления, формираватель 18 выходных импульсов,блок 19 синхронизации, блок 20 кампаратарав. Блок 17 управления содержит элемент И 21, элементы 22 и 23задержки, элементы ИЛИ 24 - 26,инвертары 27 и 28, Формирователь18 выходных импульсов содержит элементы И 29 - 32, элементы ИЛИ 33 и34, Блок 19 синхронизации содержитляпвходовые элементы И 35 и 36 иэлемент ИЛИ 37, Блок 20 содержиткомпаратары 38 - 41,11 1 и . 3 и 4 нумерация выходныхсигналил совпадает с номерами соотпеттнющих элементов преобразова переходы напряжения через нулевой уровень в общих точках резисторов происходили при фазе входного сигнала 11 здп Х 18, Зб, 54 и 72 . Фазы 0 и 90регистрируются кампараторами 6 и 7, а указанные четыре фазы определяются по срабатыванию компараторав 36 - 39. Компараторы выполняются с положительной обратной связью, поэтому сигналы поступают на их инвертирующие входы. Обозначим сигналы на выходах компараторов через А, В, С, Р, Е, 1, Напряжения с резистивного делителя 8 поступают непосредственно на компараторы 37 и 38, регистрирующие фазы 36 (144 ) и 54 (126 ). Компараторы 36 и 39 одновременно испохРьзуются и для формирования сигнала начала отсчета. Выходные сигналыи Ц формируются логическими элементами блока 17 управления и формирователя 18. Аналоговые ключи 9-12 подключают компараторы либо к формирователю 3, либо к выходам делителя 8, Возможны два направления движения к началу отсчета - движение справа (фиг.З) и движение слева (Фиг,4), В обоих случаях инверсным сигналом компаратора 37 сбрасывается триггер 13. При этом ключи 9 и 12 замыкаются, а ключи 10 и 11 размыкаются, Задержки управляющих сигналов, создаваемые элементами 14, 22 и 23, исключают одновременно замкнутое состояние в парах ключей 9, 11 и 10,12, обеспечивая развязку цепей сигнала начала отсчета и основных сигналов, Время задержкиэлемента 14 выбирается большим времени срабатывания аналогового ключа и сопутствующего переходного процесса, Величина задержкиэлементов 22 и 23 должна быть больше величины задержкиПереключение триггера 13 в единицу производится сигналом с прямого выхода компаратора 38, что приводит к обратному переключению ключей 9 12, Блок 17 управления совместно с Формирователем 18 формирует две последовательности импульсов перемещения 11, и 111,сдвиг па фазе которых относительно друг друга определяется направлением перемещения; В дальнейшем после обработки последовательности импульсов Ц, и 0можно формировать величину и знак перемещения, Блок 19 синхронизации формирует импульс начала отсчета, синхронизированный с импульсами последовательностей Б и Б Формула изобретения5 35 1. Преобразователь синусно-косинусных сигналов в последовательностьимпульсов, содержащий формировательсинусного сигнала, выход которогоподключен к входу первого компаратора и одному входу первого выпрямителя, другой вход которого соединенс прямым выходом первого компаратора,формирователь косинусного сигнала,выход которого подключен к входу второго компаратора и одному входу второго выпрямителя, другой вход которого соединен с инверсным выходом второго компаратора, выходы первого ивторого выпрямителей подключены квходам резистивного делителя напряжения, первый и второй выходы которого подключены к информационнымвходам первого и второго ключей,третий и четвертый ключи, триггер,элемент И, блок управления, прямыевыходы первого и второго компараторов и первый, второй, третий и четвертый выходы блока управления подключены к первому, второму, третьему, четвертому, пятому и шестомувходам соответственно формирователявыходных импульсов, первый и второйвыходы которого являются первым ивторым выходами преобразователя,о т л и ч а ю щ и й с я тем, что,целью повышения достоверности преобразователя, в него введены формирователь сигнала начала отсчета, блок40компараторов, элемент задержки,элемент ИЛИ-НЕ и блок синхронизации,выход формирователя сигнала началаотсчета подключен к информационнымвходам третьего и четвертого ключей, 45выход первого ключа соединен с выходом третьего ключа и подключен кпервому входу блока компараторов,выход второго ключа соединен с выходом четвертого ключа и подключенк второму входу блока компараторов,50остальные входы которого соединены.с остальными выходами резистивногоделителя напряжения, первый, второй;третий, четвертый прямые выходы ипервый инверсный выход блока компараторов подключены соответственнок первому, второму, третьему, четвертому и пятому входам блока управления, второй инверсный и четвертыйпрямой выходы блока компараторовподключены к соответствующим входамтриггера, один выходкоторого подключен к первым входам элемента Иэлемента ИЛИ-НЕ и входу элемента задержки, выход . элемента задержки подключен к вторым входам элемента И иэлемента ИЛИ-НЕ, выход элемента Иподключен к управляющим входам второго и третьего ключей, а выход элемента ИЛИ-НЕ подключен к управляющимвходам первого и четвертого ключей,инверсные выходы первого и второгокомпараторов, второй инверсный ичетвертый прямой выходы блока компараторов подключены соответственнок седьмому, восьмому, девятому идесятому входам формирователя выходных импульсов, прямые выходы первогои второго компараторов, первый, второй и четвертый прямые, второй инверсный выходы блока компараторови один и другой выходы триггера подключены к первому, второму, третьему, четвертому, пятому, шестому,седьмому и восьмому входам соответственно блока синхронизации, выходкоторого является третьим выходомпреобразователя,2. Преобразователь по п.1, о тл и ч а ю щ и й с я тем, что блокуправления содержит элемент И, дваинвертора, три элемента ИЛИ и дваэлемента задержки, первые входы элемента И, первого, второго элементов ИЛИ, вход первого элемента задержки, первый вход третьего элемента ИЛИ являются соответственнос первого по пятый. входами блокауправления, первый вход второго элемента ИЛИ через второй элемент задержки подключен к второму входуэлемента И, выход которого подключенк первому инвертору и к второму входу третьего элемента ИЛИ, выход первого элемента задержки подключен квторому входу первого элемента ИЛИ,выход которого через второй инверторподключен к второму входу второгоэлемента ИЛИ, выходы первого, второго и третьего элементов ИЛИ и выходпервого инвертора являются соответственно первым, вторым, третьим и четвертым выходами блока управления.3. Преобразователь по п,1, о тл и ч а ю щ и й с я тем, что формирователь выходных импульсов содержитчетыре элемента И и два элемента ИЛИ,входы первого элемента И являютсяпервым и четвертым входами формирователя, входы второго элемента И5являются шестым, восьмым и десятымвходами формирователя, входы третьего элемента И являются третьим, седьмым и девятым входами формирователя,входы четвертого элемента И являютсявторым и пятым входами формирователя, выходы первого и третьего элементов И подключены к входам первогоэлемента ИЛИ, выход которого является первым выходом формирователя, выходы второго и четвертого элементовИ подключены к входам первого элемента ИЛИ, выход которого являетсявторым выходом формирователя,4, Преобразователь по и. 1, о тл и ч а ю щ и й с я тем, что блок синхронизации содержит два пятивходовых элемента И и элемент ИЛИ, входы первого элемента И являются соответственно первым, вторым, третьим, пятым и седьмым входами блока синхронизации, первым и второй входы первого элемента И подключены соответственно к первому и второму входам второго элемента И, остальные входы которого являются соответственно четвертым, шестым и восьмым входами блока синхронизации, выходы первого и второго элементов И подключены к входам элемента ИЛИ, выход которого является выходом блока синхрони;зации.Составитель М.Сидоро Л.Сердюкова Корректор А.Обруч арфенова Те едак 5 Тираж 928 НИИПИ Государственного по делам изобретении 13035, Москва, Ж, Р

СмотретьЗаявка

4044114, 27.03.1986

ПРЕДПРИЯТИЕ ПЯ Г-4710

ЯРУХИН АЛЕКСАНДР ИВАНОВИЧ, СНИГИРЬ НИКОЛАЙ ИВАНОВИЧ, ДРОБЫШЕВСКИЙ ВЛАДИМИР ИВАНОВИЧ

МПК / Метки

МПК: H03M 1/30

Метки: импульсов, последовательность, сигналов, синусно-косинусных

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/7-1381705-preobrazovatel-sinusno-kosinusnykh-signalov-v-posledovatelnost-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь синусно-косинусных сигналов в последовательность импульсов</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Конвейерный аналого-цифровой преобразователь

Случайный патент: Двухпроводный кран управления тормозами прицепа