Микропрограммный модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

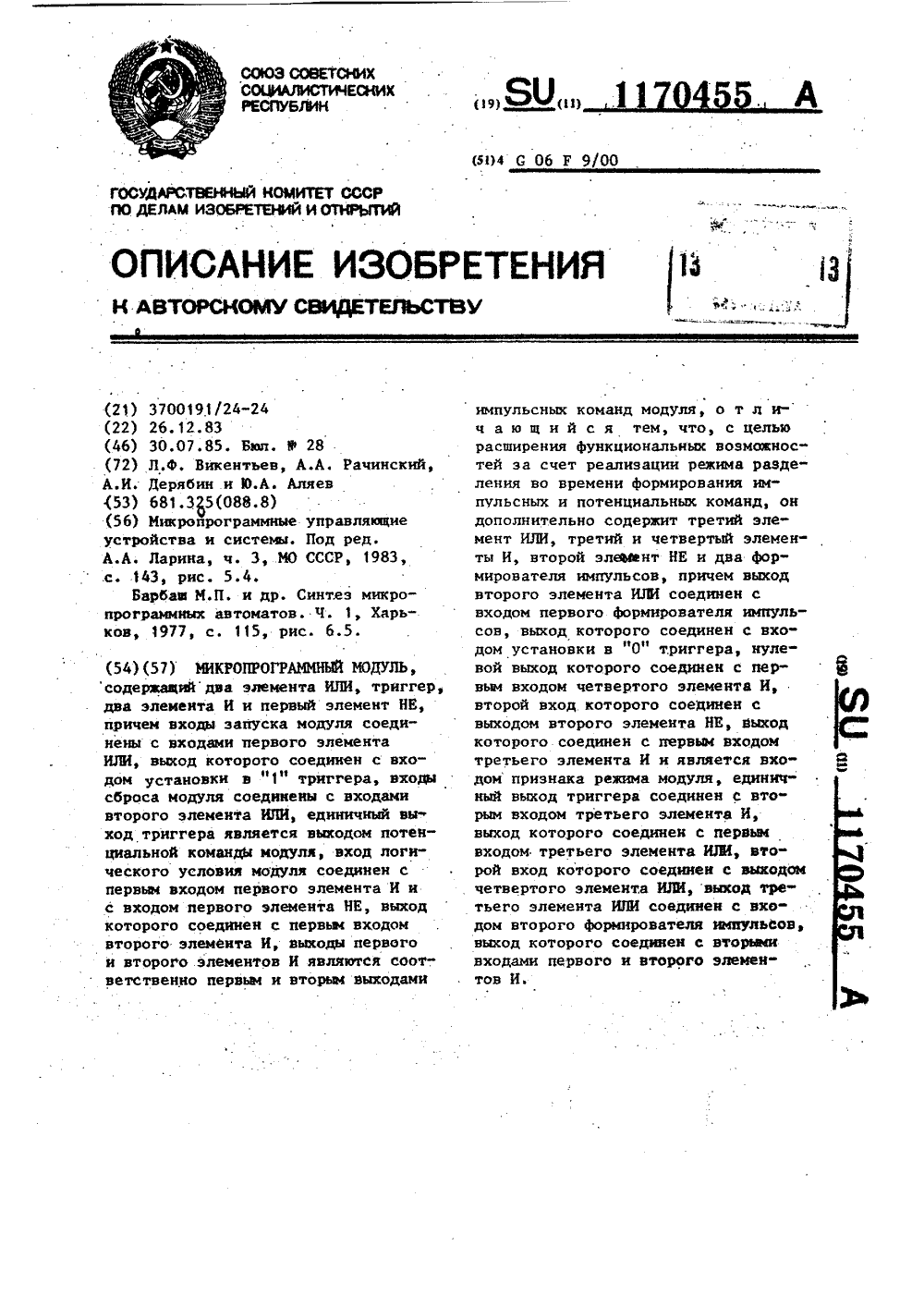

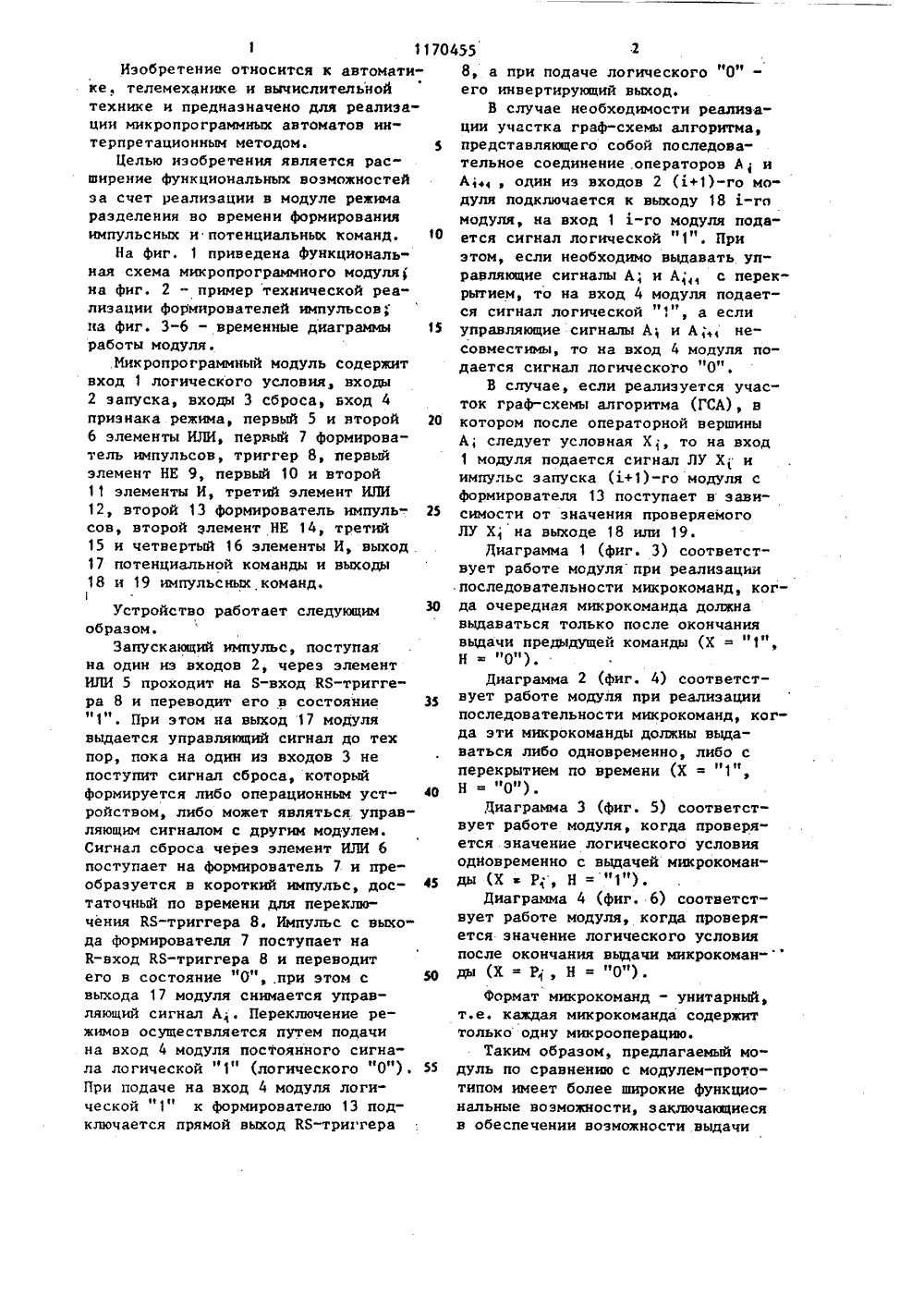

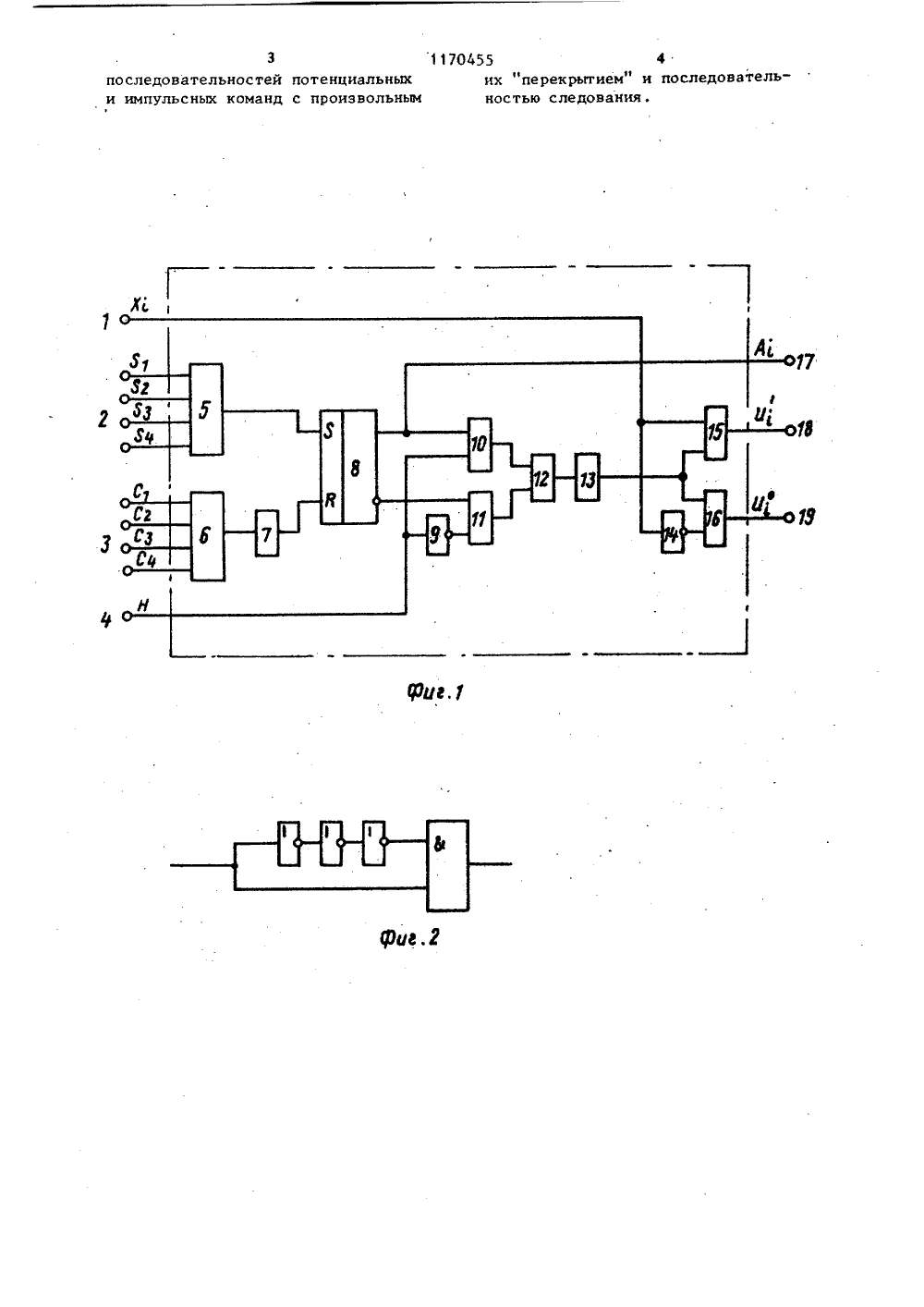

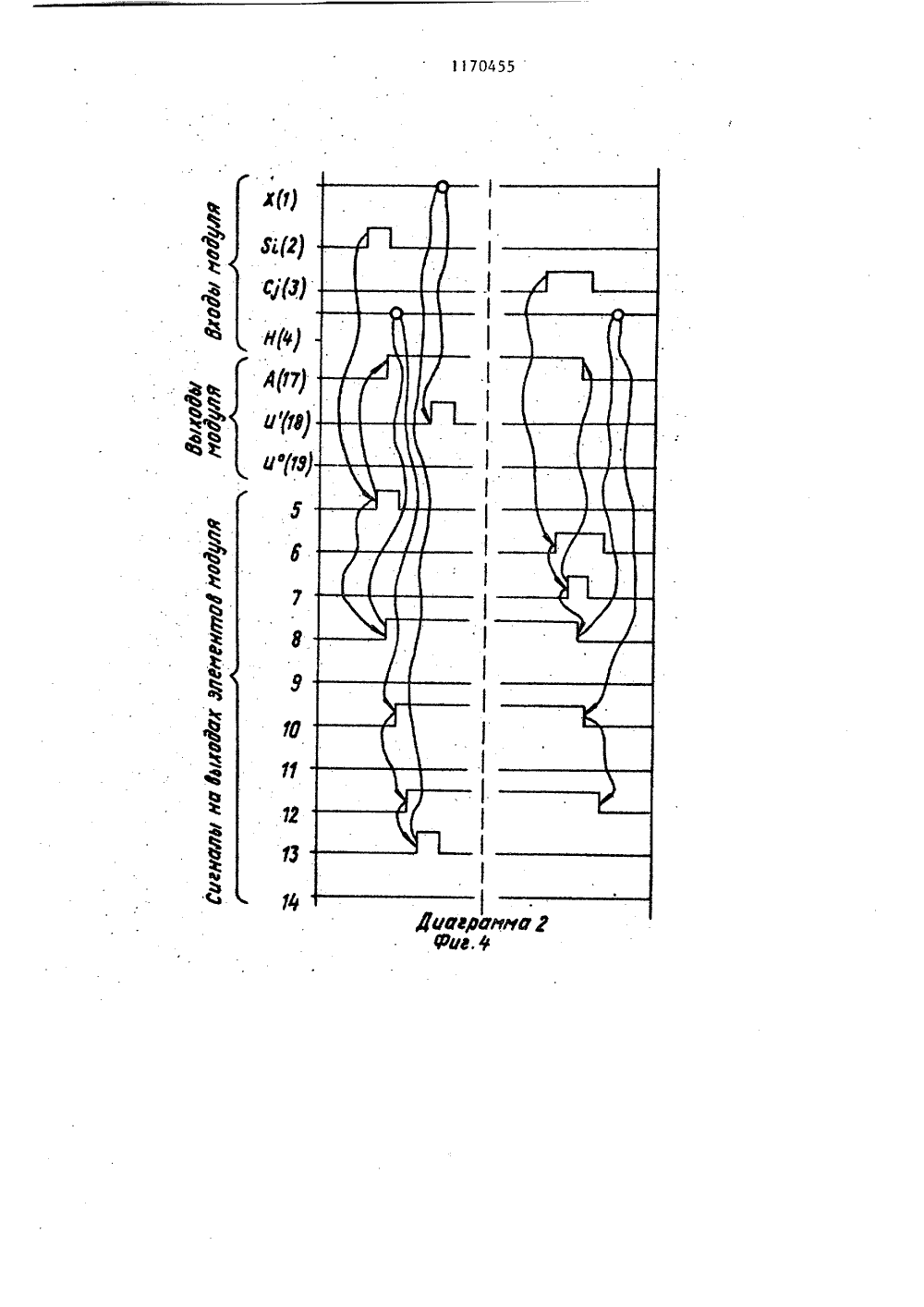

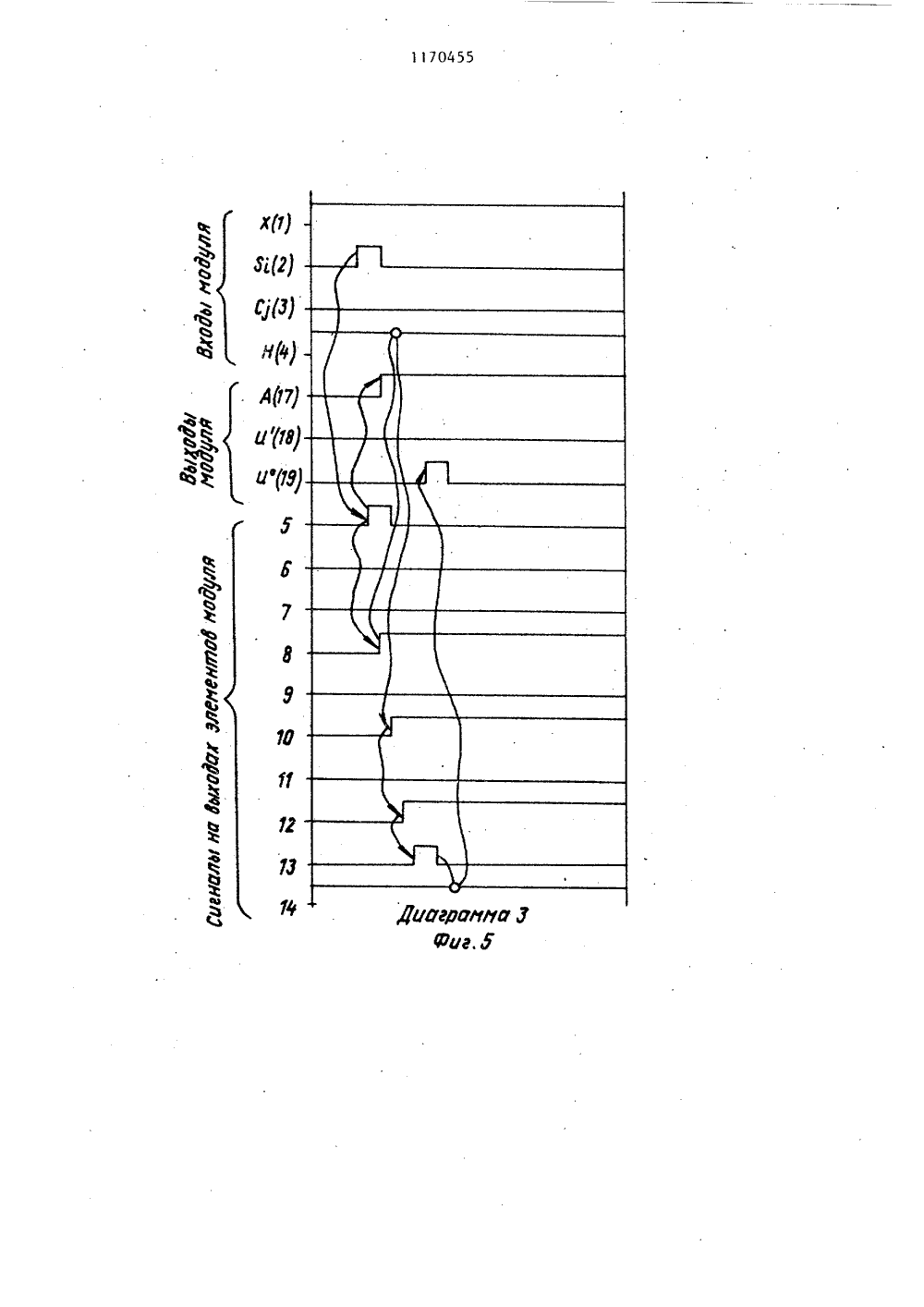

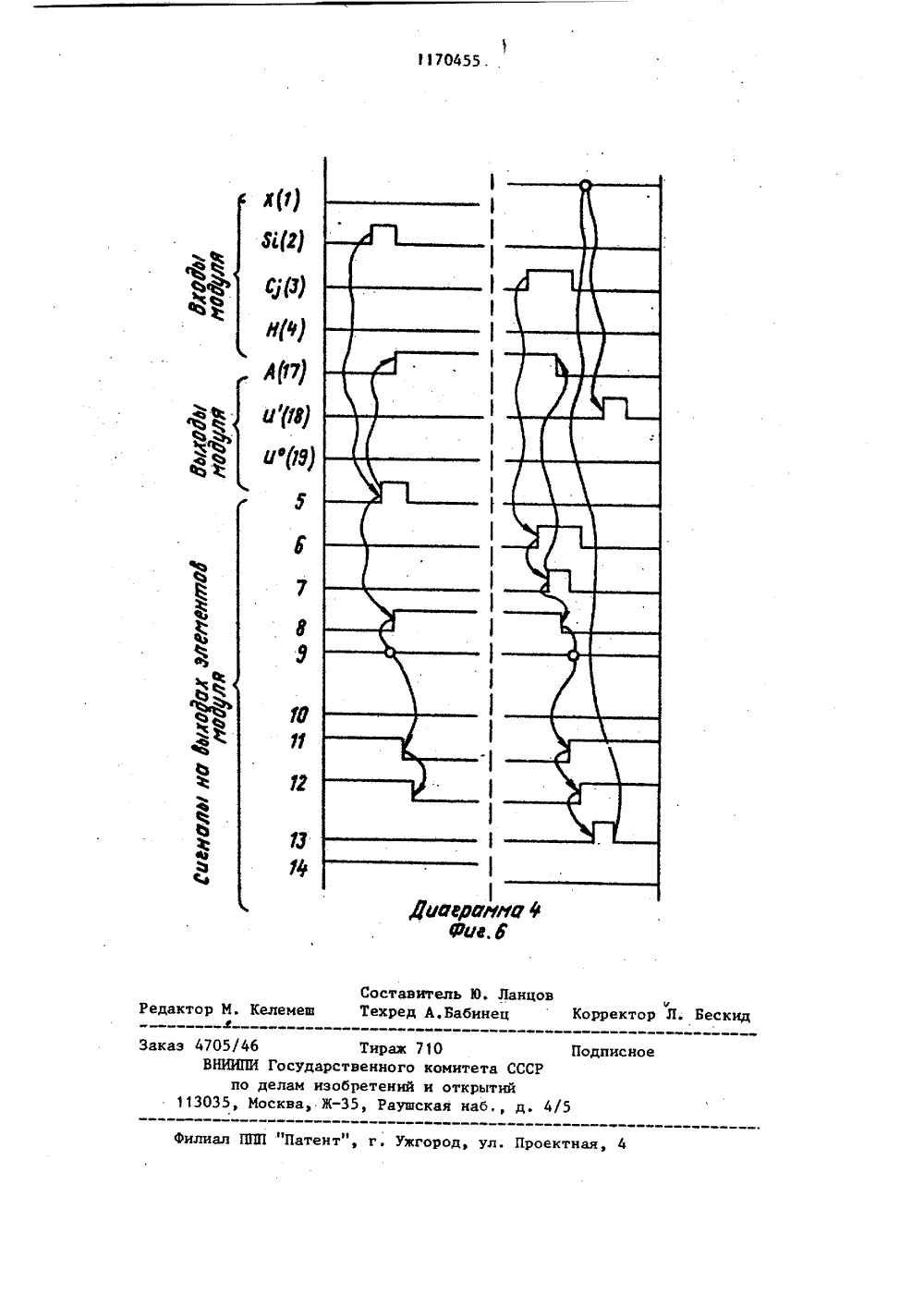

СОЮЗ СОЮЕТСНИХФИЦМРЕеваРЕСПУБЛИН 39) ( Ц 0 00 ГОСУДАРСТВЕННЫЙ ПО ДЕЛАМ ИЗОБАТЕ ОМИТЕТ СССР ТЕНИЙ И ОТКРЫТИЙНИЯ ОБРЕ ЬСТВУ ТОРСНОМУ СИИ кнй,ОПИСАНИ(56) Микропрограммные управляющие устройства и система. Под ред. А.А. Ларина, ч. 3, ИО СССР, 1983, .с, 143, рис. 5.4.Барбащ И.П. и др. Синтез микропрограммных автоматов. Ч. 1, Харьков, 1977, с. 115, рис. 6.5.(54) (57) ЮРОПРОУТАИИНЫЙ ЮДУЛ,содержащй два элемента ИЛИ, триггер,два элемента И и первый элемент НЕ,причем входы запуска модуля соединены с входами первого элементаИЛИ, выход которого соединен с входом установки в "1" триггера, входысброса модуля соединены с входамивторого элемента ИЛИ, единичный выход триггера является выходом потенциальной команд модуля, вход логического условия модуля соединен спервым входом первого элемента И ис входом первого элемента НЕ, выходкоторого соединен с первым входомвторого элемента И, выходы первогои второго элементов И являются соот".ветственно первым и вторьак выходами импульсных команд модуля, о т л и-ч а ю щ и й с я тем, что, с цельюрасширения функциональных возможностей за счет реализации режима разделения во времени формирования импульсных и потенциальных команд, ондополнительно содержит третий элемент ИЛИ, третий и четвертый элемен"ты И, второй элеМинт НЕ и два формирователя импульсов, причем выходвторого элемента ИЛИ соединен свходом первого формирователя импульсов, выход которого соединен с вхо"дом установки в "0" триггера, нулевой выход которого соединен с первым входом четвертого элемента И,второй вход которого соединен свыходом второго элемента НЕ, Выходкоторого соединен с первым входомтретьего элемента И и является входом признака режима модуля, единичный выход триггера соединен с вто"рым входом третьего элемента И,выход которого соединен с первымвходом третьего элемента ИЛИ, вто"рой вход которого соединен с выходомчетвертого элемента ЮЯ, выход третьего элемента ИЛИ соединен с входом второго формирователя импульсов,выход которого соединен с вторымивходами первого и второго элемен"тов И.170455 2 0 201Изобретение относится к автоматике, телемеханике и вычислительной технике и предназначено для реализа ции микропрограммных автоматов интерпретационным методом.Целью изобретения является расширение функциональных возможностей эа счет реализации в модуле режима разделения во времени формирования импульсных и потенциальных команд.На фиг, 1 приведена функциональная схема микропрограммного модуля 1 на фиг. 2 " пример технической реализации формирователей импульсов на фиг, 3-6 - временные диаграммы работы модуля.Микропрограммный модуль содержит вход 1 логического условия, входы 2 запуска, входы 3 сброса, вход 4 признака режима, первый 5 и второй 6 элементы ИЛИ, первый 7 формирователь импульсов, триггер 8, первый элемент НЕ 9, первый 10 и второй1 элементы И, третий элемент ИЛИ 12, второй 13 формирователь импуль". сов, второй элемент НЕ 14, третий 15 и четвертый 16 элементы И, выход .17 потенциальной команды и выходы 18 и 19 импульсных команд.Устройство работает следующим образом.Запускающий импульс, поступая на один из входов 2, через элемент ИЛИ 5 проходит на Б-вход КЗ-триггера 8 и переводит его в состояние 1. При этом на выход 17 модуля выдается управляющий сигнал до тех пор, пока на один из входов 3 не поступит сигнал сброса, который формируется либо операционным устройством, либо может являться управ" ляющим сигналом с другим модулем. Сигнал сброса через элемент ИЛИ б поступает на формирователь 7 и преобразуется в короткий импульс, достаточный по времени для переключения КЯ-триггера 8. Импульс с выхода формирователя 7 поступает на К-вход КБ-триггера 8 и переводит его в состояние "О", .при этом с выхода 17 модуля снимается управляющий сигнал А. Переключение режимов осуществляется путем подачи на вход 4 модуля постоянного сигнала логической "1 (логического О)При подаче на вход 4 модуля логической1 к формирователю 13 подключается прямой выход КБ-триггера 5 5 25 30 35 40 45 50 55 8, а при подаче логического О"- его инвертирующий выход.В случае необходимости реализации участка граф-схемы алгоритма, представляющего собой последовательное соединение .операторов А и А;+ один из входов 2 (+1)-го модуля подключается к выходу 8 1-го модуля, на вход 1 1-го модуля подается сигнал логической " 1. При этом, если необходимо выдавать управляющие сигналы А и А; с перек" рытием, то на вход 4 модуля подается сигнал логической ", а если управляющие сигналы А; и А; не" совместимы, то на вход 4 модуля подается сигнал логического О.В случае, если реализуется участок граф-схемы алгоритма (ГСА), в котором после операторной вершины А; следует условная Х;, то на вход 1 модуля подается сигнал ЛУ Х- и импульс запуска (+1)-го модуля с формирователя 13 поступает в зависимости от значения проверяемого ЛУ Х на выходе 18 или 19.Диаграмма 1 (фиг, 3) соответствует работе модуля при реализации последовательности микрокоманд, когда очередная микрокоманда должна выдаваться только после окончания выдачи предыдущей команды (Х = 1",ы О)Диаграмма 2 (фиг, 4) соответствует работе модуля при реализации последовательности микрокоманд, когда эти микрокоманды должны выдаваться либо одновременно, либо с перекрытием по времени (Х = "1", Н О)Диаграмма 3 (фиг. 5) соответствует работе модуля, когда проверяется значение логического условия одновременно с выдачей микрокоманды (Х Р Н = 1")Диаграмма 4 (фиг. 6) соответствует работе модуля, когда проверя" ется значение логического условия после окончания выдачи микрокоман- ды (Х Р Н = О).Формат микрокоманд - унитарный, т.е, каждая микрокоманда содержит только одну микрооперацию.Таким образом, предлагаемый мо" дуль по сравнению с модулем-прототипом имеет более широкие функциональные воэможности, заключающиеся в обеспечении возможности выдачипоследовательностей потенциальныхи импульсных команд с произвольным 1170455 4их "перекрытием" и последовательностью следования.170455 . иф(9 Составитель Ю, Ланцовтор М. Келемеш Техред А.Бабинец орректор Л. Беск 4705/46 Тираж 710 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Раушская наб., д, 4писное лиал ППП "Патент", г. Ужгород, ул. Проектная, 4 Мв Ф1 Диа юран Р.

СмотретьЗаявка

3700191, 26.12.1983

ПЕРМСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ

ВИКЕНТЬЕВ ЛЕОНИД ФЕДОРОВИЧ, РАЧИНСКИЙ АЛЕКСАНДР АЛЕКСЕЕВИЧ, ДЕРЯБИН АЛЕКСАНДР ИВАНОВИЧ, АЛЯЕВ ЮРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: микропрограммный, модуль

Опубликовано: 30.07.1985

Код ссылки

<a href="https://patents.su/7-1170455-mikroprogrammnyjj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный модуль</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Устройство программного управления

Случайный патент: Приспособление для забивания гвоздей в подошву