Устройство для вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

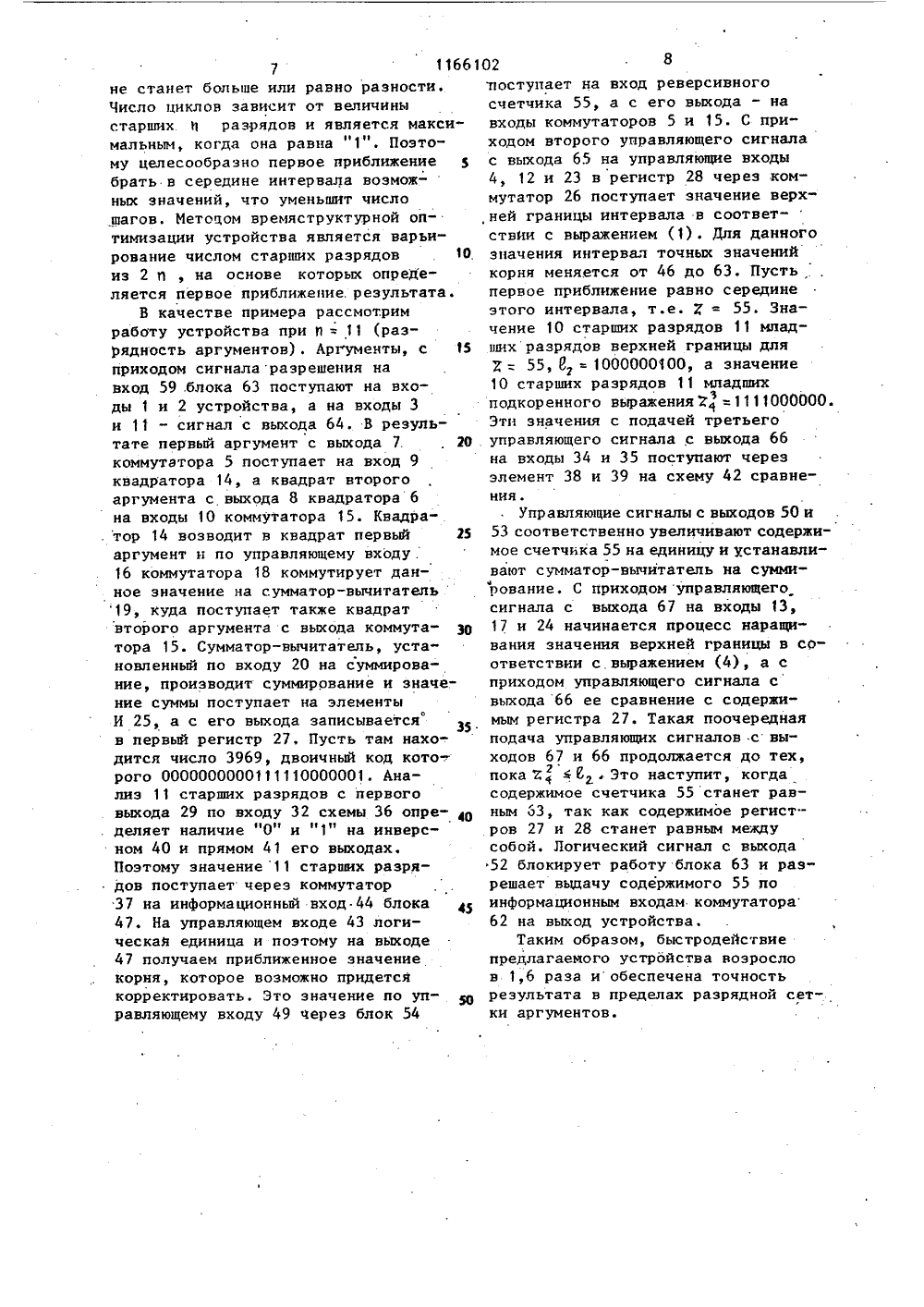

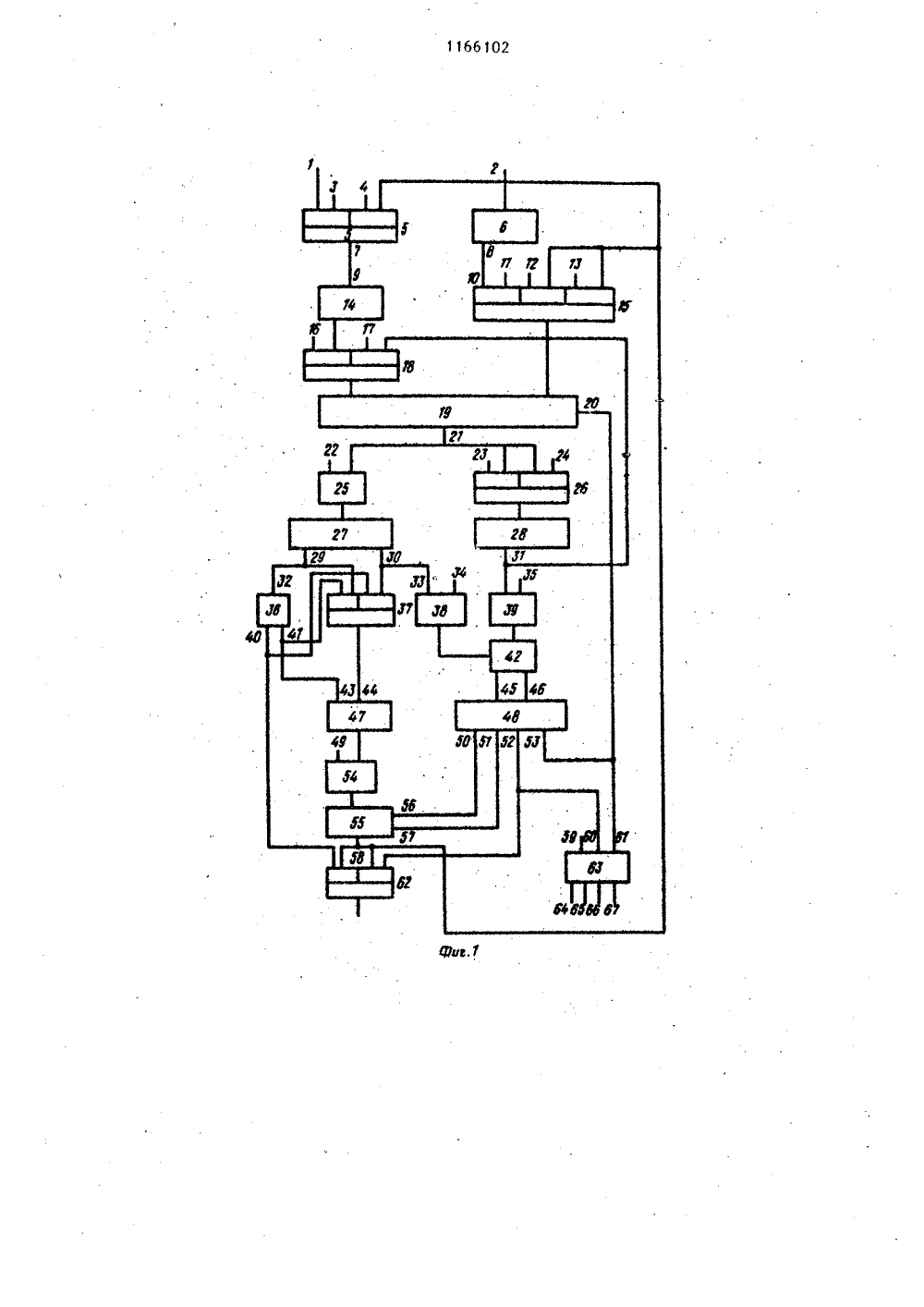

(5) С 06 Г 7/544 ОПИСАНИЕ ИЗОБРЕТЕК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ИЯ 3691362/24-2416.01.8407.07.85. Бюл. Ир 25А,В. Пархоменко, Л.Б.Макареня, В.Л. СмирноВитер и В.А. Мищенко681.325(088.8)(21) (22) (46) (72) гул(56) 1(к 622 У 94 (про 1. Авторское свидетель238, кл, 6 06 Г 7/20,Авторское свидетельст718, кл. 6 06 Р 7/552,отип). ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ(54)(57) 1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИИ ФУНКЦИИ К.4 ю ,ддддрдддд первый и второй коммутаторы, сумматор, первый регистр и схему сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия,в него введены с третьего по шестой коммутаторы, первый и второй квадраторы, второй регистр, с первой по четвертую группы элементов И, схема сравнения с нулем, блок извлечения квадратного корня, реверсивный счетчик, блок анализа и блок синхронизации, причем сумматор выполнен в виде сумматора-вычитателя, первые информационные входы первого и второго коммутаторов соединены соответственно с входом первого аргумента устройства и вьмодом первого квадратора, вход которого соединен с входом второго аргумента устройства, вход пуска которого подключен к входу пуска блока синхронизации, первый выход которого соединен с первыми управляющими . входами с первого по третий коммутаторов и первыми входами элементов И первой и второй групп, второй выход .блока синхронизации соединен с вторыми управляющими входами первого и второго коммутаторов и первым управляющим входом четвертого коммутатора, третий выход блока синхронизации соединен с первыми входами элементов И третьей и четвертой групп, четвертый выход блока синхронизации соединен с третьим управляющим входом второго коммутатора и вторыми управляющими входами третьего и четвертого коммутаторов, выход первого коммутатора через второй квадратор соединен с первым информационным входом третьего коммутатора, выход которого соединен с первым информационным входом сумматора-вычи-. тателя, выходы разрядов которого соединены с вторыми входами соответствующих элементов И первой группы и первым и вторым информационными входами четвертого коммутатора, выход которого соединен с информационным входом второго регистра, выходы разрядов которого соединены с вторым информационным вхрдом третьего коммутатора и вторыми входами соот-ветствующих элементов И третьей группы, вьмоды которых соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами элементов И четвертой группы, вторые входы эле- , юЬ ментов И которой соединены с выходами младших разрядов первого регистра и первым информационным входом пятого коммутатора, второй информационный вход которого соединен с вьмодами старших разрядов первого1166102 55 полнен в виде сумматора-вычитателя,первые информационные входы первогои второго коммутаторов соединенысоответственно с входом первого аргумента устройства и выходом первогоквадратора, вход которого соединенс входом второго аргумента устройства, вход фтуска которого подключенк входу пуска блока синхронизации,первый выход которого соединен спервыми управляющими входами с первого по третий коммутаторов и первыми входами элементов И первой и второй групп, второй выход блока синхронизации соединен с вторыми управляющими входами первого и второгокоммутаторов и первым управляющимвходом четвертого коммутатора, третий выход блока синхронизации соединен с первыми входами элементов Итретьей и четвертой групп, четвертыйвыход блока синхронизации соединенс третьим управляющим входом второгокоммутатора и вторыми управляющимивходами третьего и четвертого коммутаторов, выход первого коммутатора через второй квадратор соединенс первым информационным входомтретьего коммутатора, выход которого соединен с первым информационнымвходом сумматора-вычитателя, выходыразрядов которого соединены с вторы"ми входами соответствующих элементов И первой группы и первым и вторыминформационными входами четвертогокоммутатора, выход которого соединен с информационным входом второгорегистра, выходы разрядов которогосоединены с вторым информационнымвходом третьего коммутатора и вторыми входами соответствующих элемен" .тов И третьей группы, выходы которых соединены с первой группой входовсхемы сравнения, вторая группа входов которой соединена с выходамиэлементов И четвертой группы, вторыевходы соответствующих элементов И,которой соединены с выходами младших разрядов первого регистра и первым информационным входом пятогокоммутатора, второй информационныйвход которого соединен с выходами старших разрядов первого регистраи входом схемы сранения с нулем,прямой выход которой соединен спервым управляющим входом пятого ком.мутатора и управляющим входом блокаизвлечения квадратного корня, выходы 5 10 15 20 25 30 35 40 45 50 4разрядов которого соединены с вторыми входами соответствующих элементов. И второй группы, выходы которых соединены с информационным входом реверсивного счетчика, выход которого, соединен с первым и вторым информационными входами шестого коммутатора и вторым и третьим информационными входами второго коммутатора, выход которого соединен с вторым информа" ционным входом сумматора-вычитателя, инверснь 1 й выход схемы сравнения с нулем соединения с вторым управляющим входом пятого коммутатора н первым управляющим входом шестого коммутатора, выход которого является выходом устройства.Кроме того, блок анализа содержит триггер, два элемента задержки и с первого по пятый элементы И, прямой и инверсный выходы триггера соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с выходами соответственно первого и второго элементов задержки, инверсные выходы первого и второго элементов И соединены с первыми входами соответственно третьего и четвертого элементов И, первый и второй входы пятого элемента И соединены с прямыми выходами соответственно первого и второго элементов И, вход установки в "О" триггера соединен с инверсным выходом схемы сравнения, вторым входом четвертого элемента И и входом первого элемента задержки, вход установки в "1" триггера соединен с прямым выходом схемы сравнения, вторым входом третьего элемента И, входом второго элемента задержки, управляющим входом сумматоравычитателя и входом разрешения блока синхронизации, вход останова которого соединен с выходом пятого элемента И и вторым управляющим входом шестого коммутатора, выходы третьего и четвертого элементов И соединеьы с входами соответственно суммирования и вычитания реверсивного счетчика. На фиг. 1 дана блок-схема устйройства, на фиг. 2 - вариант конструкции блока анализа,Устройство содержит входы 1 и 2 аргумента, входы 3 и 4 управления коммутатора 5, квадратор 6, выходы 7 коммутатора и 8 квадратора, входы 9,и 39, выходы 40 и 41 схемы сравненияс нулем, схему 42 сравнения, входы43-46 блока 47 извлечения квадратного корня и блока 48 анализа, вход49. группы элементов И, выходы 50-53 15блокаанализа, группу элементовИ 54, реверсивный счетчик 55 с входами 56 и 57 и выходом 58, входыблока 59-61 синхронизации, коммутатор 62, блок 63 с выходами 64-67, . 20Блок анализа содержит триггер 68,элементы 69 и 70 задержки, элементы И 71-75. Выходы блока 63 синхронизации имеют следующую логикуподключения: 64-3, 11, 16, 22, 49, 2565-4, 12, 23, 66-34, 35; 67-13,17, 24.Работа устройства основана наследующем алгоритме. Пусть 2 л.Предлагается извлекать корень табличным путем только из и старшихразрядов подкоренного выраженияи затем при необходимости корректировать результат либо извлекатьтабличным путем корень из П младших разрядов, если старшие разрядыравны О.Коррекция разрядов основывается 40 на следующем: существует интервал Р, , Сг значений подкоренноговыражения, в пределах которого в силу ограничений (Д -разрядные значения аргументов), значение корня 45 является одним и тем же с точностью до младшего разряда аргументов и определяетсяа(1) 50г=" +Е гесли Е - приближенное значение корня из 11 старших разрядов подкоренного выражения и 2 -квадрат. этого 55 значения, то на основе выражений (1) возможно определить границыдостоверности Е и если исходное 02 бподкоренное значение находится вэтом интервалегО,=,.Ег,то процесс вычисления заканчивается,в противном случае существует связьмежду найденными границами неверного приближения Я 01, Е,1 и границамиточного результата сВ 1, Е г,17связь между границами определяется(д)преобразовывая выражения (2) и (3)учитывая, что все значения границсодержат одинаковые и старшихразрядов и их .численные значения мож-но рассматривать только в пределахй младших разрядов11е,." е,1 Е х;1=1,д ми К,п ма Е-2Анализ выражений (4) и (5) показывает, что можно оперировать только с ( 0 -1) старшими разрядами л младших разрядов значений границ, что позволит значительно сократить разрядность регистрового и дополни. тельного оборудования, если М.4 - подкоренное значение и Е 417 , найденного в соответствии с выражением (1), то на основании (4) начинается последовательный процесс суммирова" ння 3 г,со значением приближенногоувеличенного на единицу, причем в каждом цикле приближенное значение увеличивается на единицу,Точным значением корня будет последнее наращиваемое значение 7; когда сумма превысит или станет равной подкоренному значению; если4 с 7., И г,4 с 1 г то коррекциягрезультата отличается тем, что из01 происходит вычитаниЕ значенияуменьшенного на единицу, причем вкаждом цикле значение 7, уменьшается,на единицу до тех пор, пока с 4 )г7 11661 не станет больше или равно разности. Число циклон зависит от величины старших я разрядов и является максимальным, когда она равна "1". Поэто" му целесообразно первое приближение брать в середине интервала возможных значений, что уменьшит число шагов. Метоцом времяструктурной оптимизации устройства является варьирование числом старших разрядов 10, из 2 п , на основе которых определяется первое приближение. результата.В качестве примера рассмотрим работу устройства при П = 11 (разрядность аргументов). Аргументы, с 15 приходом сигнала разрешения на вход 59 .блока 63 поступают на входы 1 и 2 устройства, а на входы 3 и 11 - сигнал с выхода 64В результате первый аргумент с выхода 7. , 20 коммутатора 5 поступает на вход 9 квадратора 14, а квадрат второго аргумента с выхода 8 квадратора 6 на входы 10 коммутатора 15. Квадра.тор 14 возводит в квадрат первый 25 аргумент и по управляющему входу .16 коммутатора 18 коммутирует данное значение на сумматор-вычитатель 19, куда поступает также квадрат второго аргумента с выхода коммута- ЗО тора 15. Сумматор-вычитатель, установленный по входу 20 на суммирование, производит суммирование и значе." ние суммы поступает на элементы И 25, а с его выхода записывается в первый регистр 27, Пусть там находится число 3969, двоичный код кото-. рого 0000000000111110000001. Анализ 11 старших разрядов с первоговыхода 29 по входу 32 схемы 36 опре- о . деляет наличие "0" и "1" на инверсном 40 и прямом 41 его выходах. Поэтому значение 11 старших разрядов поступает через коммутатор37 на информационный вход 44 блока 47, На управляющем входе 43 логическая единица и поэтому на выходе 47 получаем приближенное значение корня, которое возможно придетсякорректировать. Это значение по управляющему входу 49 через блок 54 02 8поступает на вход реверсивного счетчика 55, а с его выхода - на входы коммутаторов 5 и 15. С приходом второго управляющего сигнала с выхода 65 на управляющие входы 4, 12 и 23 в регистр 28 через коммутатор 26 поступает значение верх,ней границы интервала в соответствии с выражением (1). Для данного значения интервал точных значений корня меняется от 46 до 63. Пусть ., первое приближение равно середине этого интервала, т.е. , = 55. Значение 10 старших разрядов 11 мпадших разрядов верхней границы для Х = 55, 0 = 1000000100, а значение 10 старших разрядов 11 младших подкоренного выражения 2 =1111000000. Эти значения с подачей третьего управляющего сигнала с выхода 66 на входы 34 и 35 поступают через элемент 38 и 39 на схему 42 сравнения.Управляющие сигналы с выходов 50 и 53 соответственно увеличивают содержимое счетчика 55 на единицу и устанавливают сумматор-вычитатель на суммирование. С приходом управляющего сигнала с выхода 67 на входы 13, 17 и 24 начинается процесс наращивания значения верхней границы в соответствии с.выражением (4), а с приходом управляющего сигнала с выхода 66 ее сравнение с содержимым регистра 27Такая поочередная подача управляющих сигналов с вы" ходов 67 и 66 продолжается до тех, пока Е йКЭто наступит, когда2содержимое счетчика 55 станет равным 63, так как содержимое регистров 27 и 28 станет равным между собой. Логический сигнал с выхода 52 блокирует работу блока 63 и разрешает выдачу содержимого 55 по информационным входам коммутатора 62 на выход устройства.Таким образом, быстродействие предлагаемого устройства возросло в 1,6 раза и обеспечена точность результата в пределах разрядной сетки аргументов."Патент", г. Ужгород Проектная, 4 Тираж 7 ВНИИПИ Госуд по делам и 113035, МоскПодписноственного комитета СССРбретений и открытийЖ, Раушская наб., д

СмотретьЗаявка

3691362, 16.01.1984

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПВО

ПАРХОМЕНКО АЛЕКСАНДР ВЛАДИМИРОВИЧ, АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, МАКАРЕНЯ СЕРГЕЙ НИКОЛАЕВИЧ, СМИРНОВ ВЯЧЕСЛАВ ЛЕОНИДОВИЧ, ВИТЕР ВЛАДИМИР ВАСИЛЬЕВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, функции

Опубликовано: 07.07.1985

Код ссылки

<a href="https://patents.su/7-1166102-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции</a>

Предыдущий патент: Устройство для вычисления сумм произведений

Следующий патент: Устройство для вычисления тригонометрических функций

Случайный патент: Колонковый снаряд