Процессор быстрого преобразования хартли-фурье вещественных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1594562

Авторы: Мельник, Яцимирский

Текст

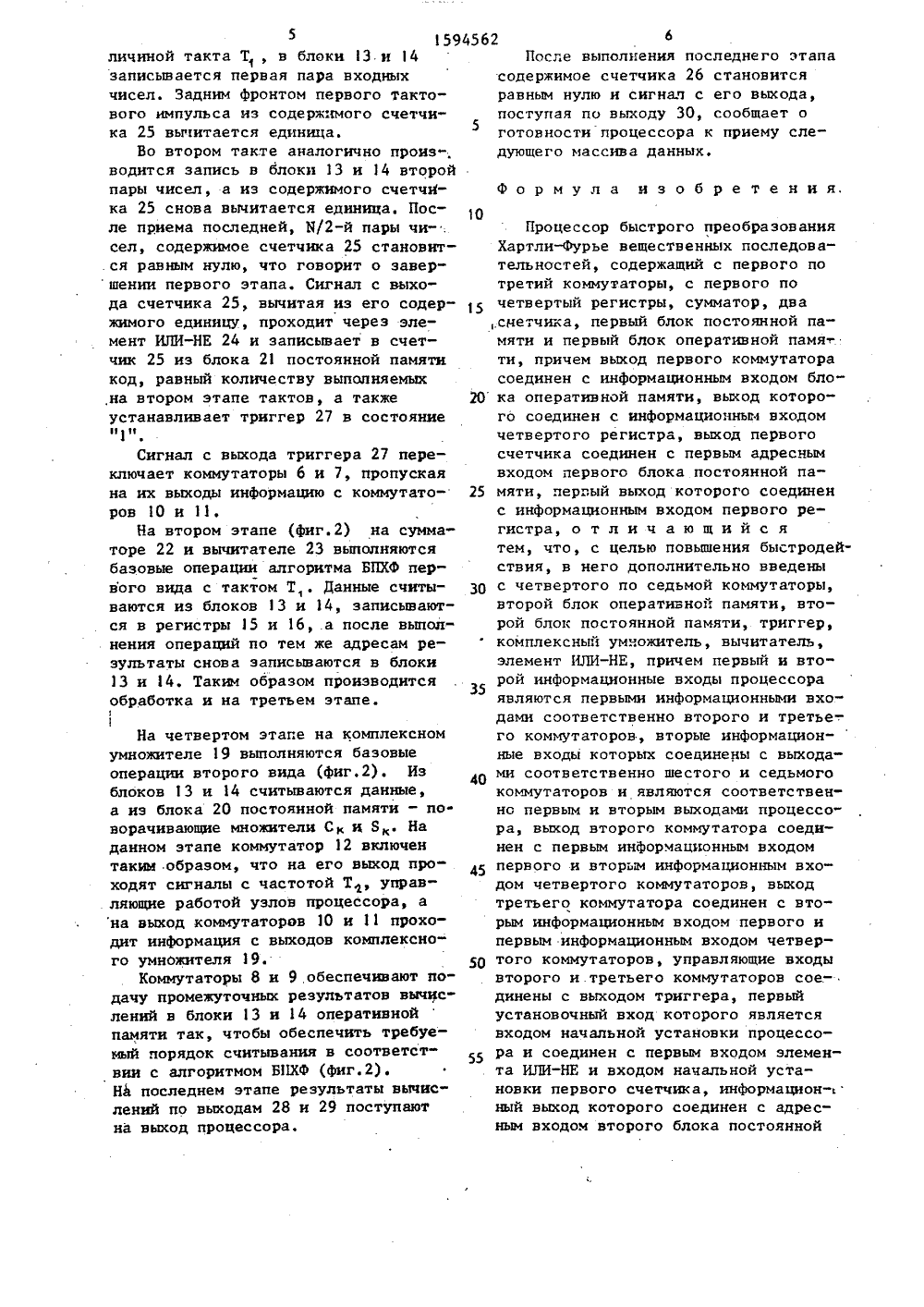

" (51)5 С 06 ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТПО ИЗОБРБЮНИЯМ И ОТНРЬГГИЯПРИ ГКЦ 7 СССР ОПИСАНИЕ ИЗОБРЕТЕН.ИЯ А ВТОРОКОЫУ СВИДЕТЕЛЬСТВУ 5Яцимирский льство СССР 15/332, 1982. ство СССР 15/332, 1986. О ПРНОБРАЗОВАСТВНННЫХ ПОСЛЕ(56) Авторское свидетУ 1078434, кл. 6 06 РАвторское свидетель1343424, кл. 0 06 Р4) ПРОЦЕССОР БЫСТРОНИЯ ХАРТЛИФУРЬН ВНП 1 НДОВАТНЛЬНОСТНЙ 2(57) Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработкисигналов. Цель изобретения - повьппе;ние быстродействия. Для этого процессор содержит коммутаторы 6-12, блоки13, 14 оперативной памяти, регистры15-18, комплексный умножитель 19,блоки 20, 21 постоянной памяти, сумматор 22., вычитатель 23, элементИЛИ-НН 24, счетчик 25, 26, триггер27, 2 нл,Изобретение относится к вычислитепьной технике и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - повьппение быст 5 родействия.На фиг.1 представлена схема процессора быстрого преобразования ХартлиФурье (БПХФ); на фиг.2 - граф алгорнтма: Хартли-Фурье вещественных последова ельностей.Процессор содержит информационные вх ды 1 и 2, вход 3 начальной уста- но ки, тактовые входы 4 и 5, коммутагоры 6-12, блоки 13 и 14 оперативной памяти, регистры 15-18, комплексный умножитель 19, блоки 20 и 21 постоянной памяти, сумматор 22, вычитатель 23, элемент ИЛИ-НЕ 24 счетчики 25 и 26, триггер 27, информационные вьходы 28 и 29 и выход 30 признака окончания обработки массива данных.Процессор выполняет алгоритм БПХФ в соответствии с графом (фиг.2) по 25 итерационному принципу. На каждой итерации выполняется одна базовая операция алгоритма БПХФ.Счетчик 25 служит для подсчета ко- личестна выполненных тактов.на одном этапе алгоритма БПХФ и работает в режйме вычитания. С каждым тактовым импульсом, поступающим с выхода коммутатора 12, из содержимого счечтика 25 вычитается единица.Счетчик 26 служит дпя подсчета количества выполненных этапов алгоритма БПХФ и работает в режиме вычитания. Как только содержимое счетчика 25 становится равным нулю, что говорит 4 об окончании выполнения этапа, сиг .-:, ныл с его выхода поступает на счетный вход счетчика 26 и вычитает из его содержимого единицу. 1 45В блоке 20 постоянной памяти запИсаны адреса, по которым производится считывание и запись операндов в 61 оки 13 и 14 оперативной памяти в кнждом такте при загрузке, выгрузке и на всех выполняемых этапах. В блоке 20 также записаны весовые коэффициенты алгоритма БПХФ-. Кроме того, в одном из разрядов блока 20 записаны кОды, управляющие коммутаторами 8 и 9, а,еще в одном разряде - коды, уйравляющие коммутатором 12, Адресом блока 20 служит содержимое счетчиков25 и 26. В блоке 21 постоянной памяти записано количество выполняемых тактов накаждом этапе алгоритма БПХФ.Базовая операция алгоритма БПХФ(фиг.2) может иметь один иэ двухвидов;А = А + В;В =А-ВилнА= АС+СЯ;В =АЯ - ВСя,где С = сов(2 йЫ/Н) 1Б= вхп(2 Г)1 с/Б).В первом случае для выполнениябазовой операции необходимо выполнитьоперации сложения и вычитания. Вовтором случае нужно выполнить операцию комплексного умножения.Так как время выполнения операцийсложения и вычитания существенноменьше времени выполнения операциикомплексного умножения, в процессорвведены коммутаторы 10 и 11, которыеобеспечивают выполнение базовой операции либо первого, либо второговидов.Тактовые импульсы с величинойтакта Т нли Тпоступают и процессор соответственно по входам 4 и 5.Процессор БПХФ работает следующиобразом.По входу 3 поступает сигнал начальнбй установки, который устанавливаеттриггер 27, в состояние "0", а в счетчике 26 устанавливается число, равное количеству выполняемых этаповалгоритма БПХФ. Задним фронтом сигнала начальной установки, который инвертируется элементом ИПИ-НЕ 24, в счетчик 25 иэ блока 21 записывается код,равный количеству тактов, выполняемыхна первом этапе алгоритма БПХФ(фиг.2)На первом этапе осуществляетсяприем входной информации по двум входам 1 и 2. Сигнал с выхода триггера27 на данном этапе пропускает на вы-,ходы коммутаторов 6 и 7 данные с входов 1 и 2, а сигнал с выхода блока20 постоянной памяти пропускаетчерез коммутаторы 8 и 9 информациюс выходов коммутаторов 6 и 7 навходы блоков 13 и 14 оперативной памяти. Данные записываются в блоки13 и 1 4 по адресам, поступающим изблока 20 постоянной памяти. По высокому потенциалу тактового импульса,поступающего из коммутатора 12 с ве-,;1594562 1 О 15 25 30 35 40 45 50 55 5личиной такта Т , в блоки 1 З.и 14 записывается первая пара входных чисел. Задним фронтом первого тактового импульса из содержимого счетчика 25 вычитается единица.Во втором такте аналогично произ", водится запись в блоки 13 и 14 второй пары чисел, а из содержимого счетчика 25 снова вычитается единица. После приема последней, Б/2-й пары чи- . сел, содержимое счетчика 25 становит.ся равным нулю, что говорит о завершении первого этапа. Сигнал с выхода счетчика 25, вычитая из его содержимого единицу, проходит через элемент ИЛИ-НЕ 24 и записывает в счетчик 25 из блока 21 постоянной памяти код, равный количеству выполняемых ,на втором этапе тактов, а также устанавливает триггер 27 в состояние Н 1 иСигнал с выхода триггера 27 переключает коммутаторы 6 и 7, пропуская на их выходы информацию с коммутаторов 10 и 11.На втором этапе (фиг.2) на сумматоре 22 и вычитателе 23 выполняются базовые операции алгоритма БПХФ первого вида с тактом Т,. Данные считываются из блоков 13 и 14, записываются в регистры 15 и 16, .а после выполнения операций по тем же адресам результаты снова записываются в блоки 13 и 14, Таким образом производится обработка и на третьем этапе.1На четвертом этаге на комплексномумножителе 19 выполняются базовыеоперации второго вида (фиг.2). Изблоков 13 и 14 считываются данные,а из блока 20 постоянной памяти - поворачивающие множители С и 8. Наданном этапе коммутатор 12 включентаким образом, что на его выход проходят сигналы с частотой Т, управляющие работой узлов процессора, ана выход коммутаторов 10 и 11 проходит информация с выходов комплексного умножителя 19.Коммутаторы 8 и 9 обеспечивают подачу промежуточных результатов вычислений в блоки 13 и 14 оперативнойпамяти так, чтобы обеспечить требуемый порядок считывания в соответствии с алгоритмом Б 11 ХФ (фиг.2).На последнем этапе результаты вычислений по выходам 28 и 29 поступаютна выход процессора,6После выполнения последнего этапа содержимое счетчика 26 становится равным нулю н сигнал с его выхода, поступая по выходу 30, сообщает о готовности процессора к приему следующего массива данных,Формула изобретения. Процессор быстрого преобразования Хартли-Фурье вещественных последов ательностей, содержащий с первого по третий коммутаторы, с первого по четвертый регистры, сумматор, два,снетчика, первый блок постоянной памяти и первый блок оперативной памятти, причем выход первого коммутаторасоединен с информационным входом блока оперативной памяти, выход которого соединен с информационньы входом четвертого регистра, выход первогосчетчика соединен с первым адреснымвходом первого блока постоянной памяти, первый выход которого соединенс информационным входом первого регистра, о т л и ч а ю щ и й с ятем, что, с целью повышения быстродействия, в него дополнительно введеныс четвертого по седьмой коммутаторы,второй блок оперативной памяти, второй блок постоянной памяти, триггер,комплексный умножитель, вычитатель,элемент ИЛИ-НЕ, причем первый и второй информационные входы процессораявляются первыми информационными входами соответственно второго и третье-.го коммутаторов, вторые информационные входы которых соецинены с выходами соответственно шестого и седьмогокоммутаторов н являются соответственно первым и вторым выходами процессора, выход второго коммутатора соединен с первым информационным входомпервого и вторым информационным входом четвертого коммутаторов, выходтретьего коммутатора соединен с вторым информационным входом первого ипервым информационным входом четвертого коммутаторов, управляющие входы второго и.третьего коммутаторов сое. -динены с выходом триггера, первыйустановочный вход которого являетсявходом начальной установки процессора и соединен с первым входом элемента ИЛИ-НЕ и входом начальной установки первого счетчика, информацнон-ный выход которого соединен с адресным входом второго блока постоянной1594562 О 3 11 Составитель Ю Техред М.Дид нцо орректор Т,Мале акто на Заказ 2831ВНИИПИ Государственного113035 Тираж 56 омитетаМосква, Ж Подписное изобретениям и открытия 5, Раушская наб., д. 4/5 ри ГКН тельский комбинат "Патент", г.ужгород, ул. Гагарина,10 венно роизв памяти, выход которого соединен синформационным входом второго счетчика, выход переноса которого соединенсо счетным входом первого счетчика,вторым входом элемента ИЛИ-НЕ и вторым установочным входом триггера,выхЬд пятого коммутатора соединен свходами записи-считывания первого ивторого блоков оперативной памяти,с тактовыми входами с первого по четвертый регистров н счетным входомвторого счетчика, вход начальной устанфвки которого соединен с выходомэлемента ИЖ"НЕ, первый и второй инфорыационные входы пятого коммутатора соединены соответственно с первыми вторым тактовыми входами процессора,управляющий вход пятого коммутатора соединен с управляющими входамишестого и седьмого коммутаторов ивторым вьгсодом первого блока постоянной памяти, второй адресный вход ко-.торого соединен с информационнымвыходом второго счетчика, третийвыход первого блока, постоянной памяти соединен с информационным входомвторого регистра, четвертый и пятыйвыходы первого блока постоянной памяти соединены с адресными входамисоответственно второго и первогоблоков оперативной памяти, шестойвыход первого блока постоянной памяти соединен с управляющими входамипервого и четвертого коммутаторов,выход четвертого коммутатора соединен с информационным входом второгоблока оперативной памяти, выход которого соединен с информационным"входом третьего регистра, выход которого соединен с первыми входамикомплексного умножителя, сумматораи вычитателя, вторые входы которыхсоединены с выходом четвертого регистра, выходы первого и второгорегистров соединены соответственнос третьим и четвертым входами комплек"сного умножителя, первый и второй вылходы которого соединены с первыми ин .формационными входами соответственношестого и седьмого коммутаторов, вто.- рые информационные входы которых сое- :5 динены соответственно с выходамисумматора и вычитателя, выход переноса первого счетчика является выходом признака окончаний обработки массива данных процессора.

СмотретьЗаявка

4471730, 27.06.1988

ПРЕДПРИЯТИЕ ПЯ В-8751

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ, ЯЦИМИРСКИЙ МИХАИЛ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, вещественных, последовательностей, преобразования, процессор, хартли-фурье

Опубликовано: 23.09.1990

Код ссылки

<a href="https://patents.su/4-1594562-processor-bystrogo-preobrazovaniya-khartli-fure-veshhestvennykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Процессор быстрого преобразования хартли-фурье вещественных последовательностей</a>

Предыдущий патент: Устройство для ортогонального преобразования цифровых сигналов по хаару

Следующий патент: Устройство ортогонального преобразования

Случайный патент: Устройство для обрезки излишков губы рантовойстельки