Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

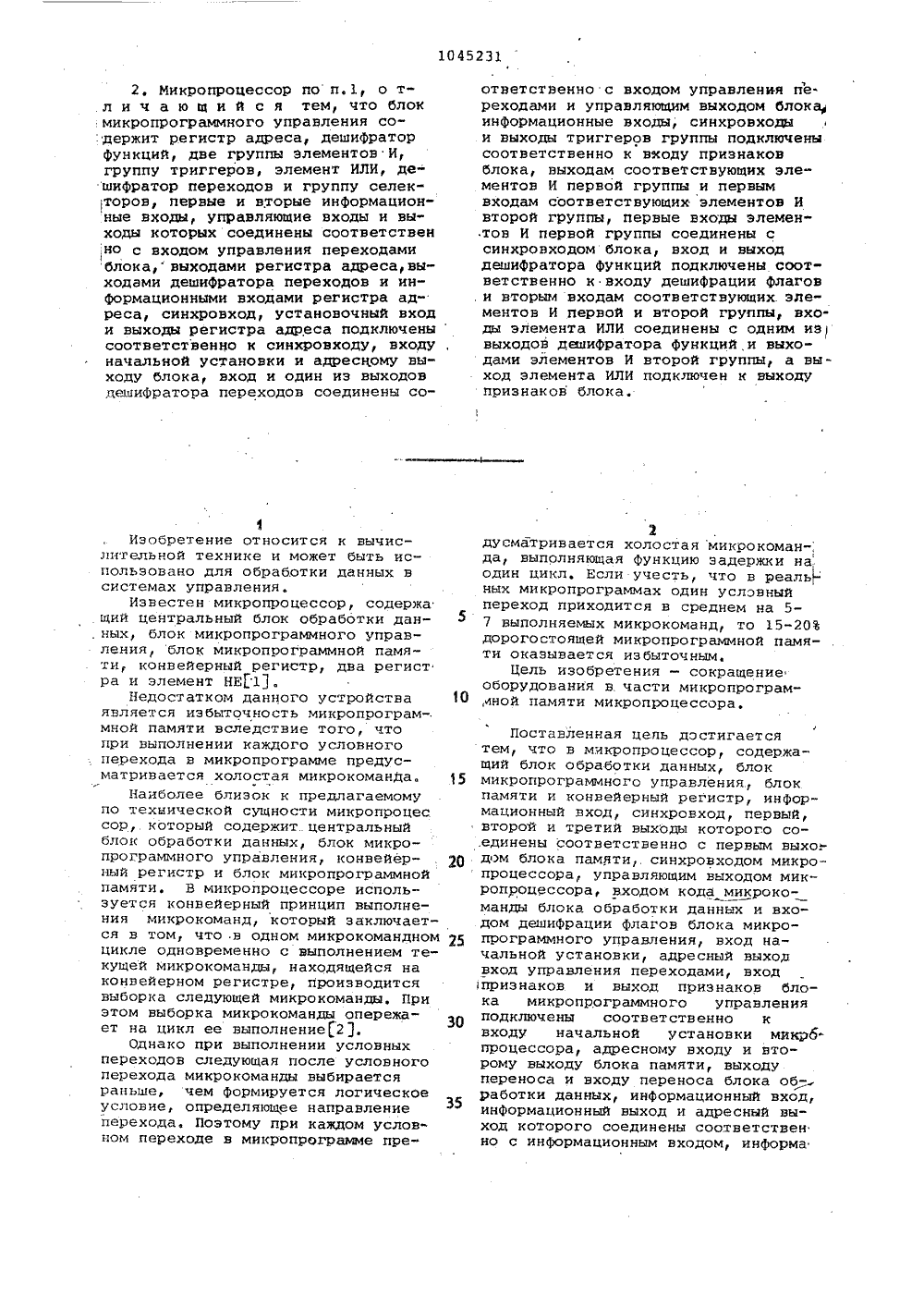

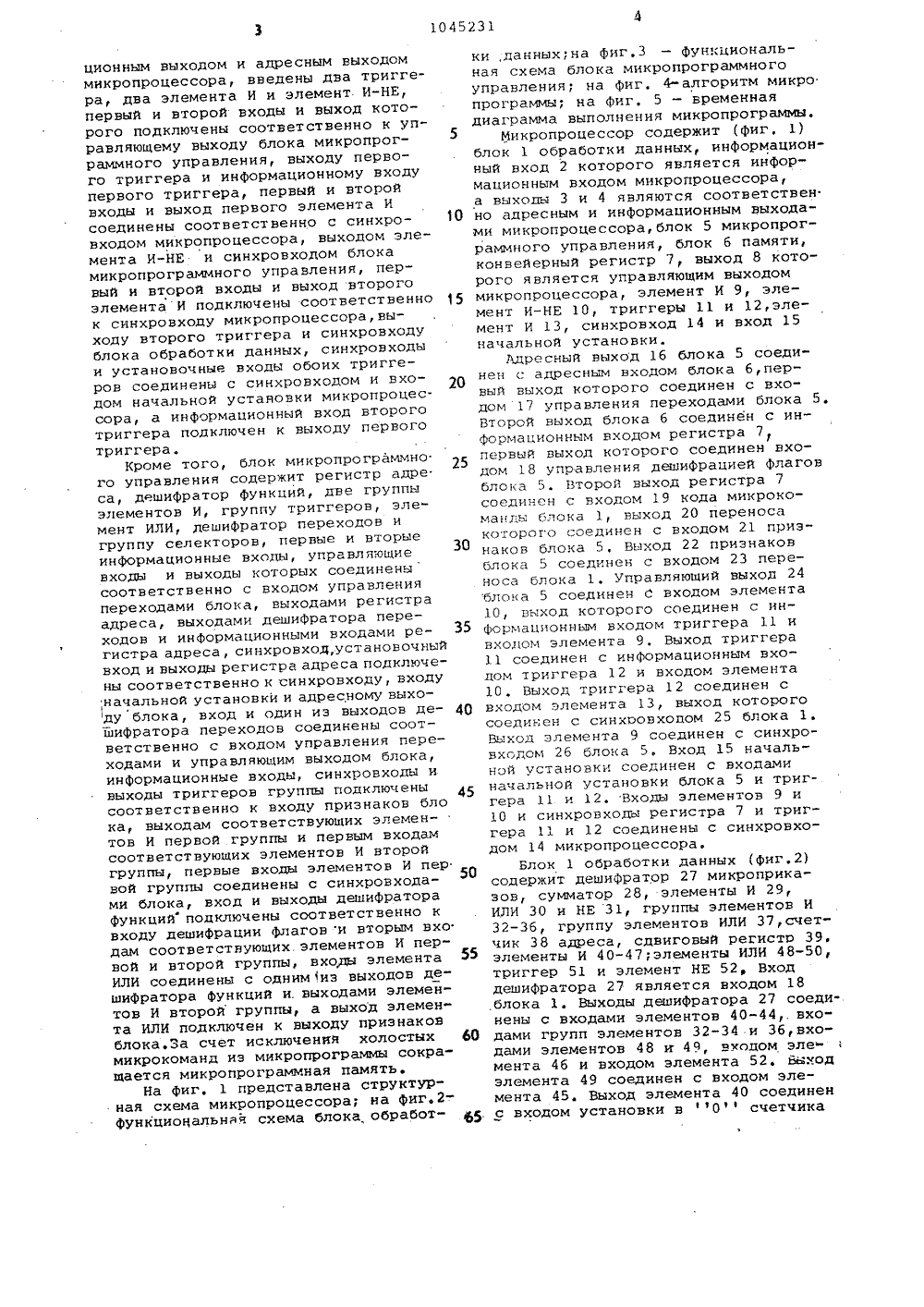

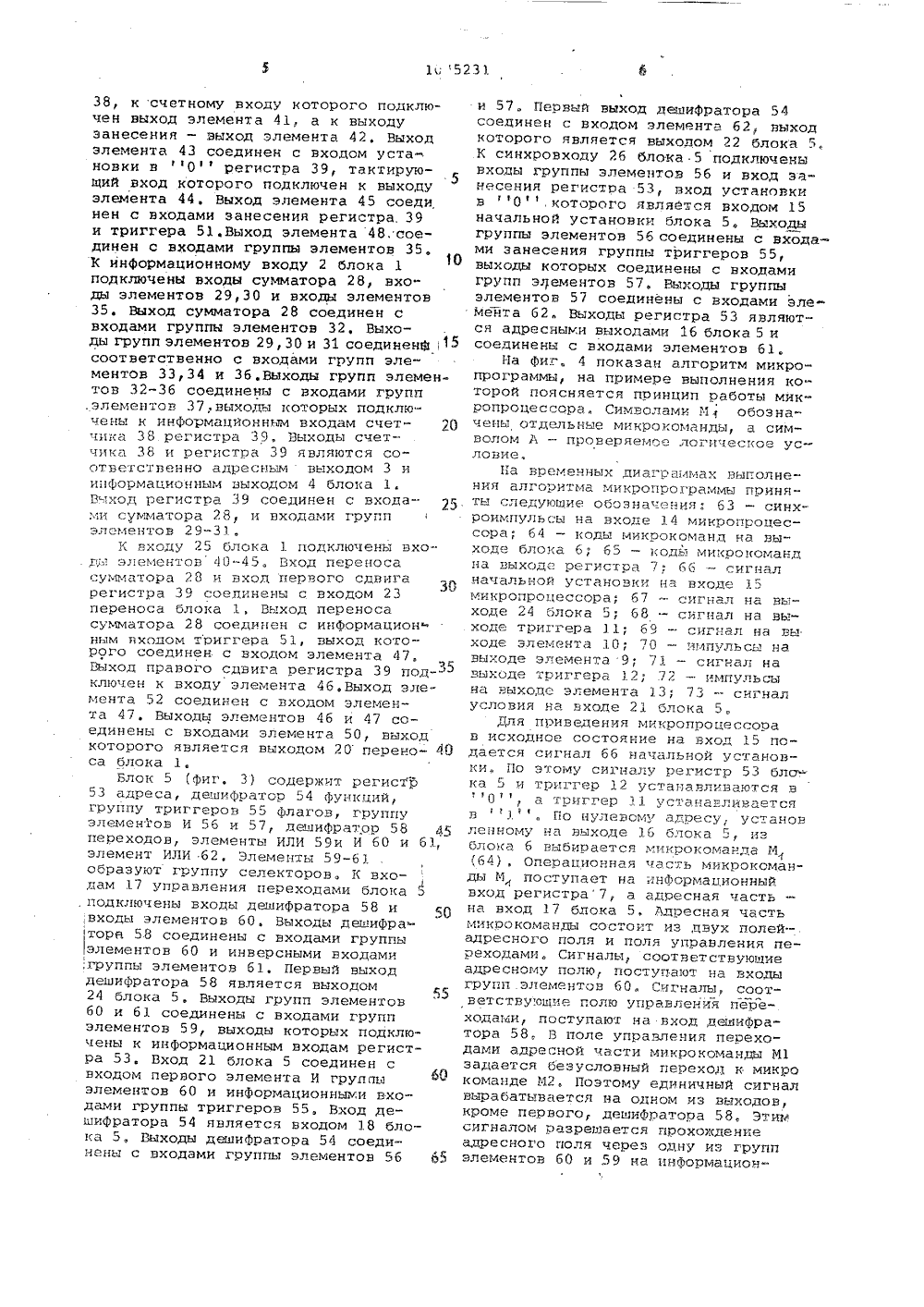

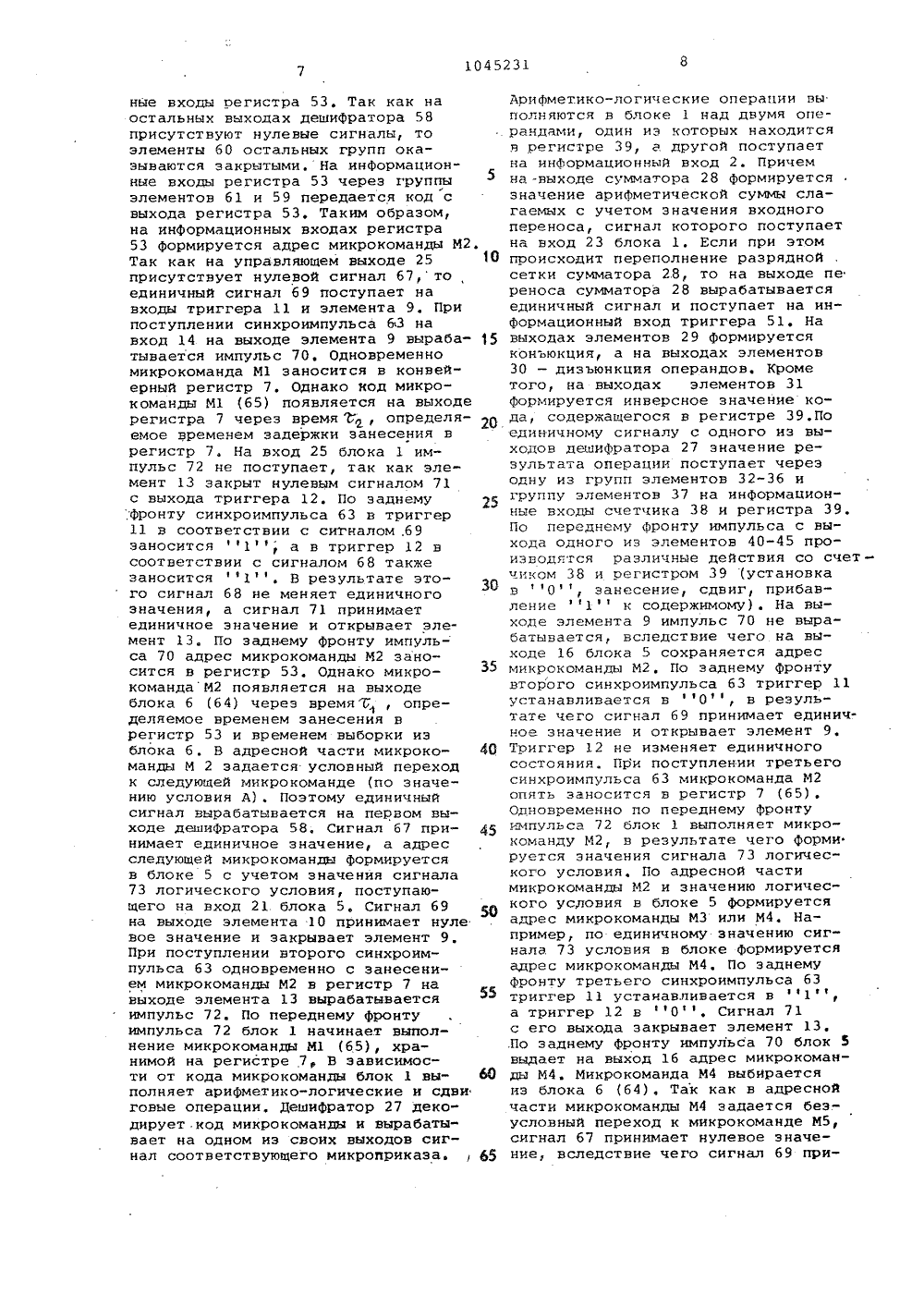

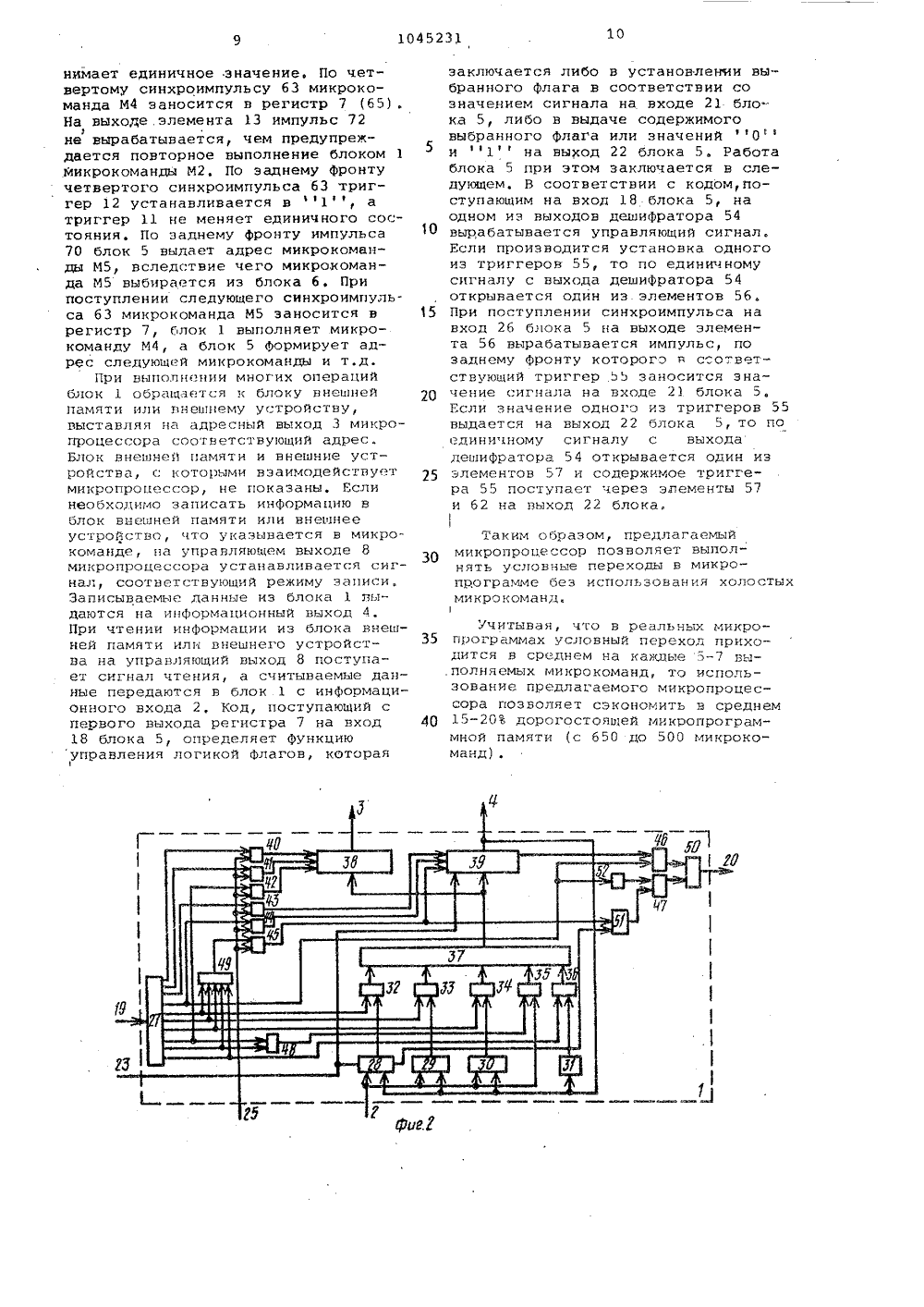

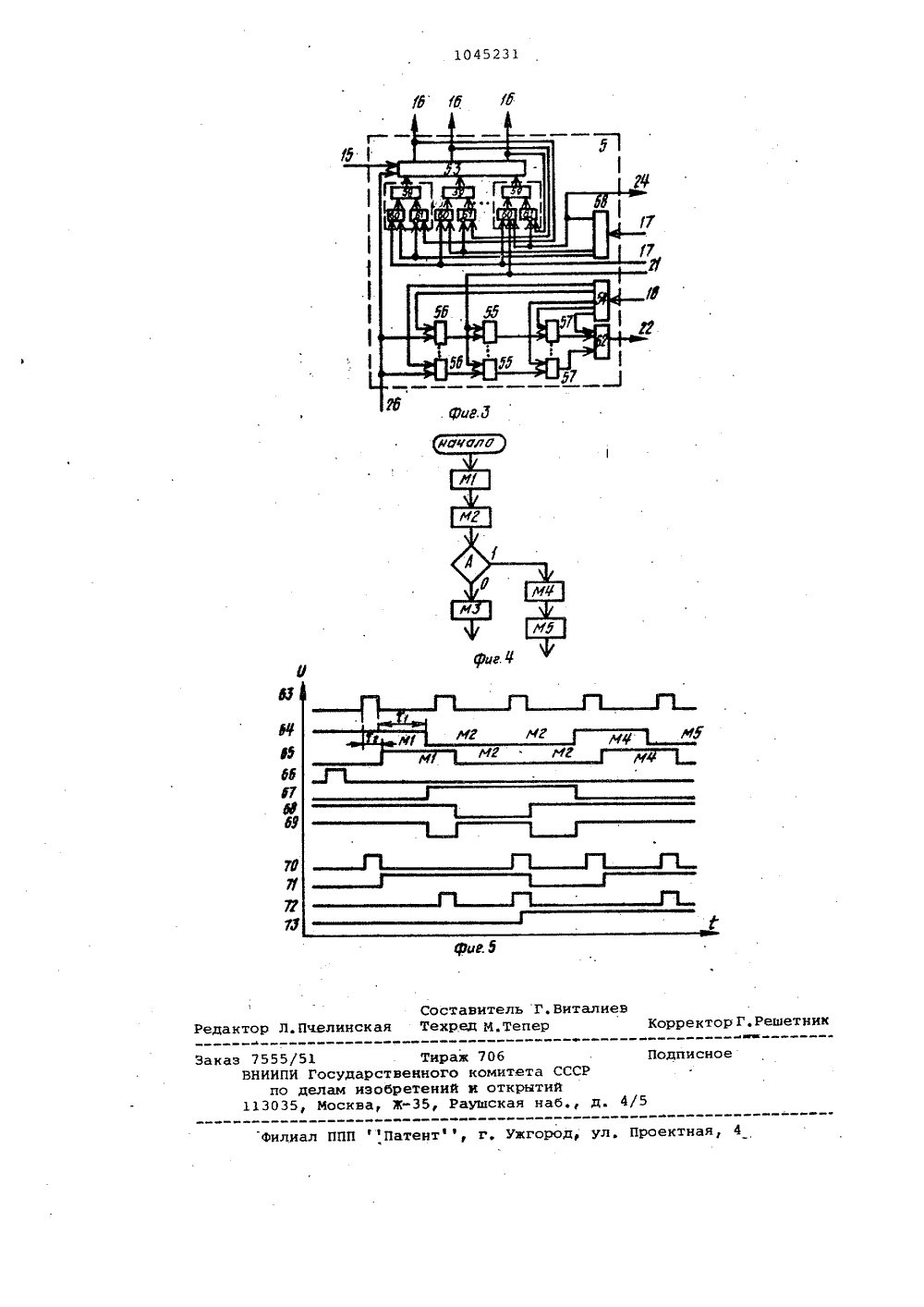

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 9) (11) 1(51) С 06 Р 15/О явч ПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ ЕТЕЛЬСТ еяч ч СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1 вАвторское свидетельство СССР )р 746532 кл, С 06 Р 15/00, 1980.2. Прангишвили И.В. Микропроцессоры и микро-ЭВМ, М фЭнергия, 1979, с. 91 (прототип) .(54)(57) 1.МИКРОПРОЦЕССОР, содержащий блок обработки данных, блок микропрограммного управления, блок памяти и конвейерный регистр, инфоряациояный вход, синхровход, первый, второй и третий выходы которого соединены с первым выходом блока памяти, синхровходом микропроцессора, управляющим выходом микропроцессора, входом кода микрокоманды блока обработки данных и входом дешифрации Флагов блока микропрограммного управ. ления, вход начальной установки, адресный выход, вход управления переходами, вход признаков и выходпризнаков блока микропрограммного управле"ния подключены соответственно к входу начальной установки микропроцессо-. ра, адресному входу и второму выходу блока памяти, выходу переноса и входу переноса блока обработки данных, информационный вход, информационный выход и адресный выход которого соединены соответственно с информационным входом, информационным выходом и адресным выходом микропроцессора, о т л и ч а ю щ и й с я тем, что, с целью сокращения оборудования, он содержит два триггера, два элемента И и элемент И-НЕ, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управле ния, выходу первого триггера и информационному входу первого триггера, первый и второй входы и выход первого элемента И соединены соот-ветственно с синхровходом микропроцессора, выходом элемента И-НЕ и синхровходом блока микропрограммного управления, перный и второй входы и выход второго элемента И подключены соответственно к синхровхо- Я ду микропроцессора, выходу второго триггера и синхровходу блока обра-ботки данных, сихровходы и установоч, ные входы обоих триггеров соединены (, с синхровходом и входом начальной установки микропроцессора, а информационный вход второго триггера подключен к выходу первого триггера.3 йЗО 2. Микропроцессор по п.1, о тл и ч а ю щ и й с я тем, что блок микропрограммного управления содержит регистр адреса, дешифратор функций, две группы элементов И, группу триггеров, элемент ИЛИ, дешифратор переходов и группу селекторон первые и вторые информацион/ные входы, управляющие входы и выходы которых соединены соответствен но с входом управления переходами блока, выходами регистра адреса,выходами дешифратора переходов и информационными входами регистра адреса, синхровход, устаноночный вход и выходы регистра адреса подключены соответственно к синхровходу, входу начальной установки и адресному выходу блока, вход и один иэ выходов дешифратора переходов соединены соИзобретение относится к вычислительной технике и может быть использовано для обработки данных н системах управления.Известен микропроцессор, содержа щий центральный блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти, конвейерный регистр, дна регист ра и элемент НЕ 1.Недостатком данного устройства является избыточность микропрограммной памяти вследствие того, что при ныполнении каждого условного перехода в микропрограмме предусматривается холостая микрокоманда.Наиболее близок к предлагаемому по технической сущности микропроцес сор,.который содержит. центральный блок обработки данных, блок микропрограммного управления, конвейерный регистр и блок микропрограммной памяти, В микропроцессоре используется конвейерный принцип выполнения микрокоманд, который заключается н том, что н одном микрокомандном цикле одновременно с выполнением текущей микрокоманды, находящейся на конвейерном регистре, проиэнодится выборка следующей микрокоманды, При этом выборка микрокоманды опережает на цикл ее выполнение 2 .Однако при выполнении условных переходов следующая после условного перехода микрокоманды выбираешься раньше, чем формируется логическое условие, определяющее направление перехода. Поэтому при каждом условном переходе в микропрограмме преответственно с входом управления пе.реходами и управляющим выходом блока информационные входы, синхровходыи выходы триггеров группы подключенысоответственно к входу признаковблока, ныходам соответствующих элементов И первой группы и первым входам соответствующих элементов Ивторой группы, первые входы элемен".тов И первой группы соединены ссинхровходом блока, вход и выходдешифратора функций подключены соотнетственно к входу дешифрации флагов , и вторым входам соответствующих элементов И перной и второй группы, входы элемента ИЛИ соединены с одним иэ) выходов дешифратора функций,и выходами элементов И второй группы, а выход элемента ИЛИ подключен к выходупризнаков блока2дусматринается холостая микрокоман-, да, выполняющая функцию задержки на один цикл. Если учесть, что н реаль ных микропрограммах один условный переход приходится н среднем на 5- 7 выполняемых микрокоманд, то 15-20 дорогостоящей микропрограммной памяти оказывается избыточным.Цель изобретения - сокращение оборудования в части микропрограм,мной памяти микропроцессора. Постанленная цепь достигается тем, что в микропроцессор, содержащий блок обработки данных, блок микропрограммного управления, блох памяти и конвейерный регистр, информационный вход, синхронход, первый, второй и третий выходы которого со.единены соответственно с первым ныхо. дом блока памяти,. синхронходом микропроцессора, управляющим выходом микропроцессора, входом кода микрокоманды блока обработки данных и входом дешифрации флагов блока микропрограммного управления, вход начальной установки, адресный выход вход управления переходами, вход признаков и выход признаков блока микропрограммного упранления подключены соответственно к входу начальной установки микрб. процессора, адресному входу и второму выходу блока памяти, выходу переноса и входу переноса блока обработки данных, информационный вход, информационный выход и адресный выход которого соединены соотнетстнен но с информационным входом, информационным выходом и адресным выходом микропроцессора, введены два триггера, два элемента И и элемент. И-НЕ, первый и второй входы и выход которого подключены соответственно к управляющему выходу блока микропрограммного управления, выходу первого триггера и информационному входу первого триггера, первый и второй входы и выход первого элемента И соединены соответственно с синхровходом микропроцессора, выходом элемента И-НЕ и синхровходом блока микропрограммного управления, первый и второй входы и выход второго элементаИ подключены соответственно к синхровходу микропроцессора,выходу второго триггера и синхровходу блока обработки данных, синхровходы и установочные входы обоих триггеров соединены с скнхровходом и входом начальной установки микропроцессора, а информационный вход второго триггера подключен к выходу первого триггера.Кроме того, блок микропрограммно. го управления содержит регистр адре са, дешифратор функций, две группы элементов И, группу триггеров, элемент ИЛИ, дешифратор переходов и группу селекторов, первые и вторые информационные входы, управляющке входы и выходы которых соединены соответственно с входом управления переходами блока, выходами регистра адреса, выходами дешифратора переходов и информационными входами регистра адреса, синхровход,установочный вход и выходы регистра адреса подключены соответственно к синхровходу, входу начальной установки и адресному выходу блока, вход и один из выходов дешифратора переходов соединены соответственно с входом управления переходами и управляющим выходом блока, информационные входы, синхровходы и выходы триггеров группы подключены соответственно к входу признаков бло ка, выходам соответствующих элементов И первой .группы и первым входам соответствующих элементов И второй группы, первые входы элементов И пер вой группы соединены с синхровходами блока, вход и выходы дешифратора функцийподключены соответственно к входу дешиФрации флагов и вторым вхо дам соответствующих. элементов И первой и второй группы, входы элемента ИЛИ соединены с одним азиз выходов дешиФратора функций и. выходами элементов И второй группы, а выход элемента ИЛИ подключен к выходу признаков блока.За счет исключения холостых мккрокоманд из микропрограммы сокращается микропрогрюжная память.На фиг, 1 представлена структурная схема микропроцессора; на фкг.2-. Функциональная схема блока обработ 510 ки,данных;на фиг,3 - функциональная схема блока микропрограммного управления; на фиг, 4-алгоритм микро программы; на Фиг. 5 - временная диаграмма выполнения микропрограммы,Микропроцессор содержит (фиг, 1) блок 1 обработки данных, информационный вход 2 которого является информационным входом микропроцессора, а выходы 3 и 4 являются соответствен но адресным и информационным выходамк микропроцессора, блок 5 микропрограммного управления, блок б памяти,конвейерный регистр 7, выход 8 которого является управляющим выходом15 микропроцессора, элемент И 9, элемент И-НЕ 10, триггеры 11 и 12,элемент И 13, синхровход 14 и вход 15начальной установкиАдресный выход 16 блока 5 соединен с адресным входом блока б,первый выход которого соединен с входом 17 управления переходами блока 5,Второй выход блока б соединен с информационным входом регистра 7первый выход которого соединен входом 18 управленкя дешиФрацией флаговблока 5. Второй выход регистра 7соединен с входом 19 кода микрокоманды блока 1, выход 20 переносакоторого соединен с входом 21 признаков блока 5, Выход 22 признаковблока 5 соединен с входом 23 переноса блока 1, Управляющий выход 24блока 5 соединен С входом элемента10, выход которого соединен с кн 35 Формационным входом триггера 11 ивходом элемента 9. Выход триггера11 соединен с инФормационным входом тркггера 12 к входом элемента10. Выход триггера 12 соединен с40 входом элемента 13, выход которогосоедккен с скнхровходом 25 блока 1,Выход элемента 9 соединен с синхровходом 26 блока 5, Вход 15 начальной установки соединен с входаминачальной установки блока 5 и триггера 11 к 12, Входы элементов 9 и10 к скнхровходы регистра 7 и триггера 11 и 12 соединены с синхровходом 14 микропроцессора,Блок 1 обработки данных (Фиг.2)содержит дешифратор 27 микроприказов, сумматор 28, элементы И 29,ИЛИ 30 и НЕ 31, группы элементов И32-36, группу элементов ИЛИ 37,счетчик 38 адреса, сдвиговый регистр 39,элементы И 40-47;элементы ИЛИ 48-50,триггер 51 и элемент НЕ 52Входдешифратора 27 является входом 18.блока 1. Выходы дешифратора 27 соединены с входами элементов 40-44,. вхо"60 дами групп элементов 32-34 и Зб,входами элементов 48 и 49, входом элемента 46 и входом элемента 52. Выходэлемента 49 соединен с входом элемента 45, Выход элемента 40 соединенс входом установки в 101 счетчика38, к счетному входу которого подключен выход элемента 41, а к выходузанесения - выход элемента 4. Выходэлемента 43 соединен с входом устанонки в 0 регистра 39, тактирующий вход которого подключен к выхоцуэлемента 44. Выход элемента 45 соединен с входами занесения регистра. 39и триггера 51.Выход элемента 48, соединен с входами группы элементов 35.( информационному входу 2 блока 1подключены входы сумматора 28, входы элементов 29,30 и входы элементов35. Выход сумматора 28 соединен свходами группы элементов 32, Выходы групп элементов 29, 30 и 31 соедкнен 9 5соответственно с входами групп элементов 33,34 и 36,Выходы групп элементов 32-36 соединены с нходами групп.элементов 37,ныхсды которых подключены к информационным входам счет- Очика 38 регистра 39, Выходы счетчика 38 и регистра 39 являются соответственно адресным выходом 3 кинФормационным ныходом 4 блока 1,В":".ход регистра 39 соединен с входа- д.к сумматора 28, и входами группэлементов 29-3),И входу 25 блока 1 подключены входы элементов 40 -45 Вход переносасумматора 28 к вход первого сдвигарегистра 39 соединены с входом 23переноса блока 1, Выход переносасумматора 28 соединен с информацион".ным яхслсм триггера 51, выход которого соединен с входом элемента 47,Выход правого сдвига регистра 39 под ключен к входу элемента 46.Выход элемента 52 соединен с входом элемента 47. Выходы элементов 46 и 47 соединены с входами элемента 50, выходкоторого является выходом 20 перено Оса блока 1,Блок 5 (Фкг. 3) содержит регистр53 адреса, дешифратср 54 функций,группу триггеров 55 флагов, группуэлементов И 56 к 57, дешифратор 58 45переходов, элементы ИЛИ 59 и И 60 и 61,элемент ИЛИ 62. Элементы 59-61образуют грУппУ селекторов. 1( нхсдам 17 управления переходами блока сподключены входы дешифратора 58 и,входы элементов 60, Выходы дешкфраторе 58 соединены с нходами группыэлементов 60 и инверсными нходамигруппы элементов 61. Первый выходдешкфратора 58 является выходом24 блока 5, Выходы групп элементов60 и 61 соединены с входами группэлементов 59, выходы которых подключены к информационным нходам регистра 53. Вход 21 блока 5 соединен свходом перного элемента И группы69элементов 60 и информационными входами группы триггеров 55, Вход дешиФратора 54 является входом 18 блока 5, Выходы дешкфратора 54 соединены с входами группы элементов 56 65 и 57 Первый выход дешкфратора 54 соединен с входом элемента 62, выход которого является выходом 22 блока 5, К синхровходу 26 блоха 5 подключены входы группы элементов 56 и вход занесения регистра 53, вход установки в 0,которого является входом 15 начальной установки блока 5. Выходы группы элементов 56 соединены с входами занесения группы триггеров 55,выходы которых соединены с входами групп э)ементов 57. Выходы группы элементов 57 соединены с входами элемента 62. Выходы регистра 53 являются адреснымк выходами 16 блока 5 и соединены с входами элементов 61,На Фиг. 4 показан алгоритм микропрограммы, на примере выполнения которой поясняется принцип работы мик" ропроцесссра, Симвсламк Иобозначены отдельные мккроксманды, а символом А в . проверяемое логическое ус- ЛОВИЕ.На временных диаграммах выполнения алгоритма микропрограммы пркняты следуюшке обозначения: 63 - синхрокмпульсы на входе 14 микропроцессора 64 - коды мккроксманд на выходе блока бу 65 - коды микрскоманд на выходе регкстра 7 у 66 - сигнал начальной установки на входе 15 микропроцессора 67 - сигнал на вь- ходе 24 блока 5; 68 - сигнал на вы" ходе триггера 11; 69 - сигнал на вы ходе элемента 10; 70 - импульсы на выходе элемента 9; 71 - сигнал на выходе триггера 12; 72 - импульсы на выходе элемента 13; 73 - сигнал условия на входе 21 блока 5Для приведения микропроцессора в исходное состояние на вход 15 подается сигнал бб начальной установки Пс этому сигналу регистр 53 блс ка 5 к триггер 12 устанавливаются н 0, а триггер ,1 устанавливается н , Пс нулевому адресу, устансн ленномУ на ныходе 16 блока 5, из блока 6 выбирается микрокоманде М (64). Операционная часть мнкроксманды М поступает на информационный вход регистра 7, а. адресная часть на нход 17 блока 5, Адресная часть мккрОксманды сОстОит кз двух ПОлей- адресного поля и поля управления переходами. Сигналы, состнетстнующке адресному полю, поступают на входы групп элементов 60. Сигналы, соответствующие голю упранленкя переходами, поступают на вход дешифратора 58,. В поле управления переходами адресной части микрокоманды И 1задается безуслонный переход к микрокоманде И 2. Поэтому едкнкчный сигналвырабатывается на одном из выходов,кроме первого, дешифратора 58, Этимсигналом разрешается прохождениеацреснсгс поля через одну из группэлементов 60 и 59 на информацион 104523151 О сетки сумматора 28, то на выходе переноса сумматора 28 вырабатываетсяединичный сигнал и поступает на инФормационный вход триггера 51. На 15 выходах элементов 29 формируетсяконъюкция, а на выходах элементов30 - дизъюнкция операндов. Крометого, на выходах элементов 31Формируется инверсное значение кода, содержащегося в регистре 39.Поединичному сигналу с одного из выходов дешифратора 27 значение результата операции поступает черезодну из групп элементов 32-36 игруппу элементов 37 на информационные нходы счетчика 38 и регистра 39.По переднему Фронту импульса с выхода одного из элементон 40-45 производятся различные действия со счетчиком 38 и регистром 39 (установкан 0, занесение, сдвиг, прибавление ф 1 к содержимому). На выходе элемента 9 импульс 70 не вырабатывается, вследствие чего на выходе 16 блока 5 сохраняется адрес 35 микрокоманды М 2, По заднему фронтувторого синхроимпульса 63 триггер 11устанавливается в 0, в результате чего сигнал 69 принимает единичное значение и открынает элемент 9, 4 О Триггер 12 не изменяет единичногосостояния. При поступлении третьегосинхроимпульса 63 микрокоманда М 2опять заносится н регистр 7 (65),ные входы оегистра 53, Так как на остальных выходах дешифратора 58 присутствуют нулевые сигналы, то элементы 60 остальных групп оказываются закрытыми. На информационные входы регистра 53 через группы элементов 61 и 59 передается код с выхода регистра 53, Таким образом, на информационных входах регистра 53 формируется адрес микрокоманды М 2 Так как на управляющем выходе 25 присутствует нулевой сигнал 67, то единичный сигнал 69 поступает на входы триггера 11 и элемента 9, При поступлении синхроимпульса 63 на вход 14 на выходе элемента 9 вырабатывается импульс 70. Одновременно микрокоманда М 1 заносится н конвейерный регистр 7. Однако код микро- команды М 1 (65) появляется на выходе регистра 7 через время, определяемое временем задержки занесения в регистр 7. На вход 25 блока 1 импульс 72 не поступает, так как элемент 13 закрыт нулевым сигналом 71 с выхода триггера 12, По заднему ;фронту синхроимпульса 63 в триггер 11 в соответствии с сигналом,б 9 заносится 1; а н триггер 12 в соответствии с сигналом 68 также заносится 1, В результате этого сигнал 68 не меняет единичного значения, а сигнал 71 принимает единичное значение и открывает элемент 13. По заднему фронту импульса 70 адрес микрокоманды М 2 заносится в регистр 53. Однако микро- командаМ 2 появляется на выходе блока б (64) через времяТ , определяемое временем занесенйя н регистр 53 и временем выборки из блока б. В адресной части микрокоманды М 2 задается услонный переход к следующей микрокоманде (по значению условия А). ПоэтомУ единичный сигнал вырабатывается на первом выходе дешифратора 58. Сигнал 67 принимает единичное значение, а адрес следующей микрокоманды формируется в блоке 5 с учетом значения сигнала 73 логического условия, поступающего на вход 21 блока 5. Сигнал 69 на выходе элемента 10 принимает нуле вое значение и закрывает элемент 9, При поступлении второго синхроимпульса 63 одновременно с занесением микрокоманды М 2 в регистр 7 на выходе элемента 13 вырабатывается импульс 72, По переднему Фронту импульса 72 блок 1 начинает выполнение микрокоманды М 1 (65), хранимой на регистре 7, В зависимости от кода микрокоманды блок 1 вы О полняет арифметико-логические и одни говые операции. Дешифратор 27 декодирует код микрокоманды и вырабатывает на одном иэ своих выходов сигнал соотнетствующего микроприказа. , 6 Арифметико-логические операции вы.полняются в блоке 1 над двумя операндами, один из которых находитсяв регистре 39, а другой поступаетна информационный вход 2. Причемна -выходе сумматора 28 формируетсязначение арифметической суммы слагаемых с учетом значения входногопереноса, сигнал которого поступаетна вход 23 блока 1. Если при этомпроисходит переполнение разрядной Одновременно по переднему Фронтуимпульса 72 блок 1 выполняет микрокоманду М 2, н результате чего Форми руется значения сигнала 73 логического условия, По адресной части микрокоманды М 2 и значению логического усдовия н блоке 5 формируетсяадрес микрокоманды МЗ или М 4, Например, по единичному значению сигнала. 73 условия в блоке формируетсяадрес микрокоманды М 4По заднемуфронту третьего синхроимпульса 63триггер 11 устанавливается в 11,а триггер 12 в 0. Сигнал 71с его выхода закрывает элемент 13.По заднему Фронту импульса 70 блок е)выдает на выход 16 адрес микрокоманды М 4, Микрокоманда М 4 ныбнраетсяиз блока б (64). Так как в адресной части микрокоманды М 4 задается безусловный переход к микрокоманде М 5,сигнал 67 принимает нулевое значение, вследствие чегосигнал 69 при 1045231нимает единичное значение. По четвертому синхроимпульсу 63 микрокоманда М 4 заносится в регистр 7 (65), На выходе элемента 13 импульс 72 не вырабатывается, чем предупреждается повторное выполнение блоком 1 микрокоманды М 2, По заднему фронту четвертого синхроимпульса 63 триггер 12 устанавливается в 1, а триггер 11 не меняет единичного состояния, По заднему фронту импульса 70 блок 5 выдает адрес микрокоманды М 5, вследствие чего микрокоманда М 5 выбирается из блока б, При поступлении следующего синхроимпульса 63 микрокоманда М 5 заносится в регистр 7, блок 1 выполняет микро- команду М 4, а блок 5 формирует адрес слелующей микрокоманды и т.д.При выполнении многих операций блок 1 обращается к блоку внешней памяти или внешнему устройству, выставляя на адресный выход 3 микропроцессора соответствующий адрес. Блок внешней памяти и внешние устройства, с которыми взаимодействует микропроцессор, не показаны. Если необходимо записать информацию в блок внешней памяти или внешнее устройство, что указывается в микрокоманде, на управляющем выхоле 8 микропроцессора устанавливается сигнал, соответствующий режиму записи, Записываемые данные из блока 1 выдаются на информационный выход 4. При чтении информации иэ блока внешней памяти или внешнего устройства на управляющий выход 8 поступает сигнал чтения, а считываемые данные передаются в блок 1 с информационного входа 2, Код, поступающий с первого выхода регистра 7 на вход 18 блока 5, определяет функцию управления логикой флагов, которая заключается либо в установлении выбранного Флага в соответствии созначением сигнала на входе 21 блока 5, либо в выдаче содержимоговыбранного флага или значений ф 0и 1 на выход 22 блока 5. Работаблока 5 при этом заключается в следующем, В соответствии с кодом,поступающим на вход 18 блока 5, наодном иэ выходов дешифратора 54вырабатывается управляющий сигнал.Если производится установка одногоиз триггеров 55, то по единичномусигналу с выхода дешифратора 54открывается один из элементов 56.15 При поступлении синхроимпульса навход 26 блока 5 на выходе элемента 56 вырабатывается импульс, позаднему фронту которогэ в с:ответствующий триггер 55 заносится значение сигнала на вхоле 21 блока 5,Если значение одного иэ триггеров 55выдается на выход 22 блока 5, то поединичному сигналу с выходалешифратора. 54 открывается один изэлементов 57 и содержимое триггера 55 поступает через элементы 57и 62 на выход 2 блока. Таким образом, предлагаемыймикропроцессор позволяет выполнять условные переходы в микропрограмме беэ использования холостых микрокоманд.Учитывая, что в реальных микро программах условный переход приходится в среднем на каждые 5-7 вы,полняемых микрокоманд, то использование предлагаемого микропроцессора позволяет сэкономить в среднем 15-20 дорогостоящей микропрограммной памяти (с 650 до 500 гликрокоманд),.Пчелинская Техред М.Тенер дакт Подписно 4 нтск П жгород,роектная, 4 ил акаэ 7555/51 ВНИИПИ ГосУДар по делам из 113035, МоскваТираж 70 бвенного комитета СССРретений и открытийЖ, Раушская наб.,Корректор Г. Решетник

СмотретьЗаявка

3393338, 12.02.1982

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 30.09.1983

Код ссылки

<a href="https://patents.su/7-1045231-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для тестового диагностирования

Следующий патент: Вероятностный автомат

Случайный патент: Устройство для отбора проб аэрозоля