Устройство для отображения информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1042069

Автор: Копанев

Текст

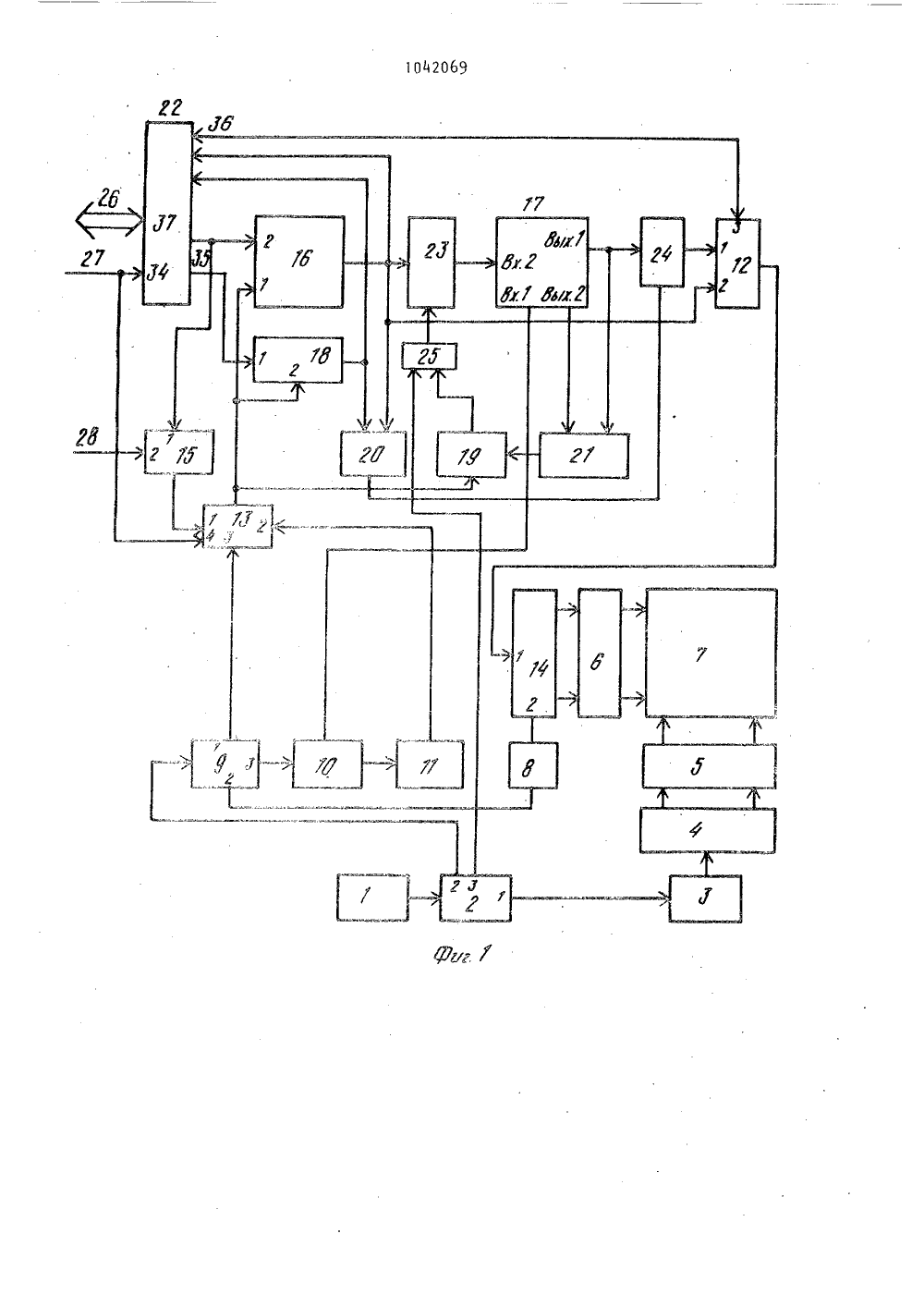

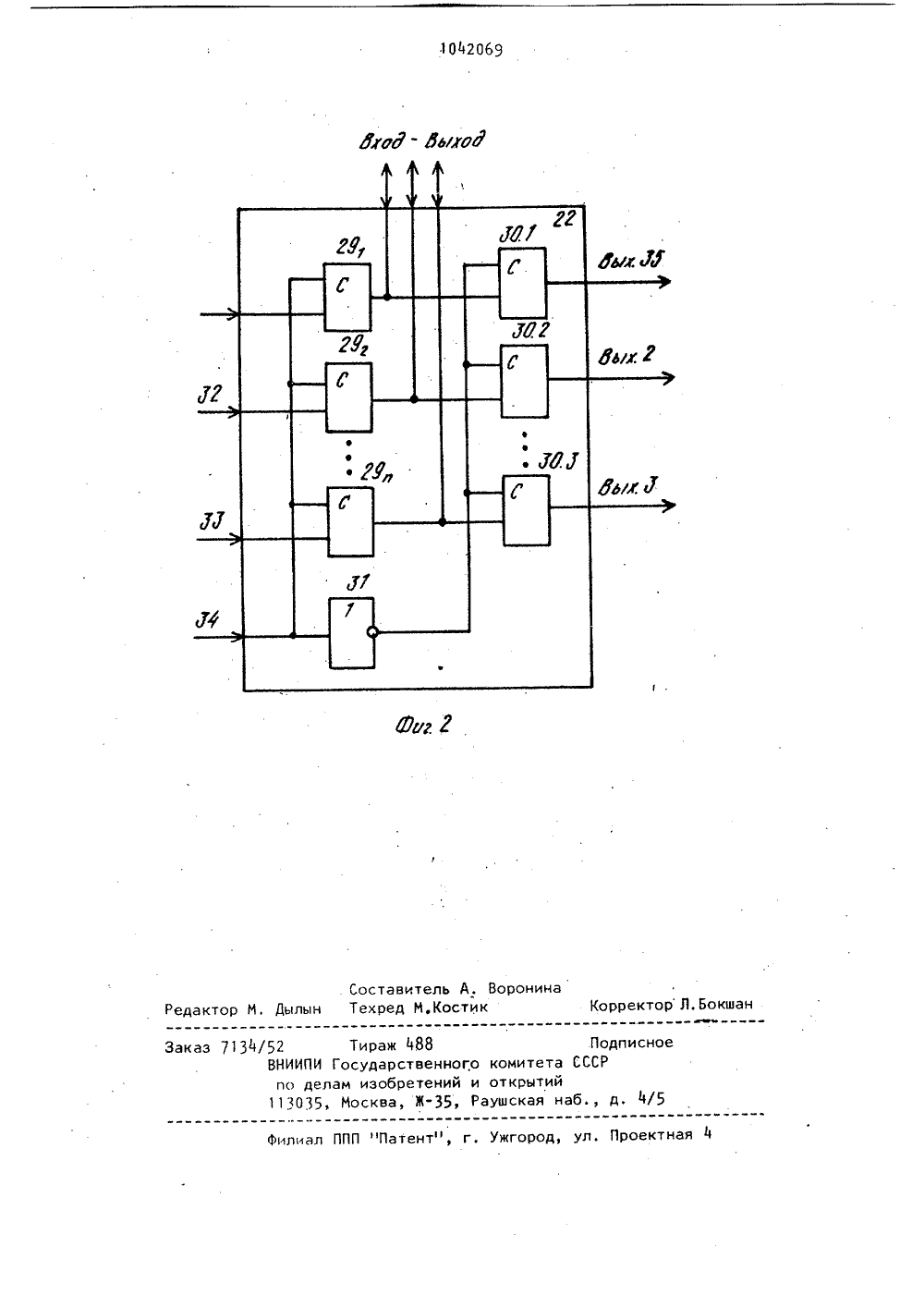

АНИЕ ИЗОБРЕТОРСИОМУ СВИДЕТЕЛЬСТВУ ОПИС211.83., Бюл. МКопанев27 088.8) 78 .0 4 ги бл вх ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 56) 1. Авторское свиЙ 960920 кл, 09 6 3 детельство СССР/28, 1981,54) (57) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯИНФОРМАЦИИ, содержащее последовательно соединенные генератор импульсов,делитель частоты, первый сцетчик,первый дешифратор и первый бло ключей, соединенный с вертикальными шинами матричной индикаторной панели,последовательно соединенные первыйкоммутатор, первый регистр и второйблок ключей соединенный с горизонтальными шинами панели, последова"тельно соединенные второй, третий ичетвертый счетчики, второй выходделителя частоты соединен с входомвторого счетчика, второй выход которого соединен с входом второго дешифратора, выход которого соединенс вторым входом первого регистра,третий выход второго счетчика соеди"нен с первым входом второго коммутатора,. второй вход которого соединенс выходом четвертого счетчика, а третий вход - с выходом второго регистра, выход второго коммутатора соединен с первым входом первого блокапамяти, и знакогенератор, первыйвход которого соединен с выходом%третьего счетчика, первый вход второго регистра является первым входомустройства для отображения информации, о т л и ч а ю щ е е с я тем,,что, с целью повышения достоверности отображения информации при ее вос. произведении в случае выхода из стро блока памяти и знакогенератора, в него введен второй и третий блоки памяти, две схемы сравнения, третий коммутатор, элемент И, блок элементов И и блок инверторов, выход которого соединен с первым входом первог коммутатора, второй вход которого соединен с первыми входами третьего коммутатора и первой схемы сравнения второй вход которой соединен с выходом второго блока памяти и вторым входом третьего коммутатора, первый вход второго блока памяти соединен с выходом второго коммутатора, а второй вход - с первым выходом треть его коммутатора, выход первого блока памяти соединен с первым входом блока элементов И, второй рход которого соединен с выходом элемента И,первыи вход которого соединен с третьим выходом делителя частоты, второй вход - с выходом третьего блока памяти, первый вход которого соединен с выходом второго коммутатора, а второй вход - с выходом второй схемы сравнения, первый вход которой соединен с первым выходом знакогенератора, второй выход которого соединен с вторым входом второй схемы сравнения и первым входом блока инверторов, второй вход которого соединен с выходом первой схемы сравнения, третий вход первого коммутатора соединен с вторым выходом третьего коммутатора, третий выход которого соединен с вторыми входами второго рестра и. первого блока памяти, выход ока элементов И соединен с вторым одом знакогенератора, третий входтретьего коммутатора соединен с чет-вертым входом второго коммутатора и1 10 ф 2069является вторым входом устройства для отображения информации, 1Изобретение относится к автоматикеи вычислительной технике, в частностик индикаторным устройствам, и можетбыть использовано в устройствах вывода информации из ЭВИ, 5Известны устройства для отображенияинформации, содержащие последовательно соединенные блок памяти, знакогенератор, коммутатор, регистр и первый блок ключей, соединенный с горизонтальными шинами матричной панели,последОвательно соединенные генераторимпульсов, делитель частоты, второйсчетцик, дешифратор и второй блок клю.цей, соединенный с вертикальными шинами панели последовательно соединен7ные второй, третий и цетвертый счетчики, второй дешифратор и второйкоммутатор 1Недостаток данного устройствазаклюцается в низкой достоверостиотображения информации за счет отсутствия контроля работы блока памяти изнакогенератора,Целью изобретения является повыше1 ние достоверности отображения информации при ее воспроизведении вслучае выхода из строя блока памятии знакогенератора.Указанная цель достигается тем,что в устройство для отображения информации, содержащее последовательносоединенные генератор импульсов, делитель частоты, первый счетчик, первый дешиФРатор и первый блок ключей,соединенный с вертикальными шинамиматричной индикаторной панели, последовательно соединенные первый коммутатор, первый регистр и второй блокключей, соединенный с горизонтальны 4 Оми шинами панели, последовательносоединенные второй, третий и четвертый сче гчики, второй выход делителячастоты соединен с входом второгосчетчика, второй выход которого соеди нен с входом второго дешифратора,выход которого соединен с вторым входом первого регистра, третий выходвторого счетчика соединен с первым 2входом второго коммутатора второй ,вход которого соединен с выходомчетвертого счетчика а третий вход с выходом второго регистра, выход второго коммутатора соединен с первым входом первого блока памяти, и знакогенератор, первый вход которого соединен с выходом третьего счетчика, первый вход второго рет истра являет - ся первым входом устройства для отображения информации, введены второй и третий блоки памяти, две схемы сравнения, третий коммутатор, элемент И, блок элементов И и блок инверторов, выход которого соединен с первым входом первого коммутатора, второй вход которого соединен с первыми входами третьего коммутатора и первой схемы сравнения, второй вход которой соединен с выходом второго блока памяти и вторым входом третьего ком мутатора, первый вход второго блока памяти соединен с выходом второго коммутатора, а второй вход с пер - вым выхОдом третьего коммутатора, выход первого блока памяти соединен с первым входом блока элементов И, второй вход которого соединен с выходом элемента И первый вход которого соединен с третьим выходом делителя частоты, второй вход с выходом третьего блока памяти первый вход которого соединен с выходом второго коммутатора,. а второй вход - с выходом второй схемы сравнения, первый вход которой соединен с первым выходом знакогенератора, второй выход которого соединен с вторым входом второй схемы сравнения и первым входом блока инверторов, второй вход которого соединен с выходом первой схемы сравнения, третий вход первого коммутатора соединен с вторым выходом третьего коммутатора, третий выход которого соединен с вторыми входами второго регистар и первого блока памяти, выход блока элементов И соединен с вторым входом Знакогенератора, третий вход третьего коммун10 М 2069 4реса 1 на первый вход второго реГистра15 поступают импульсы стробированияадреса в результате на выходе, второгозрегистра 15 Формируется код адресазаписи который поступает на третийвход второго коммутатора 13 и далеес его выхода - на первый адресныйвход блока памяти 16 и первый ( адресный 1 вход второго блока памяти10 18 (накопителя четности), на второйвход которого с первого выхода 35коммутатора 22 поступают биты контроля четности информационного слова,поступающие от источника информации15 с входа .выхода 26, Таким образом,в блоке памяти 16 осуществляется после.довательная запись кодов символов, к в случае записи цифро.буквенной информации или точек, в случае записи20 ГраФической информации, подлежащихотображению на матричной газоразрядной панели 7, а во втором блоке памяти 18 записываются контрольные битычетности, соответствующие этим кодам25 прицем каждому знакоместу или точкена экране панели 7 соответствуетячейка или бит памяти в блоке памяти16 и первом накопителе цетности 18,Остальные узлы устройства в этомрежиме уцастия не принимают.1 3тора соединен с четвертым входомвторого коммутатора и является вторывходом устройства, для отображенияинФормации,На фиг, 1 представлена структурнасхема устройства, на фиг. 2 - пример выполнения третьего коммутатора.Схема включает генератор 1 импульсов, делитель 2 частоты, первый 3счетчик, первый дешифратор М, первыйблок 5 ключей, второй блок 6 ключей,матричную индикаторную панель 7, второй дешифратор 8, второй счетчик 9,третий счетчик 10, четвертый счетчик11, первый коммутатор 12, второйкоммутатор 13, первый регистр 1второй регистр 15 первый блок памяти 16, знакогенератор 17, второй блопамяти 18, третий блок памяти 19,первую 20 и второй 21 схемы сравнения, третий коммутатор 22, блок элементов И 23, блок инверторое 2 чэлемент И 25, вход-выход третьегокоммутатора 26, второй вход устройстеа 27, первый вход устройства 28,элементы И первой группы 291 -,29 п,элементы И второй группы 30- 30 п 1инеерор 31, первый, второй и третййвходы третьего коммутатора 32 33 и3, первый, второй и третий выходытретьего коммутатора 35, 36 и 37,Устройство работает следующимобразом.Режим записи информации,На второй вход устройства (выбора35режима работы) и далее на первый вход3 ч третьего коммутатора 22 и четвертый вход второго коммутатора 13 поступает сигнал "Запись". При этом коммутатор 22 подготавливается для про 40хождения сигнала с информационноадресного входа-выхода устройства навторой вход второго регистра 15 ивторой вход блока памяти 16 путемподачи на управляющие входы первой45группы элементов И 29 - 290,фиг. 2 ) запрещающего уровня сигналас второго входа устройства 27, а науправляющие входы второй группы элементов И (30.1 - 30 я фиг. 2) разре 50шающего уровня сигнала с выхода элемента НЕ, что вызывает закрываниеэлементов И первой группы 1,29- 291)и открывание элементов И второй группы (30.1 - 304 а также обеспечивает-55ся прохождение сигналов с второговхода второго коммутатора 13 на еговыход. Синхронно с этим с первоговхода 28 сигнала опробирования адРежим контрольного считывания и отображения информации.На второй вход выбора устройства 27 режима работы и далее на,третий вход коммутатора 22 и четвертый вход второго коммутатора 13 посту пает сигнал "Отображение", Коммутатор 22 подготавливается для прохождения сигналов с его первого и второго входов на выход и далее на информа ционно-адресный вход-выход устройст ва 26 путем подачи на управляющие входы первой группы элементов И291 - 29, фиг, 2) разрешающего уровня сигнала с второго входа уст ройства 27, а на управляющие входы второй группы элементов И30. 1 30 и, фиг 2) запрещающего уровня сигнала с выхода элемента НЕ, цтовызывает закрывание элементов И первой группы ( 29 1 - 29), а также запрещается прохождение сигналов адреса с третьего входа второго коммутатора 13 и разрешается прохождение сигналов адреса считывания с третье го выхода второго счетчика 9 и выхода четвертого счетчика 11 на выход второго коммутатора 13 и далее на ад 10 ф 20ресные входы блока памяти 16, второго18 и третьего 19 блоков памяти.Импульсы с выхода генератора 1поступают на вход делителя частоты2 и с его первого выхода поступают 5на последовательно соединенные второй9, третий 10 и четвертый 1 счетчики,обеспечивающие последовательное наращивание кода адреса считывания,чТаким образом осуществляется по, следовательный опрос ячеек блокапамяти 16 и второго блока памяти. 18, информация с выхода блока памяти16 поступает на первый вход третьего коммутатора 22, а контрольныебиты считывания с выхода второгоблока памяти 18 - на второй вход коммутатора 22 и далее на информационноадерсный вход-выход устройства, т.е.обеспечивается контрольное считывание записанных кодов с целью обратного контроля их источником информации,Одновременно коды символов, подлежащих отображению, и контрольныебиты четности поступают с выходовблока памяти 16 и второго блока памяти 18 на второй и первый входы первой схемы сравнения 20 (контролячетности, осуществляющей аппаратныйконтроль на четность считываемой информации, а сигналы с выхода блокапамяти 16 поступают через элементыИ блока 23 и на второй вход знакогенератора 17, преобразуются им в 35коды подсвета вертикальных фрагментов знакоместа, а с его первого выхода поступают на первый вход блокаинверторов 21 и второй вход второйсхемы сравнения 21 ( контроля четности 40на первый вход которой поступаютс второго выхода знакогенератора 17контрольные биты четности кодов подсвета, хранящиеся в прошивке знакогенератора 17. При исправной работе 45знакогенератора 17 на выходе второйсхемы сравнения 21 (контроля четности) Формируется сигнал логической1", который через третий блок памяти19 и элемент И 25 поступает на второй 50управляющий) вход блока элементовИ 23, обеспечивая непрерывное прохождение сигналов с выхода блока памяти16 на второй вход .знакогенератора 17.При неисправности знакогенератора 55( например, число единиц в коде подсвета знака нечетное) на выходе второйсхемы сравнения 21 ( контроля четности) 69 Ьформируется сигнал логического "0",который запоминается третьим блокомпамяти 19 и с его выхода поступаетна первый вход элемента И 25, разрешая тем самым прохождение через негоимпульсных сигналов с третьего выхода делителя частоты 2 на. второйуправляющий) вход блока элементов И3, которые вызывают периодическоезапирание блока 23, что вызывает попеременное поступление на второй входзнакогенератора 17 кода отображаемого символа и кодагашения", а этовызывает мигающее изображение наэкране панели 7 символа, в формировании кодов подсвета которого принимаютучастие неисправные фрагменты знакогенератора 17, на основании чегооператор делает вывод Ь неисправностизнакогенератора 17.С выхода блока инверторов коды подсвета через первый коммутатора 12последовательно поступают на первый (информационный) вход первого регистра 1, синхронно с этим на его второй ( управляющий ) вход с выхода второго дешифратора 8 поступают сигналы записи кодов подсвета первой, второй, )-й строки, тем самым на выходе первого регистра 14 формируются сигналы подсвета всего вертикального электрода панели 7, которые через второй блок ключей 6 поступают на электроды панели 7. Синхронно с этим импульсы сканироВания с первого выхода делителя частоты 2 поступают на вход счетчика 3, а с его выхода через первые дешифратори блок ключей 5 поступают на первый вертикальный электрод панели 7, тем самым производится возбуждение индуцируемых ячеек на этом вертикальном электроде.Далее процесс опроса блока памяти 16 и второго блока памяти 18, а также процесс подготовки сигнала подсвета всего вертикального электрода панели 7 повторяется до заполнения всего экрана, после чего процесс повторяется с частотой регенерации изображения.При исправной работе блока памяти 16 на выходе первой схемы сравнения 20 формируется сигнал логической "1", поступающий с ее выхода на второй ( управляющий) вход блока инверторов и обеспечивающий прохождение кодов подсвета с первого выхода знакогенератора 17 через блок инвер7 1042торов 24 без инверсии. При неисправ" "ности блока памяти 16 либо считыванииложной информации (например, числоединиц в коде нечетное) на выходепервой схемы сравнения 20 (контролячетности) формируется сигнал логического "0", который вызывает инвертирование блоком инверторов 24 кодовподсвета символов, что вызываетна экране панели 7 негативное изоб- ,10ражение соответствующего символа,код которого считан из блока памяти16 с ошибкой,В случае отображения графическойинформации на третий 1 управляющий) 15вход первого коммутатора 12 с второговыхода 36 коммутатора 22, подготовленного для прохождения сигналов 069 8с входа-выхода устройства 26, поступает сигнал графика, запрещающий,прохождение на вход первого регистра14 сигналов подсвета с выхода знакогенератора 17 и разрешающий прохождение сигналов с выхода блока памяти16, представляющих собой непосредственно коды подсвета точек на экранематричной газоразрядной панели 7,Таким образом, предлагаемое устройство позволяет осуществлять как запись, так и обратное ( контрольное 7 считывание кодов отображаемой инкрмации, а также обеспечивает контроль исправности блока памяти и знакогенератора что резко повышает достоверность отображаемой информации.1042069 ЮюР - Боои ина Составитель А, Техред М,Кости ктор Л, Бокш Редактор М, Дылын ака эл ППП "Патент", г. Ужгород, ул. Проектная 4/52 Тира ВНИИПИ Госуда по делам изо 113035, Москв

СмотретьЗаявка

3378997, 08.01.1982

ПРЕДПРИЯТИЕ ПЯ В-8690

КОПАНЕВ АЛЕКСАНДР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 3/147, G09G 3/28

Метки: информации, отображения

Опубликовано: 15.09.1983

Код ссылки

<a href="https://patents.su/7-1042069-ustrojjstvo-dlya-otobrazheniya-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для отображения информации</a>

Предыдущий патент: Устройство для отображения информации

Следующий патент: Устройство для отображения информации на газоразрядной индикаторной панели

Случайный патент: Устройство для лечения ожогов