Цифровая система программного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 888074

Автор: Бондарев

Текст

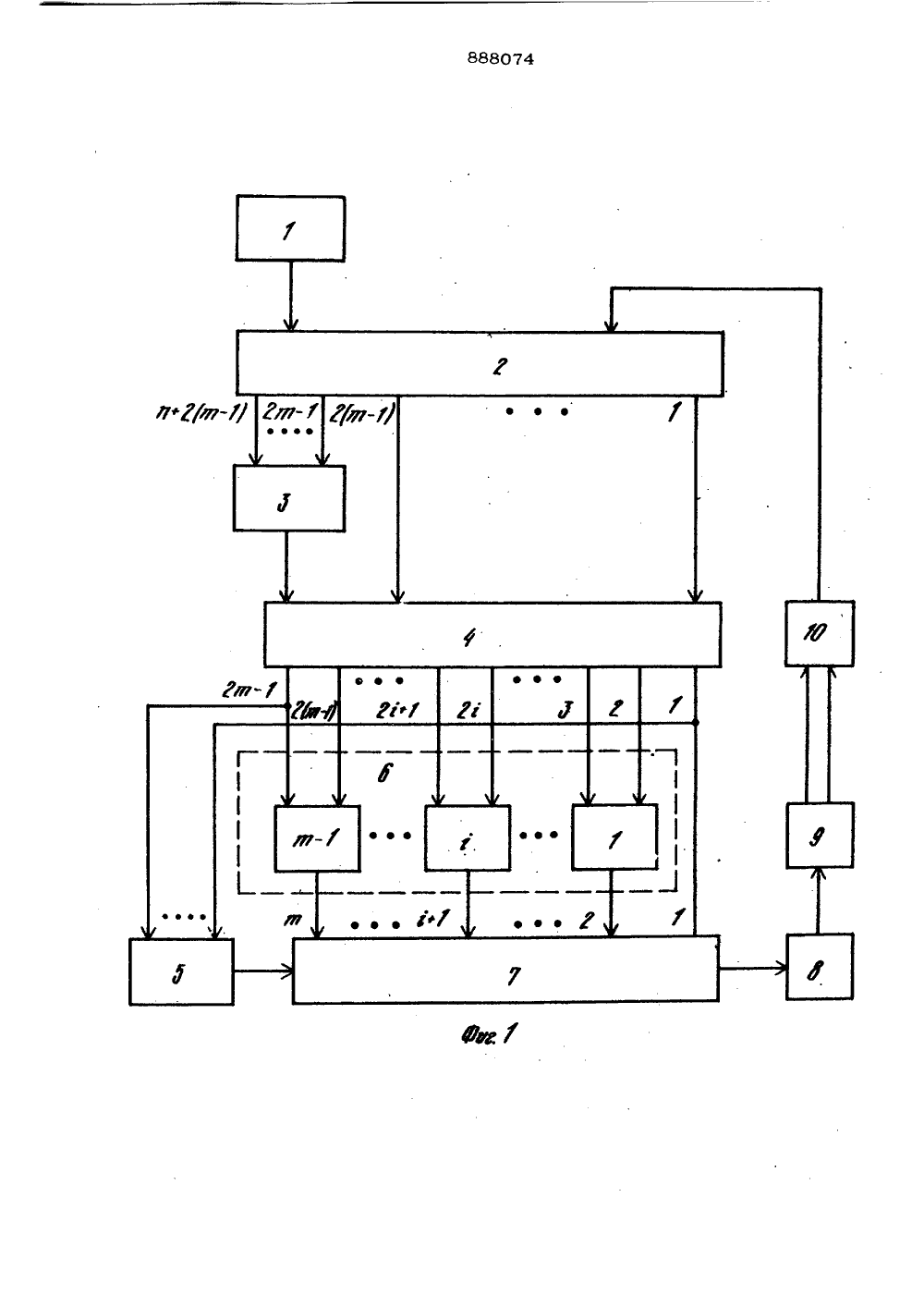

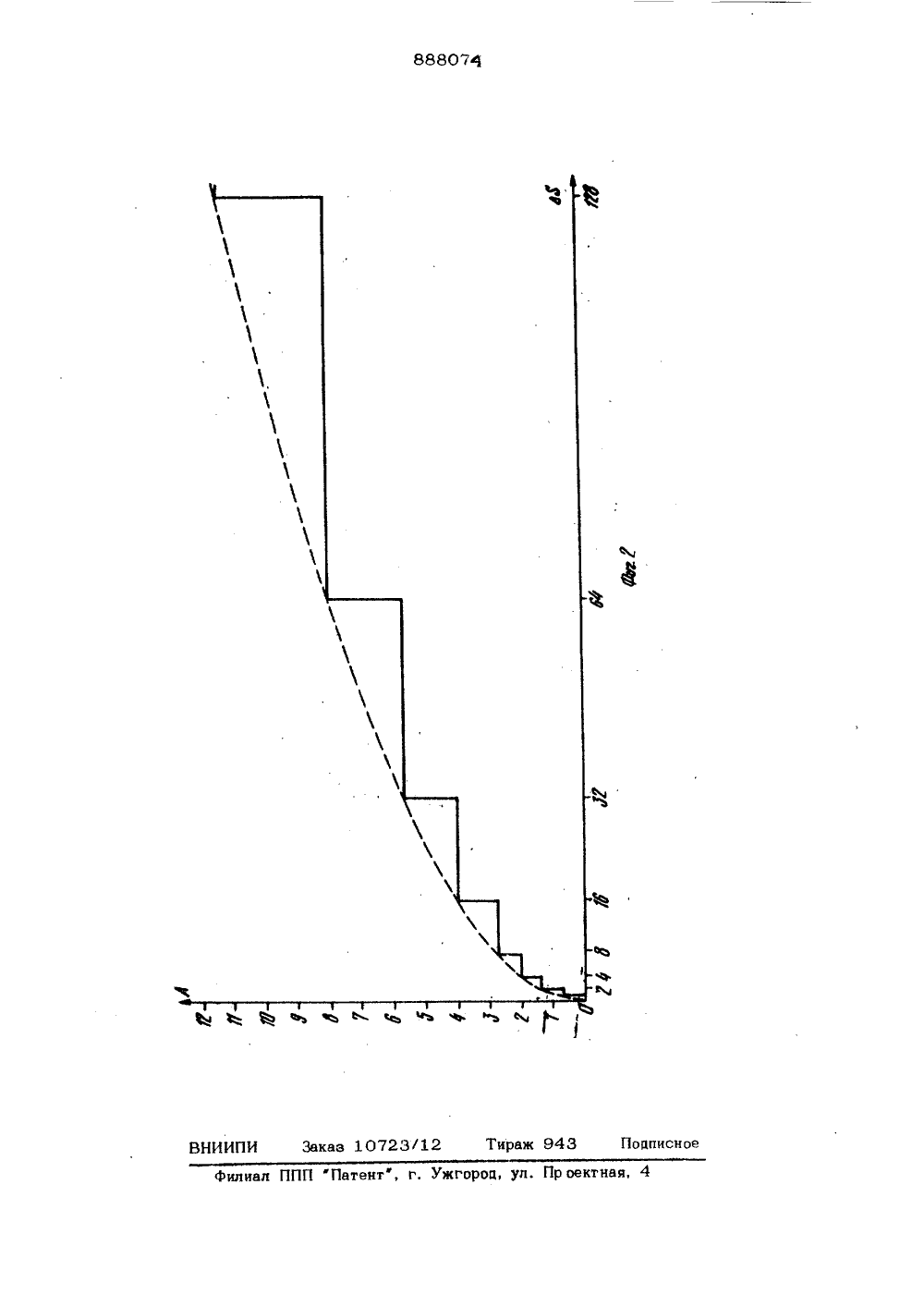

) Заявитель Волжское объединение по произво автомобилей АвтоВА(54) БИфРОВАЯ СИСТЕМ РАММ НОГО НИЯ амплитутветсввыделяемыхти Дний объе Я Изобретение относится к автоматическому управлению производственными процессами и может быть применено в шаровых системах автоматического управления позиционированием различных перемещающихся объектов.Известна цифровая система автоматического регулирования, содержащая по-следовательно соединенные преобразователь код-напряжение, усилитель, блок управления, датчик обратной связи и сумматор, вход которого соединен с выходом блока задания программы, а выходы старших разрядов сумматора подключены к входам элемента ИЛ,И 11,Недостатками этой системы являются большое время торможения и необходимость применения корректирующих устройств, что приводит к снижению быстродействия и точности системы в целом.Наиболее близким решением по технической сущности к изобретению являетс цифровая система программного управления, содержащая последовательно соединенные преобразователь код-напряженна, блок управления, датчик обратной связи и сумматор, вход которого соединен с выходом бежа задания проф граммы, а выходы старщих разрядовсумматора подключены к входам элемента ИЛИ, выход которого соединен с одним входом логическаго блока выделени старщего разряда, другие вхоф ды которого соединены с соответствуюшими выходами младщих разрядов сумматора 2),Преобразователь ищ-напряжение этого устройства выдает линейно убывающуюде гистограмму напряжений 0соо ующнх весам последовательностарщих разрядов кода раззаданного и текущего полокта. Линейно убывающая цо иоамплитуде гистограмма торможения позвопиет повысить быстродействие системыпри обработке больших перемещений засчет сокращения времени торможения.20 Однако в области средних и малыхперемещений выигрыш в быстродействии,полученный за счет ускоренного торможения,компенсируется потерей временина участке разгона, так как здесь амплитуда сигнала на выходе данного регулятора положения значительно ниже, чему линейного при одинаковом коэффициенте усиления усилителей,Нелинейность характеристики; регулятора положения невелика и при йаличиистатических усилий, воздействующих наобъект управления, по касательной ктраектории перемещения в точке позиционирования, не позволяет повыситьстатическую точность системы путемувеличения коэффициента усиления,Основными недостатками данной системы являются низкое быстродействиепри средних и малых перемещениях иневысокая статическая точность при наличии статических усилий, воздействующих на объект по касательной к траектории перемещения в точке позиционирования. 11 елью изобретения является повышение быстродействия и точности системы.Поставленная цель достигается тем, что в цифровую систему программного управления, содержащую последовательно соединенные преобразователь двоичный код-аналог, усилитель, блок управления, датчик обратной связи и сумматор, вход которого соединен с выходом блока задания программы, а выходы старших разрядов сумматора подключены к входам первого элемента ИЛИ, выход которого соединен с одним входом логического блока выделения ,старшего разряда, другие входы которого соединены с соответствующими выходами младших разрядов сумматора, а выход первого разряда логического блока выделения старшего разряда соединен с входом первого разряда преобразователя двоичный код-аналог, введены логический блок определения четности старшего разряда и вторые элементы ИЛИ, каждый первый вход которых соединен с выходом логического блока выделения старшего разряда, номер разряда которого вдвое больше номера соответствующего ему второго элемента ИЛИ, а каждый второй вход соединен с выходом логического блока выделения старшего разряда, номер разряда которого на единиц больше удвоенного номера соответсвуюцего ему второго элемента ИЛИ, выход каждого второго элемента ИЛИ соединен с входом преобразователя двоичный код-аналог, номер разряда которого на единицу больше номера соответсвующего ему второго элемента ИЛИ, причем управляющий вход преобразователя двоичный код-аналог соединен с выходом логического блока определения четности старшего разряда, а входы логического блока определения четности старшего разряда соединены с соответсвуюшими выходами логического блока выделения старшего разряда. Такая сис тема увеличивает быс тродействие, скорость процесса позиционирования с помощью торможения с постоян-ным максимально допустимым по величине ускорением и повышает статичес-кую точность позиционирования благодаря увеличению коэффициента усиленияв зоне малых рассогласований положению.На фиг. 1 представлена схема цифровой системы программного управления;на фиг, 2 - зависимость амплитуды аналогового сигнала А на выходе управляемого преобразователя двоичный код-аналогот кода разностизаданного и текущего положений объект 1,Система содержит блок 1 заданияпрограммы, сумматор 2 на И+ 2(И)разряд, элемент ИЛИ 3, логический блок4 выделения старшего разряда, логический блок 5 определения четности старшего разряда, уп -1 дополнительныхэлементов ИЛИ 6, (управляемый) преобразователь двоичный код-аналог на Мразрядов, усилитель 8, блок 9 управления и датчик 10 обратной связи.Работает система следующим образом,Блок 1 выдает в сумматор 2 кодзаданного положения объекта, Сумматор 2 формирует двоичный код разности заданного и текущего положений объекти и 2( Ю) младших разрядов двоичного кода, разности поступают непосредственно в блок 4, а И старших,разрядов через элемент ИЛИ 3,Блок 4 разрешает прохождение лишьстаршего разряда, поступающего на еговходы кода. Код выделенного старшегоразряда с выходов блока 4 поступаетна входы блока 5. Блок 5 управляеткоэффициентом преобразования преобразователя 7, выдавая на управляющий входпреобразователя 7 цифровой сигнал, вы5 8 эываюший уменьшение коэффициента преобразования преобразователя 7 в -2 раэ в том случае, когда номер выделенного старшего разряда двоичного кода четный или первый, и увеличивающий коэффициент преобразования преобразователя 7 обратно до исходного значения, когда номер выделенного старшего разряда двоичного коа нечетный, эв исключением первого.Изменение коэффициента преобразования преобразователя 7 может быть выполнено различными способами, например с помощью управляемого электронного ключа, переключающего сопротивления в цепи обратной связи суммирующего усилителя в преобразоавтеле 7,Нечетные разряды выходного двоичного кода блока 4 передаются параллельно в порядке возрастания на входы разрядов управляемого преобразователя 7: первый разряд - непосредственно на вход первого разряда преобразователя 7, остальные, начиная с третьего, через элементы ИЛИ 6 так, что 1 -й из этих элементов передает (21+1) -й раьряд выходного двоичного кода блока 4 нв ( 1 +1) -1 Гразрядный вход преобразователя 7.Число, представляющее вес (+1) -го разряда двоичного кода, где- любое число натурального ряда или нуль, равно корню квадратному из числа, представляющего вес (2 +1) -го нечетного разряда двоичного кода, поэтому при поочередном выделении блоком 4 нечетных разрядов двоичного кода разности, на выходе преобразователя 7 появятся аналоговые сигналы представляюшие, за исключением случая выделения первого разряда, в определенном масштабе, соответсвуюшем большему из двух возможных значений коэффициентов пре-. образования преобразователя 7, корни квадратные из весов, поочередно выделяемых логическим блоком 4 нечетных разрядов двоичного кода разности,Исключение, касающееся первого разряда двоичного кода разности, состоит в том, что он преобразуется в аналоговый сигнал при уменьшенном в-Г 2 раз коэффициенте преобразования преобразователя 7.Четные разряды выходного кода блока 4 передаются параллельно в порядке возрастания нв входы разрядов пре образователя 7 через элементы ИЛИ 6 так, что 1 - й дополнительный элемент ИЛИ 6 передает 21,разряд выходного 88074 4кода блока 4 на ( 1 +1)-й разрядныйвход преобразователя 7.Вес каждого четного разряда двоичного кода в 2 раза меньше веса, соотг ветсвуюшего ему большего нечетногоразряда, корень квадратный иэ веса каждого четного разряда двоичного кода в2 раз меньше корня квадратного иэ веса соответсвующего ему большего нечет ного разряда. Так квк каждый четныйразряд выходного двоичного кода блока4 передается через элемент ИЛИ 6 натот же разрядный вход преобразователя7, что и соответсвуюший ему больший 1 нечетный разряд и при выделении старшего четного разряда коэффициент преобразования преобразователя 7 уменьшается в 1 Г 2 раэ по сигналу от блока5, то при последовательном выделении фй блоком 4 четных разрядов на выходепреобразователя 7 так же, квк и вслучае с выделением нечетных разрядов, появятся аналоговые сигналы, представляющие корни квадратные из весов Ъ 5выделяемых четных разрядов, причемв том же масштабе, что и для случаявыделения всех нечетных, кроме первогоразрядов.Таким образом, при выделении блоком4 как четных, твк и нечетных разрядовдвоичного кода разности, преобразователь 7 поочередно выдает аналоговыесигналы, соответствуюшие корню квадратному иэ весов отдельных разрядов 35 двоичного кода разности заданного итекущего положений объекта и обрвэуюшие параболическую зависимость, представленную на фиг. 2щй Аналоговый сигнал с выхода преобразователя 7 через усилитель 8 поступает на блок 9, перемещающий объектуправления и дат .ик 10. Крд текущегоположения объекта с выхода датчика 10поступает на второй вход сумматора 2,который формирует новый двоичный кодразности, В случае отсутствия статических усилий, действующих нв объект покасательной к траектории перемешенияв заданной точке позиционирования, присовпадении кодов текущего и заданногоположений код разности становится равным нулю, аналоговый сигнал на входусилителя не подается и перемешениезаканчивается в заданной точке,Для оптимального по быстродействиюпроцесса позиционирования характерноторможение с постоянным максимальнодопустимым по величине ускорением,40 7 8880Связь скорости и перемещения при равноускоренном движении определяетсясоотношеннем е =Г 2 дВ, гае Е - скорость, С 1 - ускорение,- перемещение,Следовательно, задание на скорость,вырабатываемое регулятором положения позиционной. системы, допжно бытьсвязано с рассогласованием по перемещению параболической зависимостью,что и обеспечивается в данной системе.Параболическая зависимость позволяет получить существенный выигрышво времени при обработке малых и средних перемещений, при этом регуляторположения предлагаемой системы может.иметь больший, допустимый по условиямустойчивости системы коэффициентаусиления в зоне малых рассогласованийпо положению. Поэтому при наличиистатических усилий, действующих наобъект управления по касательной к тра- .ектории перемещения в точке позиционирования, данная система будет обладатьбольшей статической точностью.Разрядность преобразователя код- д 5аналог в системах позиционирования опредепяется в общем случае разрядностьюкода, представляющего максимапъныйпуть торможения объекта. Разрядностьпреобразователя двоичный код-аналог30в предлагаемой системе уменьшена на, где ф - число разрядовпреобразователя двоичный код-анапогори обычном построении системы,Это определяется тем, что в данной35системе все разряды преобразователя 7,кроме первого, используются для преобра-зования в аналог двух разрядов кодаразности заданного и текущего положений объекта, Уменьшение необходимой разрядности преобразователя двоичный код-аналог в системе является еесущественным достоинством при построеащ точных систем позиционирования дляобьвктов имеюших большой путь торможе 45иия, когда обычное построение системыможет стать неприемлемым, из.за практической невозможности построения преобразователя код-аналог на необходимоечисло разрядов,формула изобретенияБировая система программного управпеиия, содержащая поспедоватепьно 74 8соединенные преобразователь двоичный код-аналог, усилитель, блок управления, датчик обратной связи и сумматор, второй вход которого соединен с выходом блока задания программы, а выходы старших разрядов сумматора подкпючены к входам первого элемента ИЛИ, выход которого соединен с одним входом логического блока выделения старшего разряда, другие входы которого соединены с соответсвуюшими выходами младших разрядов сумматора, а выход первого разряда логического блока выделения старшего разряда соединен с входом первого разряда преобразователя двоичный код-аналог, о т и и ч а ю - ш а я с я тем, что, с целью повышения точности и быстродействия системы, в нее введены логический блок определения четности старшего разряда и вторые элементы ИЛИ, каждый первый вход которых соединен с выходом логического блока выделения старшего разряда, номер разряда которого вдвое больше номера соответсвуюшего ему второго элемента ИЛИ, а каждый второй вход соединен с выходом логического блока выдепения старшего разряда, номер разряда которого на единицу больше удвоенного номера соответсвуюшего ему второго элемента ИЛИ, выход каждого второго элемента ИЛИ соединен с входом преобразователя двоичный код-аналог номер разряда которого на единицу больше номера соответсвуюшего ему второго элемента ИЛИ, причем управляющий вход преобразователя двоичный код-аналог соединен с выходом лОгического блока определения четности старшего разряда, а входы логического блока оп редепения четности старшего разряда соединены с соответствующими выходами логического блока выделения старшего раз, рядиИсточники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР М 447684, кл. З 05 В 11/26; 1973. 2, Авторское свидетельство СССР

СмотретьЗаявка

2898995, 25.03.1980

ВОЛЖСКОЕ ОБЪЕДИНЕНИЕ ПО ПРОИЗВОДСТВУ ЛЕГКОВЫХ АВТОМОБИЛЕЙ АВТОВАЗ

БОНДАРЕВ СЕРГЕЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G05B 19/18, G05B 19/416

Метки: программного, цифровая

Опубликовано: 07.12.1981

Код ссылки

<a href="https://patents.su/6-888074-cifrovaya-sistema-programmnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Цифровая система программного управления</a>

Предыдущий патент: Линейный интерполятор

Следующий патент: Система управления подачей шлифовального станка

Случайный патент: Кольцевой счетчик на динисторах