Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

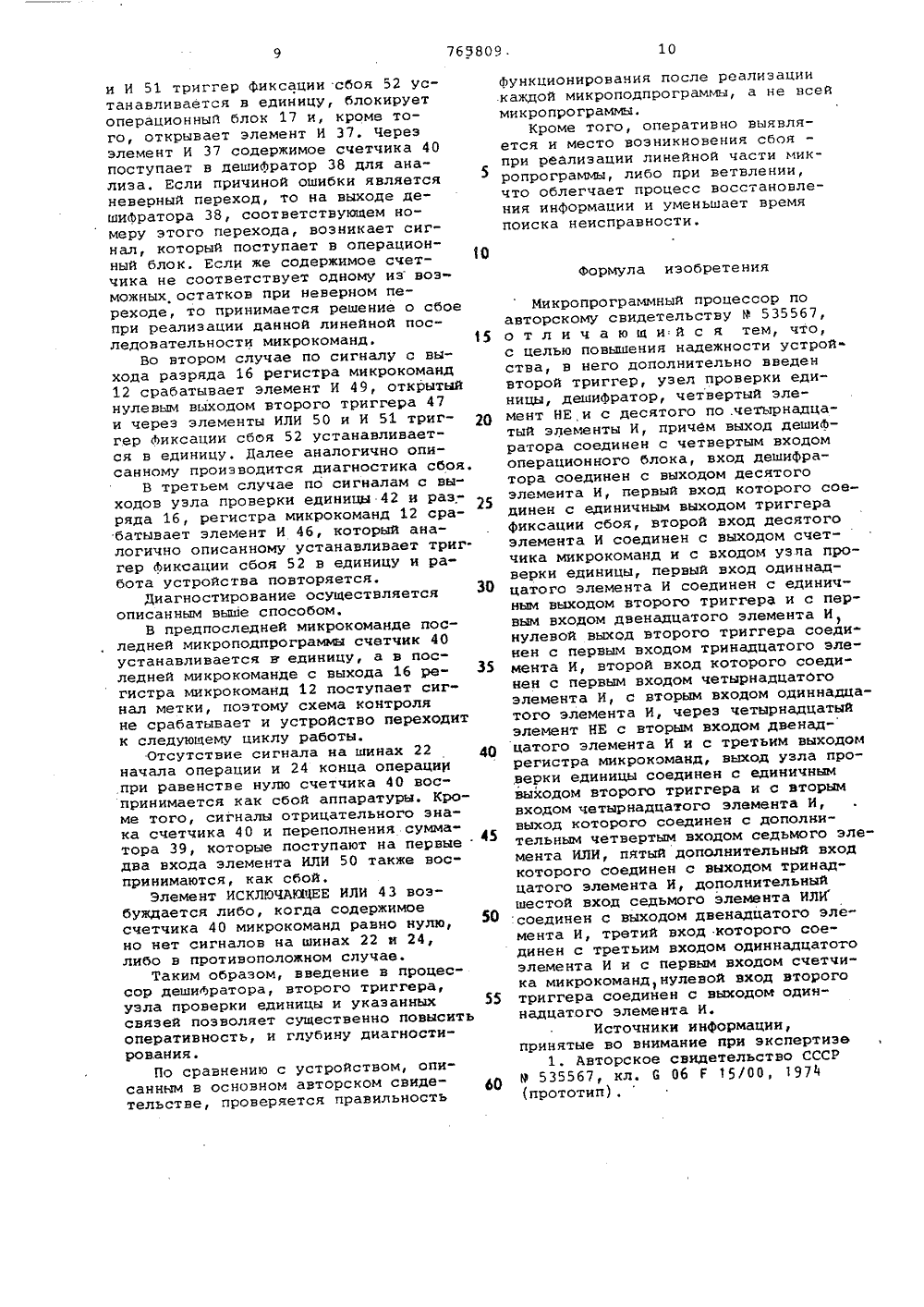

Союз Советских Социалистических Республик(22) Заявлено 09, 11. 78 (21) 2681280/18-24с присоединением заявки Нов(51) М ( 3 З 06 Г 15/00 Государственный комитет СССР по делам изобретений и открытий(54) МИКРОПРОГРАММНЫИ ПРОЦЕССОР Изобретение относится к вычислительной технике, в частности к само- контролируемым процессорам,В основном изобретении по авт. 5 свил. Р 535567 описан микропрограмный процессор, содержаший операционный блок, первый выход которого через блок сопряжения с оперативной памятью и регистр кода операций сое- т 0 динен с первым входом элемента И, выход которого через первый элемент ИЛИ соединен с первым входом регистра адреса микрокоманд, выход которого через блок памяти микрокоманд 15 соединен с входом регистра микрокоманд, первый и второй выходы которого соединены с первыми и вторыми входами операционного блока, второй и третий выходы которого шинами на чала и конца операции соединены с вторыми входами первого элемента И и регистра адреса микрокоманд соответственно и с входами второго элемента ИЛИ, выход которого через пер вый элемент НЕ соединен с первыми входами второго и третьего элементов Ы, выходы которого через первый и третий элементы ИЛИ соответственно соединены с первым и третьим вхо дами регистра адреса микрокоманд,четвертый вход которого соединен спервым входом счетчика микрокоманд.и шиной синхронизации с четвертымвыходом операционного блока, пятыйвыход которого соединен с вторым входом счетчика микрокоманд, а шестойвыход соединен с управляюшим входомблока памяти микрокоманд и с первымвходом четвертого элемента И, выход которого соединен с единичнымвходом триггера фиксации сбоя, единичный выход которого соединен стретьим входом операционного блока,седьмой выход которого соединен спервым входом первого узла,ветвления, второй вход которого соединенс третьим выходом регистра микрокоманд, третий выход соединен с вторым входом второго элемента И и выходом регистра микрокоманд, четвертый выход которого соединен с вторым входом третьего элемента И, выход первого узла ветвления черезтретий элемент ИЛИ соединен с третьим входом регистра адреса микрокоманд, а первый вход второго узлаветвления соединен с одноименнымвходом первого узла ветвления, второй вход которого соединен с первымивходами пятого и шестого элементовИ, через второй элемент НЕ - с первыми входами седьмого и восьмогоэлементов И, через четвертый элемент ИЛИ и третий элемент НЕ - стретьим входом второго элемента И ис первым входом пятого элемента ИЛИ,с вторым входом второго узла ветвления, третий вход которого соединенс третьим входом первого узла ветвления и с первым входом девятого элемента И,а выход второго узла ветвлениясоединен с вторым входом пятого элемента И, второй вход шестого элемента И соединен с четвертым выходомоперационного блока, а выход соединенс единичным входом триггера, единичный выход которого соединен с входом четвертого элемента ИЛИ и с вторым входом седьмого элемента И, выход которого соединен с вторым входом девятого элемента И, выход пятого и девятого элементов И и пятогоэлемента ИЛИ через шестой элементИЛИ соединены с первым входом сумматора приращения, первый выход которого соединен с третьим входом счетчика микрокоманд, первый выход которого соединен с вторым входом сумматора приращений и через узел проверки нуля - с первым входом элементаИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ й выходом пятого элементаИЛИ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИи вторые выходы счетчика микрокоманди сумматора приращений через седьмойэлемент ИЛИ соединены с вторым входом четвертого элемента И, второйвход восьмого элемента И соединен сшестым выходом операционного блока,а выход соединен с нулевым входомтриггераЯ40Низкая оперативность диагностирования этого устройства обусловленатем, что результаты контроля выдаются только по окончании реализацииоперации, что ограничивает применение такого процессора в составе ЭВИ,45работающих в реальном масштабе времени, и тем саьым сужает областьего возможного применения, а низкаяглубина диагностирования обусловленаневозможностью идентификации микроподпрограммы или перехода, на которых произошел сбой в микропрограмме.Цель изобретения - повышение надежности устройства,Это достигается тем, что в микропрограммный процессор по авт.свид.9 535567 дополнительно введены второй триггер, узел проверки единицы,дешифратор, четвертый элемент НЕ ис десятого по четырнадцатый элементыИ, причем выход дешифратора подключенк четвертому входу операционногоблока, вход дешифратора соединен свыходом десятого элемента И, первыйвход которого соединен с единичным выходом триггера фиксации сбоя, вто рой вход десятого элемента И подключен к выходу счетчика микрокоманд и входу узла проверки единицы, первый вход одиннадцатого элемента И соединен с единичным выходом второго триггера и с первым входом двенадцатого элемента И, нулевой выход второго триггера соединен с первым входом тринадцатого элемента И, второй вход которого соединен с первым входом четырнадцатого элемеьта И, с вторым входом одиннадцатого элемента И, через четвертый элемент НЕ - с вторым входом двенадцатого элемента И и с третьим выходом регистра микрокоманд, выход узла проверки единицы соединен с единичным входом .второго триггера и с вторым входом четырнадцатого элемента И, выход которого соединен с дополнительным четвертым входом седьмого элемента ИЛИ, пятый дополнительный вход которого соединен с выходом тринадцатого элемента И, дополнительный шестой вход седьмого элемента ИЛИ соединен с выходом двенадцатого элемента И, третий вход которого соединен с третьим входом одиннадцатого элемента И и с первым входом счетчика микрокоманд, нулевой вход второго триггера соединен с выходом одиннадцатого элемента И.Сущность изобретения состоит в осуществлении контроля каждой микро- подпрограммы, что позволяет повысить оперативность диагностирования, Кроме того, в процессоре при получении сигнала сбоя после реализации микро- подпрограммы возможна идентификация места сбоя между сбоем при ветвлении и сбОем во время реализации линейной части микропрограммы. Этим достйгается повышение глубины диагностирования.На чертеже приведена функциональная схема Микропрограммного процессора.Процессор содержит аппаратуру собственно процессора (элементы 1-26)и аппаратуру контроля (элементы 2752). Аппаратура собственного процессора состоит из второго 1 и четвертого 2 элементов ИЛИ, первого 3 итретьего 4 элементов НЕ первого 5и второго 6 элементов И, первогоэлемента ИЛИ 7, третьего элементаИ 8, третьего элемента ИЛИ 9, регистра адреса 10, памяти микрокоманд 11,регистра микрокоманд 12, содержащегополе 13 микрокоманды, поле 14 ветвления, поле 15 адреса и разряд 16удлиненйя адресного поля, операционный блок 17 с выходами конца операции 18, начала операции 19, логических условий 20 чтения микрокоманд21, гашения счетчика микрокоманд 22и тактовых импульсов (шина синхронизации) 23, блока 24 сопряжения с ОЗУпервого узла ветвления 25, регистра 26 кода операции. Аппаратура контроля процессора состоит из восьмого27 и шестого 28 элементов И, второгоэлемента НЕ 29, первого триггера 30,седьмого элемента И 31, второго узла ветвления 32, пятого элемента ИЛИ33, девятого 34 и пятого 35 элементов И, шестого элемента ИЛИ 36, девятого элемента И 37, дешифратора 38,сумматора 39 приращений, счетчика40 микрокоманд, узла проверки руля41, узла проверки единицы 42, элемента 42, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ43, одиннадцатого элемента И 44, четвертого элемента НЕ 45, четырнадцато- .го элемента И 46, второго триггера 1547, двенадцатого 48 и триннадцатого49 элементов И, седьмого элементаИЛИ 50, четвертого элемента И 51 итриггера фиксации сбоя 52.Микрокоманды считываются иэ блока 20памяти 11 в регистр микрокоманд 12по сигналу в операционный блок 17,который осуществляет необходимые преобразования инФормации и, кроме тогсконтролируют правильность их выполнения. Правильность считывания изблока памяти 11 в регистр 12 такжеконтролируется блоком 17.Информация с выходов полей 14 и15 используется для Формирования адреса следующей микрокоманды. При этомполе ветвлений 14 используется в зависимости от состояния разряда 16. Влинейных микрокомандах значение разряда 16 равно 0 и поля 14 и 15 совместно образуют адрес следующей микрокоманды. При этом сигналы с поля 14через элементы И 6, ИЛИ 7 поступаютпо тактовому импульсу с выхода 23операционного блока 17 в старшиеразряды регистра адреса 10, в младшие разряды которого через элементыИ 8 и ИЛИ 9 записывается информацияс поля 15 регистра микрокоманд 12.В микрокомандах ветвления значение разряда 16 равно единице, а в лоле 14 записаны код логических условий. Поэтому через элементы ИЛИ 2 иНЕ 4 блокируется запись информации врегистр адреса 10 с выхода поля 14,Код логических условий и сигналы логических условий поступают на входыпервого узла ветвления 25 с поля 14и выхода 20 операционного блока 17соответственно. С выхода узла 25 кодзначений логических условий черезэлемент ИЛИ 9 записывается в регистрадреса 10, модиФицируя тем самымадрес следующей микрокоманды в соответствии со значениями логическихусловий,Выполнение команды разделено на 60два цикла. Один цикл выборки и адресных преобразований, который является общим для всех команд, и циклисполнения команд, который включаетразличные микропрограммы для разных. б 5 команд. В конце ццкла выборки код операции передается в регистр 26 и операционный блок 17 возбуждает сиг нал на выходе 19 начала операции. При этом содержимое регистра 26 через элементы И 5, ИЛИ 7 записывается в старшие разряды регистра адреса 10. После этого начинает выполняться микропрограмма цикла исполнения команды.В конце микрокоманды цикла исполнения операционный блок 17 возбуждает сигнал конца операции на выходе 18, который сбрасывает регистр адреса 10 и осуществляет переход к выполнению микропрограммы цикла вы" борки следующей команды.Сигналами с выходов 18 и 19 операционного блока 17 блокируется запись в регистре адреса 10 с регистра микрокоманд 12 и осуществляется либо прием информации из региСтра 26, либо установка регистра адреса 10 в нуль соответственно, Для возбуждения сигналов на выходах 18 и 19 операционного блока 17 используются Фиксированные значения кодов ветвления. Контроль микропрограммы осущест-вляется следующим образом, В начале линеной микроподпрограммы в счетчик 40 записан код числа микрокоманд в последовательности, который затем уменьшается на единицу с каждой следующей микрокомандой. В предпоследней микрокоманде последовательности в счетчике 40 записана единица, Если следующей выполняется микрокоманда ветвления, что подтверждается единицей в разряде 16 регистра микрокоманд 12, то сигнал сбоя отсутствует. При любом другом порядке появления единицы в счетчике .и единицы в разряде 16 Формируется сигнал сбоя. Таким образом осуществляется оперативный контроль каждой линейной микроподпрограммы.Контроль правильности реализации переходов осуществляется следующим образом, В микрокоманде ветвления к содержимому счетчика прибавляется, код логических условий ветвления. В первой микрокоманде следующей последовательности к содержимому счетчика 40 прибавляется уменьшенный на единицу код числа микрокоманд в последовательности и вычитается увеличенный на единицу код логических условий. Поэтому при правильной реализации ветвления в счетчике 40 остается код числа микрокоманд в пос ледовательности, а при оШибочной код, отличный от кода числа микро- команд в последовательности, что будет обнаружвно при контроле числа микрокоманд в микрокоманде ветвления, либо в микрокоманде линейной последовательности, следующей за той,765809 в которой содержимое счетчика 40 равно единице.Для идентификации места сбоя между линейной последовательностью и переходом служит дешифратор 38, который включается в работу по сигналу обнаружения ошибки. Дешифратор ана лизирует содержимое счетчика 40 и в случае, если код счетчика соответствует одной из возможных разностей кодов логических условий (соответствующих ошибочным переходам) 0 выдает в операционный блок 17 признак ошибочного перехода. Если же код счетчика не соответствует ошибочному переходу, то, следовательно, сбой произошел во время реализации данной ли" 15 нейной последовательности. В зави- симости от одного из двух возможных результатов диагностирования операционный блок 17 выдает команду на повторение микропрограммы, начиная либо с конкретной линейной последовательности, либо организует повторную реализацию ошибочного перехода. Это позволяет реализовать оперативный контроль микропрограммного процессора в процессе реализации операции.Рассмотрим Функционирование аппаратуры контроля процеосора.В первой микрокоманде микроподпрограммы из поля ветвления 14 регистра микрокоманд 12 через элементы 30 И 34, ИЛИ 36, и сумматор 39 в счетчик 40 записывается уменьшенный на единицу код числа микрбкоманд в этой последовательности. В каждой следующей микрокоманде через элементы ИЛИ 35 33 и 36 и сумматор 39 от содержимого счетчика 40 вычитается единица, срабатывает узел проверки единицы 42, который устанавливает в единицу второй триггер 47, который открывает 4 О элементы И 44 и 48.В последней микрокоманде, в которой осуществляется ветвление, из счетчика 40 единица не вычитается, а с выхода второго узла ветвления 32 через элемент И 35 открытый сигна лом с выхода разряда 16 регистра микрокоманд 12, элемент ИЛИ 36 и сумматор 39 добавляется код ветвящих разрядов адреса. Одновременно по сигналу с выхода разряда 16 регистра микрокоманд 12 через элемент И 44 второй триггер 47 устанавливается в нуль, блокируя Формирование сигнала сбоя.Первая микрокоманда каждой микропрограммы определяется по состоянию перчого триггера 30. Если триггер установлен в единицу, то этим идентифицируется первая после ветвления микро- командаЕсли же второй триггер 40 находится в нуле, то в поле ветвления Щ 14 регистра микрокоманд 12 содержится либо код ветвления (при единичном значении разряда 16 регистра микро- ,команд 12) либо старшие разряды адре,:а следующей микрокоманды (при нуле- ч вом значении разряда 16 регистра микрокоманд 12), Установка первого триггера 30 в единицу осуществляется потактовому импульсу и единичному сигналу с выхода разряда 16, которыеоткрывают элемент И 27. В следующеймикрокоманде после ветвления через от.крытый в этом такте элемент И 28 первый триггер 30 устанавливается в нуль.В первой микрокоманде следующеймикроподпрограммы, к которой произошел переход, из содержимого счетчика40 вычитается увеличенный на единицукод логических условий и добавляетсяуменьшенное на единицу число микрокоМанд в этой микроподпрограмме. Этаинформация поступает из поля ветвления 14 регистра микрокоманд 12 черезэлементы И 28, ИЛИ 29. Далее при отсутствии сбоев процессор Функционирует аналогично описанному выше.В последней микрокоманде последней микроподпрограммы в разряде 16регистра микрокоманд 12 записана единица, При этом из счетчика 40 микрокоманд вычитается единица, он принимает нулевое значение, возбуждаетсясигнал на выходе 19 операционногоблока 17 и происходит переход к микропрограмме цикла исполнения команды.Сбои в процессоре могут возникатьв схемах формирования адреса или всхемах выборки памяти микрокоманд11, а также в первом узле ветвления25.Это приводит к тому, что в. счетчике оказываются записанными коды,отличные от заданных.Перед ветвлением микропрограммыправильным является следующий порядок прохождения микрокоманд: первойвыдается микрокоманда М 1 (предпоследняя в микроподпрограмме), которой соответствует единичный код всчетчике," затем выдается микрокоманда М 2 (последняя в микроподпрограмме), которая имеет единичное значение разряда ветвления 16.Если сбОЙ произошел при выполнении предыдущего данной микроподпрограмме ветвления или в самой микроподпрограмме, то это в Функциональном отношении приводит к следующимтрем случаям:после микрокоманды М 1 не выдается микрокоманда М 2,микрокоманда М 2 выдается раньшемикрокоманды М 1;микрокоманды М 2 и М 1 выдаются одновременно.Рассмотрим работу аппаратуры кон-троля в этих случаях. В первом случае после срабатывания узла 42 устанавливается в единицу триггер 47,Если в следующем такте разряд 16регистра микрокоманд 12 имеет нулевое значение, то сигналом с выхода элемента НЕ 45 элемент И 48открывается и через элемент ИЛИ 50формула изобретения 50 и И 51 триггер фиксации сбоя 52 устанавливается в единицу, блокируетоперационный блок 17 и, кроме того, открывает элемент И 37. Черезэлемент И 37 содержимое счетчика 40поступает в дешиФратор 38 для анализа. Если причиной ошибки являетсяневерный переход, то на выходе дешиФратора 38, соответствующем номеру этого перехода, возникает сигнал, который поступает в операционный блок. Если же содержимое счетчика не соответствует одному из возможных остатков при неверном пе"реходе, то принимается решение о сбоепри реализации данкой линейной последовательности микрокоманд. 15Во втором случае по сигналу с выхода разряда 16 регистра микрокоманд12 срабатывает элемент И 49, открытыйнулевым выходом второго триггера 47и через элементы ИЛИ 50 и И 51 триггер фиксации сбоя 52 устанавливается в единицу. Далее аналогично описанному производится диагностика сбоя.В третьем случае по сигналам с выходов узла проверки единицы 42 и разряда 16, регистра микрокоманд 12 срабатывает элемент И 46, который аналогично описанному устанавливает триггер Фиксации сбоя 52 в единицу и работа устройства повторяется,Диагностирование осуществляетсяописанным выше способом,В предпоследней микрокоманде последней микроподпрограмьы счетчик 40устанавливается в единицу, а в последней микрокоманде с выхода 16 ре- З 5гистра микрокоманд 12 поступает сигнал метки, поэтому схема контроляне срабатывает и устройство переходитк следующему циклу работы.Отсутствие сигнала на шинах 22 4 Оначала операции и 24 конца операции.при равенстве нулю счетчика 40 воспринимается как сбой аппаратуры. Кроме того, сигналы отрицательного знака счетчика 40 и переполнения сумматора 39, которые поступают на первые .два входа элемента ИЛИ 50 также воспринимаются, как сбой.Элемент ИСКЛЮЧИИЯЕЕ ИЛИ 43 возбуждается либо, когда содержимоесчетчика 40 микрокоманд равно нулю,но нет сигналов на шинах 22 и 24,либо в противоположном случае.Таким образом, введение в процессор дешиФратора, второго триггера,узла проверки единицы и указанных 55связей позволяет существенно повыситьоперативность, и глубину диагностирования.По сравнению с устройством, описанным в основном авторском свидетельстве, проверяется правильность Функционирования после реализации каждой микроподпрограммы, а не всей микропрограммы.Кроме того, оперативно выявляется и место возникновения сбоя при реализации линейной части микропрограммы, либо при ветвлении, что облегчает процесс восстановления информации и уменьшает время поиска неисправности. Микропрограммный процессор поавторскому свидетельству У 535567,о т л и ч а ю щ и й с я тем, что,с целью повышения надежности устройства, в него дополнительно введенвторой триггер, узел проверки единицы, дешифратор, четвертый элемент НЕ и с десятого по .четырнадцатый элементы И, причем выход дешифратора соединен с четвертым входомоперационного блока, вход дешифратора соединен с выходом десятогоэлемента И, первый вход которого соединен с единичным выходом триггерафиксации сбоя, второй вход десятогоэлемента И соединен с выходом счетчика микрокоманд и с входом узла проверки единицы, первый вход одиннадцатого элемента И соединен с единичным выходом второго триггера и с первым входом двенадцатого элемента И,нулевой выход второго триггера соединен с первым входом тринадцатого элемента И, второй вход которого соединен с первым входом четырнадцатогоэлемента И, с вторым входом одиннадцатого элемента И, через четырнадцатыйэлемент НЕ с вторым входом двенад-цатого элемента И и с третьим выходомрегистра микрокоманд, выход узла про,верки единицы соединен с единичнымвыходом второго триггера и с вторымвходом четырнадцатого элемента И,выход которого соединен с дополнительным четвертым входом седьмого элемента ИЛИ, пятый дополнительный входкоторого соединен с выходом тринадцатого элемента И, дополнительныйшестой вход седьмого элемента ИЛИсоединен с выходом двенадцатого эле"мента И, третий вход которого соединен с третьим входом одиннадцатогоэлемента И и с первым входом счетчи"ка микрокоманд,нулевой вход второготриггера соедийен с выходом одиннадцатого элемента И.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 535567, кл. 6 06 Г 15/00, 1971765809 Составитель Г. ПономареваРе акто Е. Гонча Тех е Ж.Кастелевич Ко екто ек ПодписноеНИ ого комитета СССРний и открытий11 Ра ская наб. д. 4 5лиал ППП Патент , г. Ужгород, ул. Проектная, 4 Заказ 6510/45В

СмотретьЗаявка

2681280, 09.11.1978

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 23.09.1980

Код ссылки

<a href="https://patents.su/6-765809-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Арифметико-логическое устройство связного процессора

Следующий патент: Цифровой коррелометр

Случайный патент: Способ получения безмасляных алкидных смол