Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

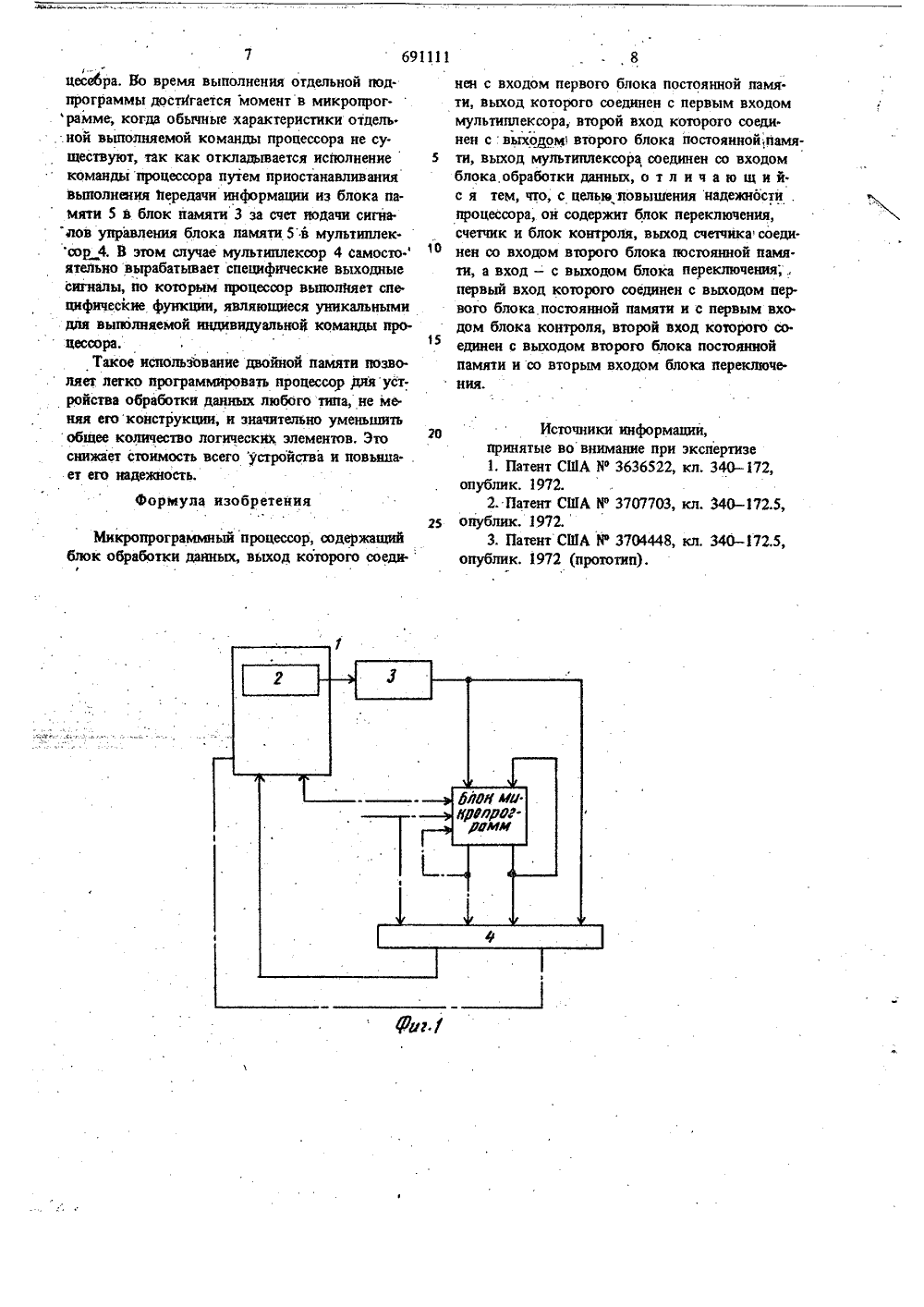

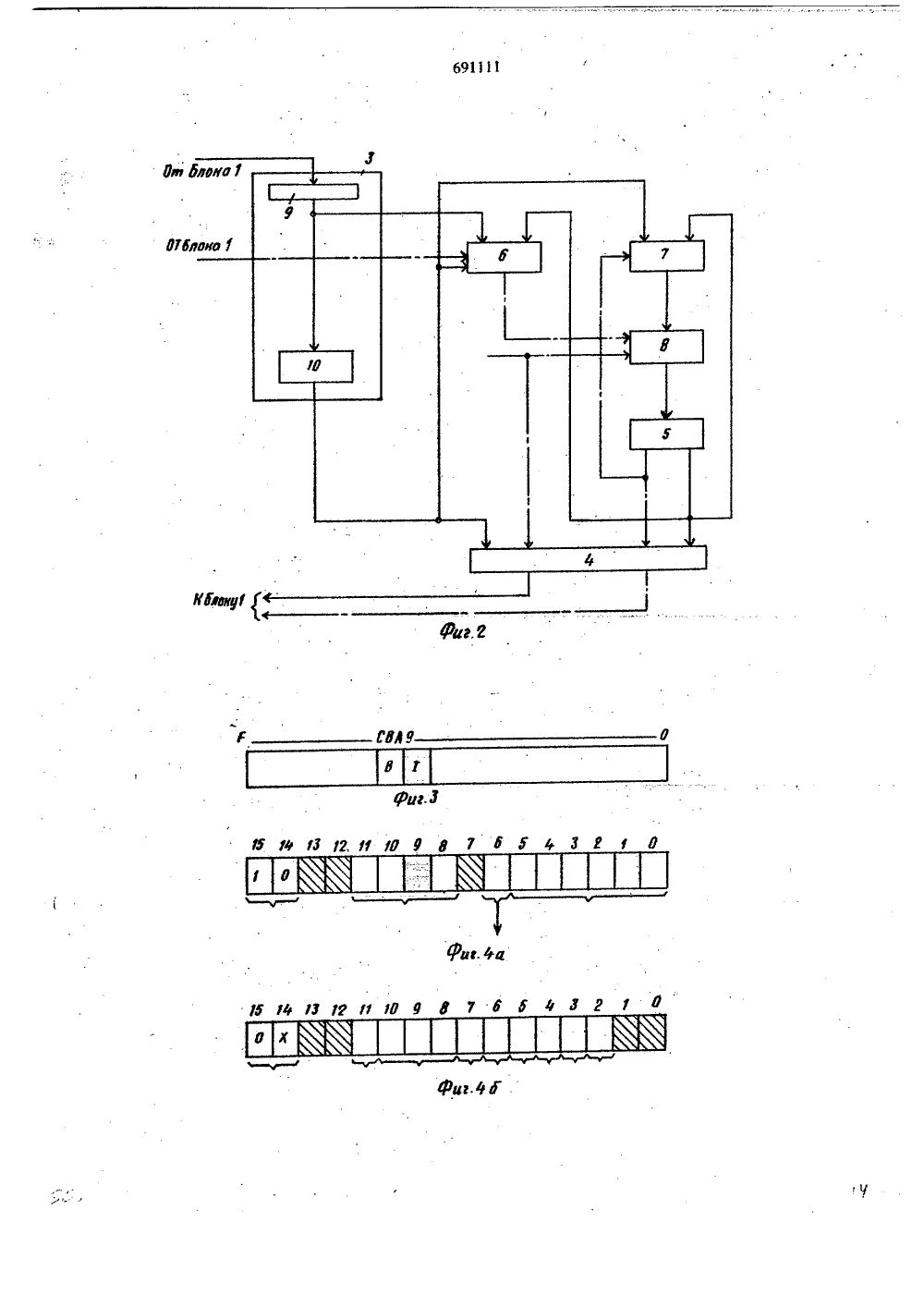

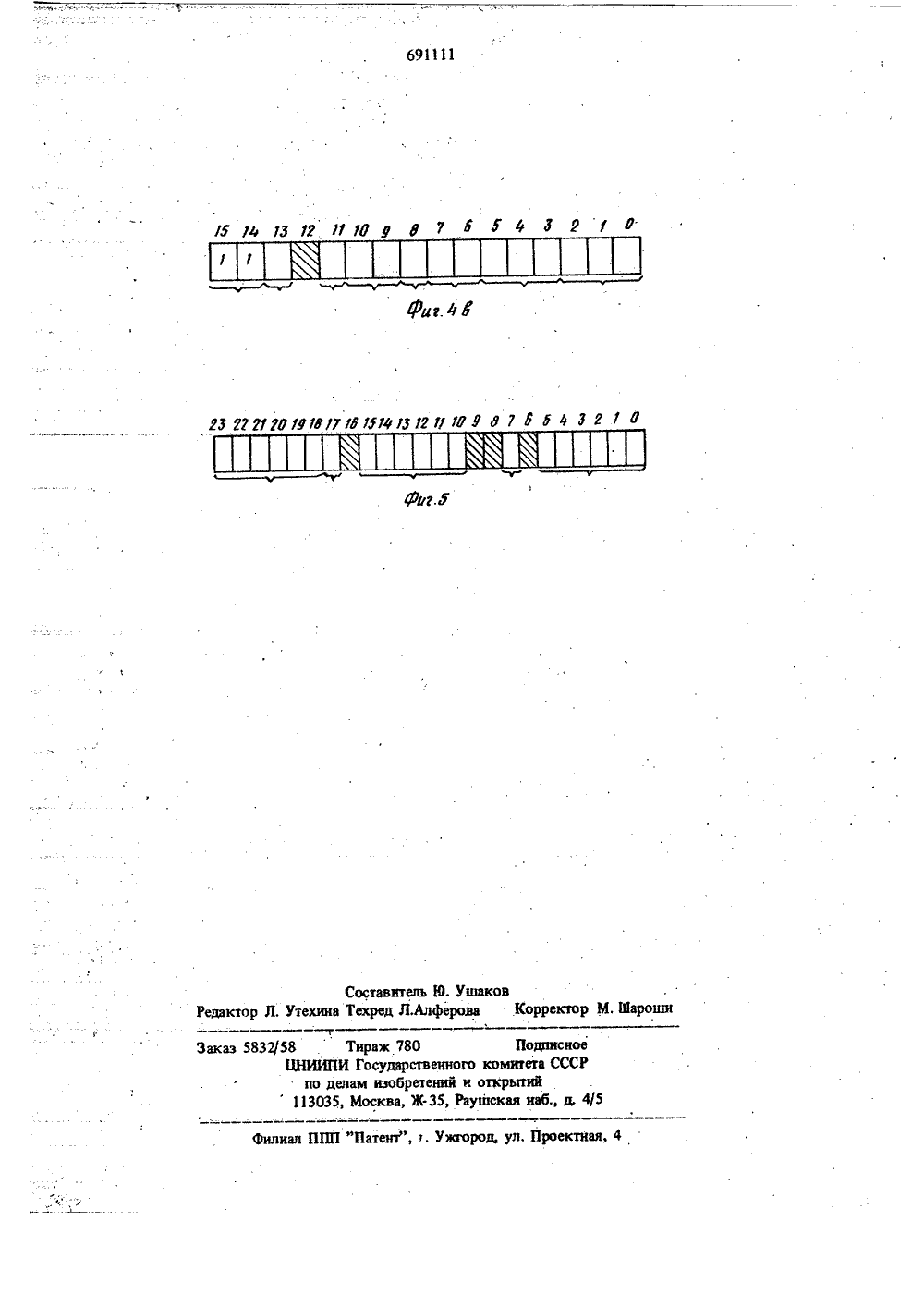

в 69111 Союз Соеетскнх Соцналнстнческнх Респубпнк(32) 14,12,72 Гювударстввииий квмвт СССР вв двяам извбрвтвиая и вткрмткя(72) Авторы изобретения Иностранныорс Копли и Ричард Кент Девис(США) Иностранная фирмаженерал Электрик Компани" (СЮА) 1) Заявител) МИКРОПРОГРАМ Й ПРОЦЕССОР ако наступает мо не имеют общих различные функ бует введения д к Наиболее близким техническим решением кизобретению является микропрограммный процессор, содержащий блок обработки данных, вы.ход которого соединен со входом первого блокапостоянной памяти, выход которого соединен спервым входом мультиплексора, второй входкоторого соединен с выходом второго блока постоянной памяти, а выход мультиплексора соединен со входом блока обработки данных 13.Недостатком известных микропрограммныхпроцессоров является их низкая универсальностьиз-за введения дополнительных логических бло.ков и элементов, что уменьшает надежность всего устройства,Целью изобретения явл е надежности микропрогра ра,яется повышены ммного процессо Изобретение относится к области вычислительной техники и предназначено для управления работой различных устройств обработки данных, в том числе для управления памятью вычислительных машин (ВМ) .Известны микропрограммные процессоры, содержащие блок постоянной памяти для хране. ния необходимых микропрограмм, блок обра. ботки данных и мультиплексоры 1 и 12.Процессор 11 содержит последовательно расположенную микропрограмму, в результате чего ее можно выполнить только через множес 1- во подпрограмм, а зто требует либо большой ем: кости блока постоянной памяти, либо введения нескольких дополнительных блоков памяти для хранения управлаощих слов,.Процессор (2 содержит дополнительный ло. гическнй блок с памятью, что позволяет несколько уменьшить емкость. блока постоянной памяти, каждая подпрограмма которого может частично регулировать выполнение нескольких команд, имеющих общие характеристики выполнения. Од. мент, когда новые команды ужрактеристик, т.е. выполняютв обработке данных, что трелнительных логйческих бло691111 1 О 3Поставленная цель достигается тем, что впрецложенный микропрограммный процессорвведены блок переключения, счетчик и блокконтроля, Выход счетчика соединен со входомвторого блока постоянной памяти, а вход -с выходом блока переключения, первый входкоторого соединен с выходом первого блока,постоянной памяти и с первым входом блокаконтроля, второй вход которого соединен с вы;ходом второго блока постоянной памяти и совторым входом блока переключения.. На фиг, 1 приведена общая структурнаясхема микропрограммного процессора; на фиг.2 - его развернутая структурная схема; на фиг.3 - 5 - варианты распределения управляющейинформации в различных блоках микропрограммного процессора,Микропрограммный процессор содержит блокобработки данных 1, включающий блок оперативной памяти 2, первый блок постоянной памя ти 3, мультиплексор 4, второй блок постояннойпамяти 5, блок контроля 6, блок переключения7 и счетчик 8 (на чертежах информационныешины показаны сплошными линиями, а шиныуправления - пунктирными) .Блок обработки данных 1 можетпредставлять собой законченную ВМ, номожетсостоятьи иэ регистра адреса, регистра. счетчика, арифме.тичессого регистра, блока вычислений и блокасйнхронизации. В этом случае регистр адресапринимает адрес команды иэ блока вычисленийили из блока синхронизации и управляет бло.ком памяти 2. Регистр-счетчик считает количество сдвигов выполняемых блоком 1, и можетбыль загружен либо из блока памяти 2, либо изблока синхронизации. Блок вычислений выполняет арифметические ойераций и передачи от регистра к регистру, а арифметический регистр перемещает ряд битов во время выполнения командсдвига и временно хранит информацию блокапамяти 2,Формат командного слова в блоке памяти 2показан на фиг, 3, Биты от А до Е являютсявходными для первого блока памяти 3, когда 4команда извлекается блоком 1, Биты от С до Еопределяют команду (сложение, вычитание и т.д.),Бит В используется для обозначения того, чтообласть адреса команды (биты от 0 до 9) будетиндексирована, а бит А - для обозначения того,что область адреса команды является индексом.Адресование и индексирование области адресакоманды ьюжет быль установлено одновременно битами А и В.Командная информация (биты от А до Е)удерживаютСя в регистре 9 внутри блока памяти3 для адресации к требуемым ячейкам памятинакопителя 10,4При адресации. первого блока постоянной па. мяти 3 вырабатываются индексы и сигналы к блоку памяти 5 и мультиплексору 4, который вырабатывает информационные и управляющие сигналы для блока 1. Каждая ячейка памяти блока памяти 5 содержит определенное микропрограммное управляющее слово, которые в совокупности составляют микропрограмму, которая должна быль выполнена всем процессо.ром путем регулярного генерирования выходныхсигналов из мультиплексора 4 на вход блока 1.Микропрограммные управляющие слова бло. ка памяти 5, могут быть трех типов: развет. вляющиеся (фиг, 4 а), операционное (фиг 4 б) и ввода-вывода (фиг, 4 в).Разветвляющееся управляющее слово используется во время выполнения микропрограмм, чтобы вызвать селективное адресование блока памяти 5, основанное на обработке различных управляющихсигналов (условий состояния) в блоке 1 и в блоке переключения 7. Биты "14" и "15" этого слова представляют собой опера. ционный код и передаются в виде управляющих сигналов с выхода блока памяти 5 к блоку пе. реключения 7, который декодирует этот код, Биты от "8" до "11" образуют область проверки, которая также формирует управляющие конт. рольные сигналы к блоку переключения 7. Эти сигналы сравниваются с сигналами состояния из блока 1, чтобы вызвать генерирование либо разветвляющегося, либо последовательного адреса к блоку памяти 5.Разветвляющийся адрес к собстЬенной области разветвляющегося управляющего слова содер.жит биты от "О" до "5", Эти биты передаются на второй вход блока переключения 7 в видесигналов адреса. Бит "6" регулирует селектив. ное адресование и создает замедление сигналовадреса к блоку перключения 7 для определения того, должны быль использованы биты от "0 до "5" или сигналы с первого входа блока пе.реключения 7, поступившие с выхода блока па.мяти 3 (биты от "18" до "23" фиг. 5), Биты"7", 12" и "13" разветвляющегося управляюще.го слова в данном устройстве не используютсяОперационное управляющее слово испольэу.ется для генерирования выходных сигналов муль.типлексора 4 для управления обработкой данныхвнутри блока 1; Биты "14" и "15" этого слова(фиг. 4 б) аналогичны битам "14" и "15" развет.вляющегося управляющего слова. Кроме того, ониуправляют мультиплексором 4 для многократнойпередачи сигналов к блоку 1. Биты "8", "9" иБит "11" обозначает гашение счетчика 8 и используется блоком переключения 7 для восста.тновления адреса блока памяти 5.Биты "0", "1", "12" и "13" операционногоуправляющего слова не используются. 5Управляюшее слово ввода-вывода используется для управления выполнением микропрограммы обращения блока 1 к блоку памяти 2,Биты "14" и "15" этого слова (фиг.4 в) аналогйчны битам "14 и "15" разветвляющегося иоперационного управляющих слов. Биты от "0"до "5" определяют источник адреса блока па.мяти 2, причем биты от "О до "2" являютсябитами непосредственной адресации от мульти.плексора 4 для индексирования или модификации в регистре. счетчике блок 1,а биты от "3"до "5 выбирают в качестве источника адресаили регистр адреса, или другой блок после обработки сигналов с выхода блока памяти 3(биты от "10" до "15" фиг. 5), Бит "13" управляет загрузкой регистра-счетчика через мультиплексор 4 от ячейки памяти, непосредственноадресуемой битами от "0" до "2", Биты "9"и "10" определяют операцию записи или считывания при обращении к блоку памяти 2. Биты"6" и "7" декодируются .мультиплексором 4 ипереводят блоки, взаимодействующие с блоком1, в режим приема или выдачи информации,Бит "8" создает замедление передачи сигналовв мультиплексоре 4 от битов "6" и "7" к битуЗо"17" (фиг, 5) командного управляющего словаблока памяти 3, Бит "11" служит для гашениясчетчика 8 аналогично биту "11" операционно.го управляющего слова,Формат командного управляющего слова, ко 35торое содержится в блоке памяти 3 показан нафиг. 5, Эти слова имеют содержание, присущеекоманде, выполняемой всем микропрограммнымпроцессором, и дополняют микропрограммы,находящиеся в блоке памяти 5, Биты от "18"до "23" этого слова содержат разветвляющийсяадрес, который вызывает выполнение подпрог.раммы микропрограммы для управления выпол.пением конкретной команды процессора в соот 45ветствии с кодом адреса блока памяти 3, Бит"17" используется для управления передачейинформации между блоком памяти 2 и либоарифметическим регистром, либо регистром. счетВкком в блоке 1. Биты от "10" до "15" исполь 50зуются мультиплексором 4 для непосредственной адресации указанной ячейки индекса в бло.ке памяти 2 через блок 1, Бит "7" использует.ся блоком переключения 7 для управления адресацией блока памяти 5 к требуемой ячейке не.посредственно от Ювка памяти 2. Биты от 055до "5" образуют код операции, выполняемойв блоке 1 блоком вычислений, аналогично ра.нее описанному в операционном. управляющем слове, Код операции используется мультиплексором 4 для многократного повторения командыв блоке 1. Однако, кроме ранее описанных опе.раций, он позволяет ввести дополнительные операции командного управляющего слова в блокепамяти 3,Необходимо отметить, что регистр 9 в блокепамяти 3, получив командную информацию отблока памяти 2, передает далее эту информациюв накопитель 10, где она дешифрируется и выбирает требуемую ячейку памяти, и в блок,контроля 6, Последний после соответствующейобработки этих сигналов н сигналов от блока1 и накопителя 10 и блока памяти 5 либо загружает счетчик 8 через блок переключения 7, либодает счетчику 8 единичное приращение, осущест.вляя последовательную выборку ячеек памятиблока памяти 5. При этом блок контроля сравнивает биты от А до Р регистра 9 (фиг, 3)и биты от "8" до "11" и "14", "15" разветвляющегося управляющего слова (фиг. 4 а) блокапамяти 5,Таким образом, блок памяти 3 является до.полнительным микродекодирующим блоком исодержит множество командных управляющихслов, соответствующих командам микропрограм.много процессора Он может непосредственносоединяться с блоком памяти 2 или с блоком1 для получения текущей информации, котораяиспользуется им, чтобы выборочно адресоватьпоследнее для выполнения считывания командное управляющее слово. Во время выполненияопределенных команд микропрограммным про.цессором блок памяти 3 при управлении бло.ком памяти 5 вырабатывает для него управля.ющую информацию, чтобы вызвать ветвлениеадресов к начальным ячейкам, присущим отдельным подпрограммам микропрограммы, выполняемой процессором,Блок памяти 5 содержит микропрограммныеуправляющие слова, образующие микропрограм.му. Он связан с блоком переключения 7, кото.рый обеспечивает последовательное или выборочное адресование к нему и от блока памяти 3в ответ на управляющую информацию блока памяти 5 и на различные условия состояния и сигналы, подаваемые к блоку переключения 7.Оба блока постоянной памяти управляютмультиплексором 4, который вырабатывает управляющие и информационные сигналы к блоку1 в соответствии с выполняемой командой имюсропрограммным управляющим словом.Это позволяет значительно уменьшить коли.чество дополнительных логических элементов и .уменьшить общую емкость постоянной памятиза счет наличия в блоке памяти 5 микропрограмм,состоящих из множества подпрограмм, каждаяиэ которых связана с множеством команд про 1Iцесе 6 ра. Во время выполнения отдельной подпрограммы достйгается момент в микропрограмме; когда обычные характеристики отцель. ной выполняемой команды процессора не существуют, так как откладывается исполнение команды процессора путем приостанавливания выполнения передачи информации из блока памяти 5 в блок памяти 3 за счет подачи сигна.лов управления блока памяти 5 в мультиплексор 4, В этом случае мультиплексор 4 самосто- ятельно вырабатывает специфические выходные сигналы, по которым процессор выполйяет спе.цифическне функции, являющиеся уникальными для выюлняемой индивидуальной команды процессора.Такое использование двойной памяти позво.ляет легко программировать процессор ваяя уСтройства обработки данных люббго типа, не ме.няя его конструкции, и значительно уменьшить общее количество логических элементов, Это снижает стоимость всего устройства и повьнпа.ет его надежность. Микропрограммный процессор, содержащийблок обработки данных, выход которого соеди. Р нен с входом первого блока постоянной памяти, выход которого соединен с первым входом мультиплексора, второй вход которого соеди.нен с выходом второго блока постоянной;.памя ти, выход мультиплексора соединен со входомблока обработки данных, о т л и ч а ю щ и й.с я тем, что, с целые повышения надежности .процессора, он содержит блок переключения, счетчик и блок контроля, выход счетчика соединен со входом второго блока постоянной памяти, а вход - с выходом блока переключения;., первый вход которого соединен с выходом пер.ного блока постоянной памяти и с первым вхо.дом блока контроля, второй вход которого соединен с выходом второго блока постоянной памяти и со вторым входом блока переключения. Источники информации,принятые во внимание при экспертизе1. Патент США Иф 3636522, кл, 340 - 172,опублик. 1972.2. Патент США йо 3707703, кл. 340-172.5,25 опублик, 1972,3. Патент США Р 3704448, кл. 340-72,5,опублик, 1972 (прототип),691111 7 Ю Х Ф 8 Р 1413 12 11 1 Ю У Ю 7 Ф Ю 4 Я 2 1 Составитель Ю. УшаковУтехина Техред Л.Алферова .Ко М, Шароши едакто иал ППП "Патент", . Ужгород, ул, Проек Зф 58 Тираж 780 Подписное ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж, Раушская иаб., д. 4/5

СмотретьЗаявка

1979797, 13.12.1973

Иностранцы, Джеймс Вудворс Конли и Ричард Кент Девис, Иностранная фирма "Дженерал Электртк Компани"

ДЖЕЙМС ВУДВОРС КОНЛИ, РИЧАРД КЕНТ ДЭВИС

МПК / Метки

МПК: G06F 9/16

Метки: микропрограммный, процессор

Опубликовано: 05.10.1979

Код ссылки

<a href="https://patents.su/6-691111-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Материал для проявления электростатографических изображений

Следующий патент: Устройство для считывания информации

Случайный патент: Способ определения мгновенной скорости движения тел, например горячего проката