Устройство для обнаружения и коррекции ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1783583

Автор: Емельяненко

Текст

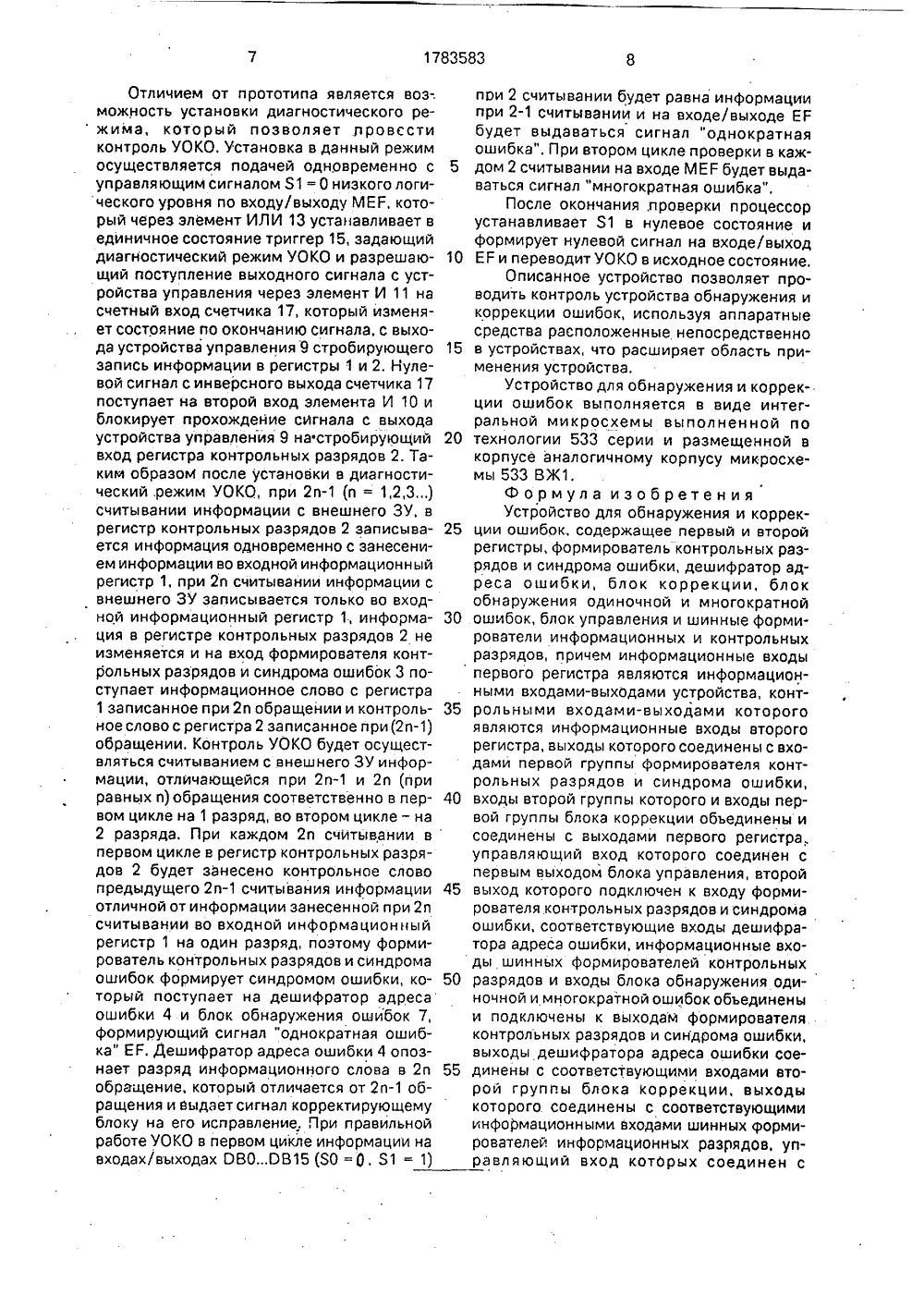

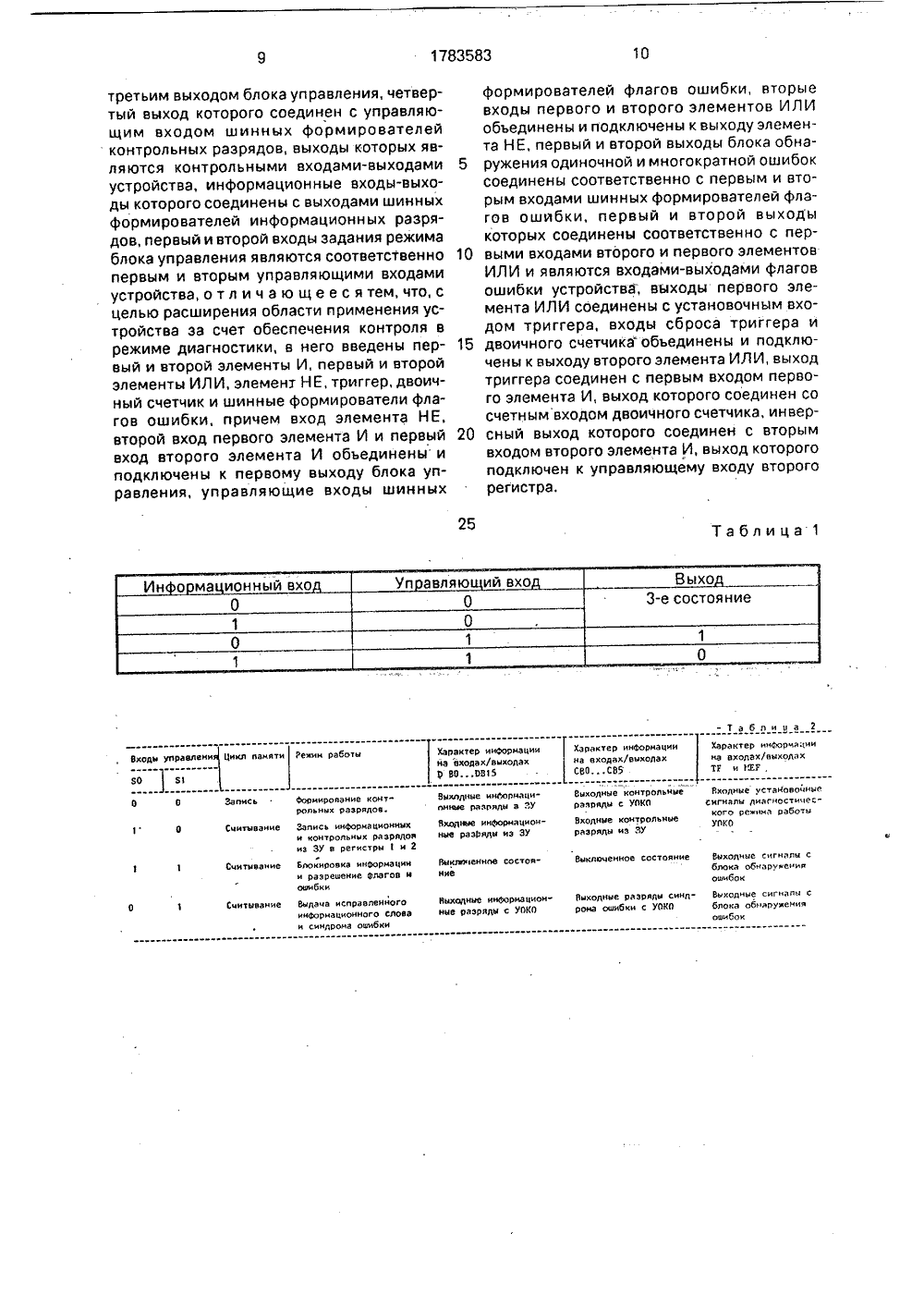

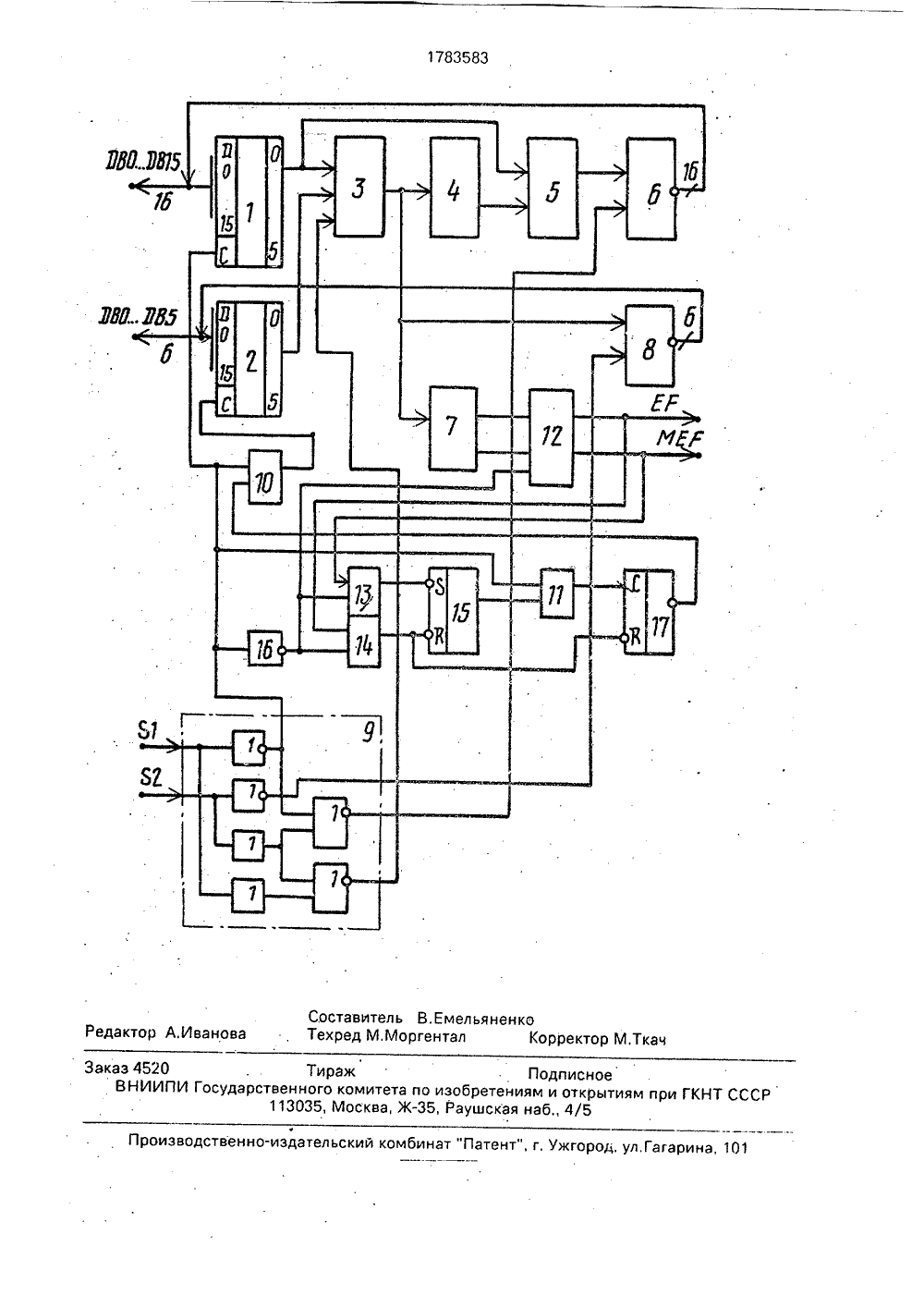

союз сОВетсихСОЦИАЛИСТИЧЕСКИХРЕСПУбЛИК 1783583 А 1 5 6 11 С 29/ ИСАНИЕ ИЗОБРЕТЕНеееВ устрой решен и ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР ТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Микросхема М 1804 ВЖ 1 бк. 0.347.328-06 ТУ. Техническое описание И 93.480.004-01 Т 07.Микросхема 533 ВЖ 1 бк, 0,347,141 ТУ 41, Руководство по применению микросхем серии 533. ОСТ 11.340.917-84, с. 140-152. (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК(57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Цель изобретения - расширение области применения устройства за счет обеспечения контроля в режиме дйагностиИзобретение относится к вычислительной технике и может быть использовано в блоках контроля запоминающих устройств,Известно устройство обнаружения и коррекции ошибок, содержащее, регистр входных данных, регистр контрольных данных, регистр режима диагностики, регистр входных данных, буфер входных контрольных данных, генератор признаков ошибки, формирователь данных, устройство управления, дешифратор признаков ошибки.Недостатком данного устройства является большое количество выходов (48), в том числе восемь выходов управляющих команд, определяемых внешним устройством управления, что приводит к усложнению устройства.Из известных ств наиболее близким техническим ем к данному изоки. Для достижения цели в устройство обнаружения и коррекции ошибок, содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, блок обнаружения одиночной и многократной ошибок, дешифратор адреса ошибки, блок коррекции, блок управления и шинные формирователи информационных и контрольных разрядов, вводятся элемент НЕ, триггер, первый и второй элементы И, первый и второй элементы ИЛИ, двоичный счетчик и шинные формирователи флагов ошибок. Ввод данных элементов позволяет при считывании внешйей информации и занесении ее во входные-регйстры осуществить контроль цепей коррекции ошибок изменением алгоритма занесения информации в регистр контрольных разрядов, 1 ил. бретению является устройство обнаружения и исправления ошибок содержащее, входные регистры и шинные формировате ли, формирователи контрольных разрядов и Ж синдрома ошибок, блок обнаружения оди- Ы ночной и многократной ошибки, дешифра- (Я тор адреса ошибки, корректирующий блок и Со блок управления, 6 дНедостатком этого устройства является отсутствие возможности контроля устройств в режиме диагностики, что приводит к усложнению запоминающих устройств в которых применено данное устройство и снижает надежность данных запоминающих устройств.Целью изобретения является расширение области применения устройства за счет введения возможности контроля устройства в режиме диагностики.Поставленная цель достигается тем, что в устройство обнаружения и коррекции ошибок. содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, .дешифратор адреса ошибки, блок коррекции, блок обнаружения одиночной и многократной ошибок, блок сравнения и шинные формирователи информационных и контрольных разоядов, причем информационные входы первого регистра являются информационными входами - выходами устройства, контрольными входами - выходами которого являются информационные входы второго регистра, выходы которого соединены с входами, первой группы формирователя контрольных разрядов и синдрома ошибки, входы второй группы которого и входы первой группы блока коррекции объединены и соединены с выходами первого регистра, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к входу формирователя контрольных разрядов и синдрома ошибки, соответствующие входы дешифратора адреса ошибки, информационные входы шинных формирователей контрольных разрядов и входы блока обнаружения одиночной и многократной ошибок объединены и подключены к выходам формирователя контрольных разрядов и синдрома ошибки, выходы дешифратора адреса ошибки соединены с соответствующими входами второй группы блока коррекции, выходы которого соединены с соответствующими информационными входами шинных формирователей информационных разрядов, управляющий вход которых соединен с третьим выходом блока управления, четвертый выход которого соединен с управляющим входом шинных формирователей контрольных разрядов, выходы которых являются контрольными входами - выходами устройств, информационными входами - выходами которых являются выходы шинных формирователей информационных разрядов, первый и второй входы задания режима блока управления являются соответственно первым и вторым управляющими входами устройства и введены элементами И, ИЛИ, НЕ, триггер с установочными входами, двоичный счетчик и шинные формирователи флагов ошибки, причем управляющие входы шинных формирователей соединены с выходом элемента НЕ вход которого соединен с первым выходом устройства управления, информационные входы первого и второго шинного формирователя соедйнены соответственно с первым и вторым выходом блока обнаружения одиночной и многократной ошибок,а выходы шинных формирователей флаговошибки соединены с выходами устройствафлагов ошибки ЕР и МЕР и с первыми входами соответственно первого и второго эле 5 мента ИЛИ, вторые входы которыхсоединены с выходом элемента НЕ, выходпервого элемента ИЛИ соединен с установочным входом триггера, вход сброса которого соединен с выходом второго элемента10 ИЛИ и с входом сброса счетчика, счетныйвход которого соединен с выходом первогоэлемента И первый вход которого соединенс выходом триггера, а второй вход соединенс первым выходом устройства управления и15 с первым входом второго элемента И, второй вход которого соединен с инверснымвыходом счетчика, а выход второго элемента И соединен со стробирующим входомрегистра контрольных разрядов,20 Рассмотрение показало, что предложенное техническое решение в сравнении спрототипом обладает новыми отличительными признаками, что доказывает соответствие заявляемого решения критерию25 "новизна".Введение новых элементов И, ИЛИ, НЕ,триггера с установочными входами, двоичного счетчика, шинных формирователей вуказанной связи с другими элементами схе 30 мы позволяет получить новое свойство осуществления возможности контроляустройства в режиме диагностики, что доказывает соответствие технического решениякритерию "существенное отличие",35 На чертеже представлена функциональная схема предлагаемого устройства,Устройство содержит; входной информационный регистр 1, регистр контрольныхразрядов 2, формирователь контрольных40 разрядов и синдрома ошибок 3, дешифратор адреса ошибок 4, блок коррекции 5,шинные формирователи информационныхразрядов 6. блок обнаружения одиночных имногократных ошибок 7, шинные формиро 45 ватели контрольных разрядов 8, устройствоуправления 9, первый и второй элементы И10 и 11, шинные формирователи флаговошибки 12, элементы ИЛИ 13 и 14, триггерс установочными входами 15, элемент НЕ50 16, двоичный счетчик 17, информационныевходы/выходы ОВООВ 15, входы/выходыконтрольной информации СВОСВ 5, входы/выходы флагов ошибки ЕР и МЕР, управляющие входы ЯО и 31.55 Входной информационный регистр 1 ирегистр контрольных разрядов 2 предназначены для приема информации поступающей по входам/выходам ОВООВ 15 иСВОСВ 5 с внешних запоминающих устройств.Формирователь контрольных разрядови синдрома ошибок 3 осуществляет в циклезаписи формирование контрольных разрядов, поступающих через шинные формирователи на входы/выходы СВОСВ 5 изинформационных, в соответствии с кодомХэмминга. Каждый контрольный разрядпредставляет собой результат суммирования по модулю два восьми информационных разрядов. В цикле считываниеформируется синдром ошибки в результатесравнения входной информации свернутойпо коду Хэмминга и контрольных разрядов.Дешифратор адреса ошибки 4 осуществляет дешифрации синдрома ошибки, формирует сигнал указывающий ошибочныйразряд и выдает сигнал блоку коррекции наего исправление,Блок коррекции 5 осуществляет коррекцию (инвертирование) ошибочных разрядовинформации занесенной на входной информационный регистр 1 и выдачу откорректированной информации на входные шинныеформирователи.Входные шинные формирователи 6 осуществляют коммутацию информации с выхода блока корректора на входы/выходыОВО.ОС 15 в соответствии с табл, 1 по сигналу с выхода устройства управления,Блок обнаружения одиночной и многократной ошибок 7 формирует сигналы однократной ошибки ЕЕ и многократной ошибкиМЕЕ по результатам анализа синдромаошибки. Входные шинные формирователи 8осуществляют коммутацию информации свыхода формирователя контрольных разрядов и синдрома ошибок на входы/выходыконтрольной информации СВО.СВ 5. Устройство управления 9 осуществляет управление работой устройства обнаружения икоррекции ошибок (УОКО) по входным сигналам 0 и 1 в соответствии с табл. 2,Элементы И 10 и 11, двоичный счетчик17 предназначены для блокировки через обращение записи информации в регистр контрольных разрядов 2. Элементы ИЛИ 13 и14, триггер 15. позволяют переключитьУОКО в диагностический режим. ЭлементНЕ 16 и шинные формирователи 12 осуществляют коммутацию сигналов по входам/выходам ЕЕ и МЕР,Устройство работает следующим образом.По начальной установке процессор устанавливает 31 в нулевое состояние и формирует нулевой сигнал на входе ЕР, которыйчерез элемент 2 ИЛИ 14 производит сбростриггера 15 и счетчика 17. Инверсный выходсчетчика 17 разрешает через элемент И 10прохождение сигнала с выхода устройства5 10 15 20 25 30 35 40 45 50 55 управления 9 на стробирующий вход регистра контрольных разрядов 2 одновременно с сигналов поступающих на стробирующий вход информационного регистра 1, После окончания информационной установки процессор снимает нулевой сигнал на входе ЕР и дальнейшая работа устройства осуществляется аналогично работе прототипа, Устройство работает в двух основных режимах, соответствующих циклам записи и считывания с ЗУ. В цикле записи происходит процесс кодирования, т.е. формирование контрольных разрядов иэ информационных в соответствии с кодом Хэмминга, Каждый контрольный разряд представляет сбйой результат суммирования по модулю 2 восьми информационных разрядов.Сформированные контрольные разряды выдаются на двунаправленную шину и поступают вместе с информационными разрядами в ЗУ. На этом цикл записи заканчивается.В течение цикла считывания информационные и контрольные-разряды с ЗУ заносятся на регистры 1 и 2 (Я 1 = О, 50 -1) и формирователь контрольных разрядов и синдрома ошибок сформирует из содержимого информационного регистра 1 контрольные разряды и сравнит их с контрольными разрядами занесенными в регистр контрольных разрядов 2. Если достигнуто равенство всех шести разрядов, то это означает, что нет ошибок и при ЯО и 31 равным единице, на входах ЕЕ и МЕР не появляются сигналы ошибок.При несовпадении одного или более разрядов в контрольных битах формирователь контрольных разрядов и синдрома ошибок 3 формирует сигнал ошибки который поступает на дешифратор адреса ошибок 4 и блок обнаружения одиночных и многократных ошибок 7. По синдрому ошибок дешифратор адреса ошибок 4 определяет ошибочный разряд информации и выдает сигнал блоку коррекции 5 на исправление (инвертирование) информации поступающей с выхода регистра 1, С выхода блока коррекции 5 информация поступает на вход шинных формирователей 6, который по управляющему сигналу (при ЯО = О, Я 1 = 1) с выхода устройства управления выдает одкорректированную информацию на входы/выходы ОВООВ 15. Кроме того блок обнаружения одиночных ошибок и многократных ошибок 7 формирует сигналы однократной и многократной ошибки, которые поступают на шинные формирователи 12 и по управляющему сигналу (при 31 = 1) с выхода устройства управления 9 выдается на входы/выходы ЕГ и МЕР,Отличием от прототипа является воз-, можность установки диагностического ре жима, который позволяет провссти контроль УОКО. Установка в данный режим осуществляется подачей одновременно с управляющим сигналом 51 = 0 низкого логического уровня по входу/выходу МЕР, который через элемент ИЛИ 13 устанавливает в единичное состояние триггер 15, задающий диагностический режим УОКО и разрешающий поступление выходного сигнала с устройства управления через элемент И 11 на счетный вход счетчика 17, который изменяет состояние по окончанию сигнала, с выхода устройства управления 9 стробирующего запись информации в регистры 1 и 2. Нулевой сигнал с инверсного выхода счетчика 17 поступает на второй вход элемента И 10 и блокирует прохождение сигнала с выхода устройства управления 9 на стробирующий вход регистра контрольных разрядов 2. Таким образом после установки в диагностический. режим УОКО, при 2 п(и = 1,2,3,) считывании информации с внешнего ЗУ, в регистр контрольных разрядов 2 записывается информация одновременно с занесением информации во входной информационный регистр 1, при 2 п считывании информации с внешнего ЗУ записывается только во входной информационный регистр 1, информация в регистре контрольных разрядов 2 не изменяется и на вход формирователя контрольных разрядов и синдрома ошибок 3 поступает информационное слово с регистра 1 записанное при 2 п обращении и контрольное слово с регистра 2 записанное при(2 п) обращении, Контроль УОКО будет осуществляться считыванием с внешнего ЗУ информации, отличающейся при 2 пи 2 п (при равных и) обращения соответственно в первом цикле на 1 разряд, во втором цикле - на 2 разряда. При каждом 2 п считывании в первом цикле в регистр контрольных разрядов 2 будет занесено контрольное слово предыдущего 2 псчитывания информации отличной от информации занесенной при 2 п считывании во входной информационный регистр 1 на один разряд, поэтому формирователь контрольных разрядов и синдрома ошибок формирует синдромом ошибки, который поступает на дешифратор адреса ошибки 4 и блок обнаружения ошибок 7, формирующий сигнал "однократная ошибка" ЕЕ. Дешифратор адреса ошибки 4 опознает разряд информационного слова в 2 п обреение который отличается от 2 побращения и выдает сигнал корректирующему блоку на его исправление, При правильной работе УОКО в первом цикле информации на входах/выходах ОВО.ОВ 15 (30 =О. Я 1 = 1)30 35 40 первым выходом блока управления, второй 45 выход которого подключен к входу формирователя контрольных разрядов и синдрома ошибки, соответствующие входы дешифратора адреса ошибки, информационные вхо 10 15 20 50 55 пои 2 считывании будет равна информации при 2-1 считывании и на входе/выходе ЕЕ будет выдаваться сигнал "однократная ошибка". При втором цикле проверки в каждом 2 считывании на входе МЕЕ будет выдаваться сигнал "многократная ошибка". После окончания проверки процессор устанавливает 31 в нулевое состояние иформирует нулевой сигнал на входе/выход ЕР и переводит УОКО в исходное состояние,Описанное устройство позволяет проводить контроль устройства обнаружения и коррекции ошибок, используя аппаратные средства расположенные непосредственно в устройствах, что расширяет область применения устройства,Устройство для обнаружения и коррекции ошибок выполняется в виде интегральной микросхемы выполненной по технологии 533 серии и размещенной в корпусе аналогичному корпусу микросхемы 533 ВЖ 1,Формула изобретения Устройство для обнаружения и коррекции ошибок, содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, дешифратор адреса ошибки, блок коррекции, блок обнаружения одиночной и многократной ошибок, блок управления и шинные формирователи информационных и контрольных разрядов, причем информационные входы первого регистра являются информационными входами-выходами устройства, контрольными входами-выходами которого являются информационные входы второго регистра, выходы которого соединены с входами первой группы формирователя контрольных разрядов и синдрома ошибки, входы второй группы которого и входы первой группы блока коррекции объединены и соединены с выходами первого регистра, управляющий вход которого соединен с ды шинных формирователей контрольных разрядов и входы блока обнаружения одиночной и многократной ошибок обьединены и подключены к выходам формирователя контрольных разрядов и синдрома ошибки, выходы дешифратора адреса ошибки соединены с соответствующими входами второй группы блока коррекции, выходы которого соединены с соответствующими информационными входами шинных формирователей информационных разрядов, управляющий вход котОрых соединен с-Таблица 2Характер информациина входах/выходахР ВОРВ 15 Входы Управленя цикл памяти ВО В 1 Характер инфорча;1 иина входах/выходахТР и 1 БГ Характер информациина входах/выходахСВОСВ 5 Репин работы Выходные контрольныеразряды с УОКО Входные установочные сигналы Лнагностиче"- кого режима работы УОКО Выходные информационные разряды а ЗУ Фориирование контрольных разрядов. О О Запись Входные контрольныеразряды из ЗУ Входные инфорнационные разРяды из ЭУ Запись информационных и контрольных разряЛоя из ЗУ в регистры 1 и 2 Блокировка информации и разрешение флагов и ошибки 0 Считывание Выключенное состояние Считывание Выходные снгнтлы сблока обнзруяенияошибок Выктззченнпе состояние Выходные сигналы сблока обнруяенияошибок Выдача исправленногоинформационного словаи синлрома ошибки Выхолные разряды синдрома ошибки с УОКО Выходные информационные разряды с УОКО Считывание третьим выходом блока управления, четвертый выход которого соединен с управляющим входом шинных формирователей контрольных разрядов, выходы которых являются контрольными входами-выходами устройства, информационные входы-выходы которого соединены с выходами шинных формирователей информационных разрядов, первый и второй входы задания режима блока управления являются соответственно первым и вторым управляющими входами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения контроля в режиме диагностики, в него введены первый и второй элементы И, первый и второй элементы ИЛИ, элемент НЕ, триггер, двоичный счетчик и шинные формирователи флагов ошибки, причем вход элемента НЕ, второй вход первого элемента И и первый вход второго элемента И объединены и подключены к первому выходу блока управления, управляющие входы шинных формирователей флагов ошибки, вторые входы первого и второго элементов ИЛИ объединены и подключены к выходу элемента НЕ, первый и второй выходы блока обна ружения одиночной и многократной ошибоксоединены соответственно с первым и вторым входами шинных формирователей флагов ошибки, первый и второй выходы которых соединены соответственно с пер выми входами второго и первого элементовИЛИ и являются входами-выходами флагов ошибки устройства, выходы первого элемента ИЛИ соединены с установочным входом триггера, входы сброса триггера и 15 двоичного счетчика объединены и подключены к выходу второго элемента ИЛИ, выход триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом двоичного счетчика, инвер сный выход которого соединен с вторымвходом второго элемента И, выход которого подключен к управляющему входу второго регистра.1783583 Составитель В.Емельяненкоедактор А,Иванова, Техред М.Моргентал Корректор М,Ткач водственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 П Заказ 4520 Тираж Подписное ВНИИПИ 1 осударственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4846102, 02.07.1990

НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ИМПУЛЬС"

ЕМЕЛЬЯНЕНКО ВИТАЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: коррекции, обнаружения, ошибок

Опубликовано: 23.12.1992

Код ссылки

<a href="https://patents.su/6-1783583-ustrojjstvo-dlya-obnaruzheniya-i-korrekcii-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и коррекции ошибок</a>

Предыдущий патент: Устройство для управления динамической памятью

Следующий патент: Способ определения температуры замедлителя нейтронов

Случайный патент: Дератель для граверного резца