Устройство для выполнения быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1520538

Авторы: Горинштейн, Евсеев, Назаренко, Сведлик

Текст

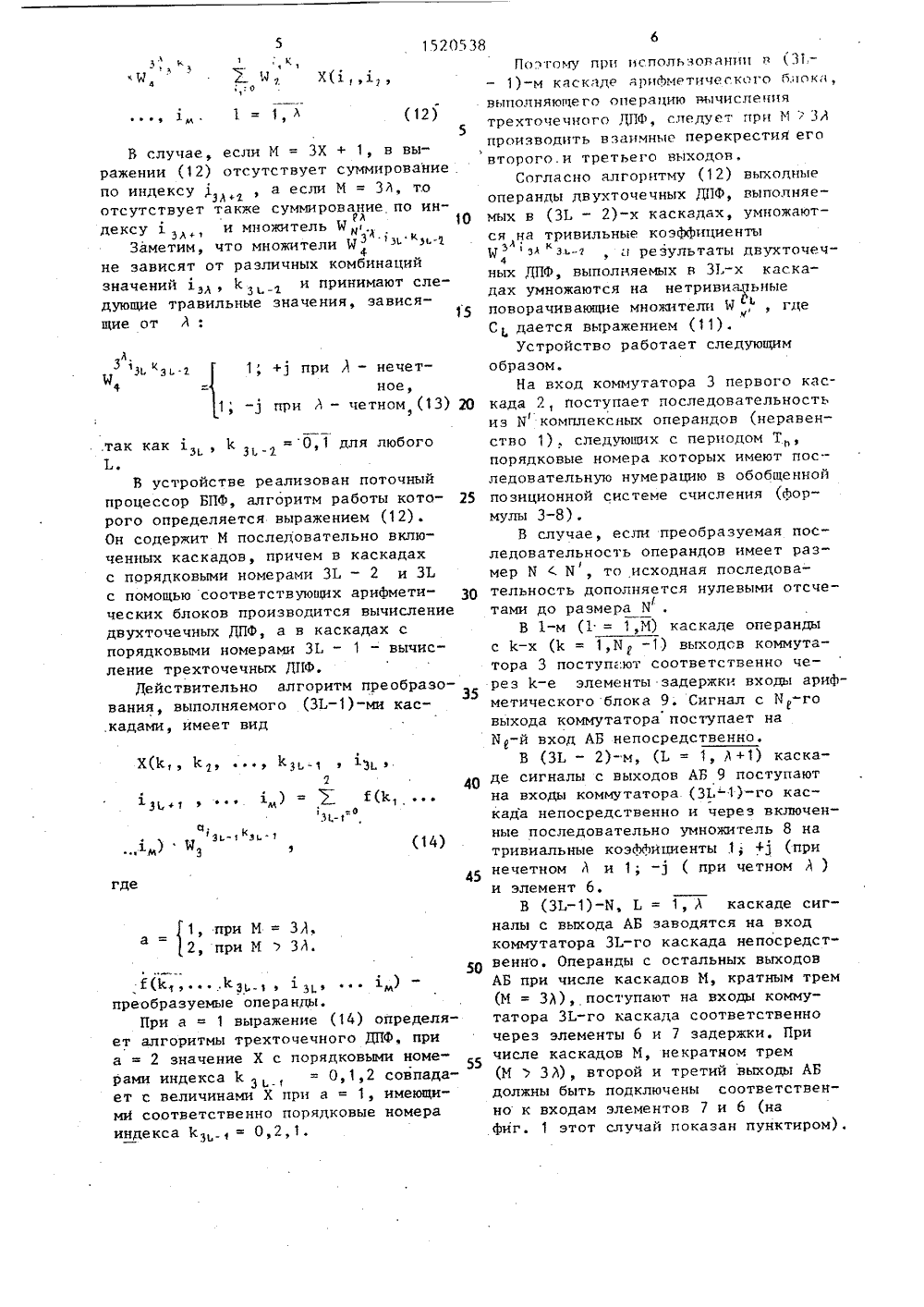

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСК РЕСПУБЛИ)4 С 332 ОП РЕТЕНИЯ 1еский и азаренктейн ьство СССР 5/332, 1984.)к. 198 12 управле бло янной телеикаск памяти (по- выходы ко 14, ( ия, блок 1 орачивающи циф быт ножиены орого о 1 Л)вычислени перандовУстроиство произБПФ массива комплек х еравенстм оп размеравом м.П Я сЯ Ф=1е МСЛ, 3 Пфпс 1ЗЛ+ Ь- 3 Таким образом ется на произв множителей и и полной тройкой число И радение полных адь роек дной "койодно жет быть еще(2,3) либо двН (И, то ис В случае, есл исло операндов ледует дополн ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидетел1107132, кл. С 06 Г 1Патент США3588460кл. С 06 Р 7/38, опубли Изобретение относится к области ровой обработки сигналов и может ь использовано в системах связи, гидролокации, радиолокации.Целью изобретения является упрощение устройства.На фиг. 1 представлена функциональ-, ная схема устройства, на Фиг.2 - схема устройства при М = 24; на фиг. 3 - алгоритм работы.Устройство содержит информационный вход 1, последовательно включенные каскады 2преобразований, 1 =1,М, содержащие коммутатор 3, элементы 4 - 7 задержки (в 22 д и 2 зл -м каскадах отсутствуют элементы 5 и 7, а в 2 л, -м каскаде элементы б и 7), умножитель 8 (на тривиальные коэФФициенты) (в 2 -х каскадах, Ь = 1,Э), арифметический блок (АБ)9, умножители 10 и 11 (на поворачивающие множители) .(в 2 з-х(54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ БЫС РОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ(57) Изобретение относится к облас цифровой обработки. сигналов и може быть использовано в системах связи гидролокации, радиолокации. Цель изобретения - упрощение устройства Цель достигается за счет того, что устройство содержит информационный вход, каскады преобразования, элем ты задержки, умножитель, арифметич кий блок, умножители, блок управле ния и блок постоянной памяти. 3 ил1520538 нулевыми отсчетрми до общего числа операндов И и производить вычисление/И -точечного ДПФ.Реализованный в устройстве алгоритм ГГ 1 Ф получе н на основе предс тав 5 пения естественного порядка следования обрабатываемых операндов х(1) в обобщенной позиционной системе счисления.Для эффективного вычисления ДПФ комплексной последовательности 1 х(з.);= Оф И, определяемого выражениемМ 1 15х (1 с) =( ) 14 (2)1=027 где 1 с = О,И - 1, Я,= ехР(-3(3) м1 с = К 1 И, 1 с (воаИ ), щ:1 где х 1 с, = О,И, (5) это индексы лексикографического представления переменных 1 и 1 с в обобщен ной позиционной системе счисления для данного разложения числа И на(а,в) - наибольший общий делительчисел а и в," Х(1 сЕ 2, ,1 с, ) м 14 -1 хЕ г,., ) 1:О Е 1 г 1 А 9 А П И З:1 а 1,-1 Л ЗЬ" ЗЬ г 3 1,2 1, П 11 31, З 1.-2 Л ;,х Л 4. йИз (10) путем соответствующей расстановки множителей 11 вдоль внутренних сумм получаем для МЗД + 2 (а2) алгоритм ВПФ, реализованный в предлагаемом устройстве (фиг, 1):(12)5 ф И В случае, если М = ЗХ + 1, в выражении (12) отсутствует суммирование . по индексу 1 , , а если М = ЗЛ, то отсутствует также суммирование по индексу ги множитель И.10Заметим что множителиз 1 з"1.-г4 не зависят от различных комбинаций значений 1 л, 1 з и принимают следующие травильные значения, зависящие от Л;15 Л,31, э.-г 3 1 К 1, + при Л - нечетное,1; -3 при Л - четном,(13) 203 Ь1 Э 1г(14) где 1 , приМ=ЗЛ.2, при М ) ЗЛ. 50ЕОс 11.1 ЗЬфЗЬфм) преобразуемые операнды.При а = 1 выражение (14) определяет алгоритмы трехточечного ДПФ, при а = 2 значение Х с порядковыми номе 55 рами индекса 1, = 0,1,2 совпадает с величинами Х при а = 1, имеющими соответственно порядковые номера индекса 1 с, , = 0,2,1,.так как 1 , 1 с=0,1 для любого Ь.В устройстве реализован поточный процессор БПФ, алгоритм работы кото рого определяется выражением (12). Он содержит М последовательно включенных каскадов, причем в каскадах с порядковыми номерами ЗЬ - 2 и ЗЬ с помощью соответствующих арифметических блоков производится вычисление двухточечных ДПФ, а в каскадах с порядковыми номерами ЗЬ - 1 - вычисление трехточечных ДПФ,Действительно алгоритм преобразования, выполняемого (ЗЬ)-ми кас,кадами, имеет вид Поэтому при использовании 11 (31, -1)-м каскаде арифметического блока,выполняющего операцию вычислениятрехточечного ДЛФ, следует при МЗЛпроизводить взаимные перекрестия еговторого.и третьего выходов,Согласно алгоритму (12) вьгходныеоперанды двухточечных ДПФ, выполняемых в (ЗЬ - 2)-х каскадах, умножают -ся на тривильные коэффициентыз"ку з з 1-1, я результаты двухточечных ДПФ, выполняемых в ЗЬ-х кас.кадах умножаются на нетривиальныеповорачивающие множители 1,", гдеС дается выражением (11).Устройство работает следующимобразом.На вход коммутатора 3 первого каскада 2, поступает последовательностьиз И комплексных операндов (неравенство 1). следующих с периодом Т,порядковые номера которых имеют последовательную нумерацию в обобщеннойпозиционной системе счисления (формулы 3-8).В случае, если преобразуемая последовательность операндов имеет размер М С М , то исходная последовательность дополняется нулевыми отсчетами до размера ИВ 1-м (1 = 1,М) каскаде операндыс 1 с - х (1 с = 1,М -1) выходов коммутатора 3 поступ".ют соответственно через К-е элементы задержки входы арифметического блока 9. Сигнал с И-говыхода коммутатора поступает наИ-й вход АБ непосредственно,В (ЗЬ - 2)-м, (Ь = 1, Л +1) каскаде сигналы с выходов АБ 9 поступаютна входы коммутатора (ЗЬ)-го каскада непосредственно и через включенные последовательно умножитель 8 натривиальные коэффипиенты 1; Ф (принечетном 1 и 1; -З ( при четном Л )и элемент 6.В (ЗЬ)-М, Ь = 1, Л каскаде сигналы с выхода АБ заводятся на входкоммутатора ЗЬ-го каскада непосредственно. Операнды с остальных выходовАБ при числе каскадов М, кратным трем(М = ЗЛ), поступают на входы коммутатора ЗЬ-го каскада соответственночерез элементы б и 7 задержки, Причисле каскадов М, некратном трем(М ) 3 Л), второй и третий выходы АБдолжны быть подключены соответственно к входам элементов 7 и 6 (нафиг. 1 этот случай показан пунктиром), В 31 м каскаде сигнялы с ньходов Л 1 Ч поступают на входы коммутатора (31,+1)-го каскада соответственно через умножители О и 11 на нетривиаль 5 ные поворачивающие множители И г",При М = ЗЛ + 2 В(3 Л + 1) каскаде отсутствует умножптель 8 на тривиальные коэффициенты. При этом сигнал с второго выхода ЛГ поступает непосредственно иа вход элемента 6. При М = ЗЛ, 3 Л + 1 или ЗД - 2 выходами устройства являются выходы, АБ соответствующих М-х каскадов.15Формула изобретения Устройство для выполнения быстрого преобразования Фурье, содержащее ММ- каскадов преобразования (где П. М ( 2 О,иИ 4 ПИ; М 613 ЗЛ+ 1; ЗЛ+ 2), 13.- зь 1 здзь- = И= 3" 1, = 1 , И - размер пре образования), блок управления и блок постоянной памяти, причем каскад пре, образования с номером 1 Е 131, - 2, 31., 3 Ь + 1) содержит арифметический блок, первый и второй элементы за- ЗО держки и коммутатор, при этом входы первого и второго операндов арифметического блока подключены соответственно к выходу первого элемента задержки и первому выходу коммутатора второй выход которого подключен к входу первого элемента задержки, выход первого операнда арифметического блока и выход второго элемента задержки подключень соответственно к первому и второму информационным входам коммутатора (1 + 1)-го каскада преобразования, а в 31,-м (1. =1,Л) каскаде преобразования выход второго операнда арифметического бло ка подключен к первому входу умножителя, выход которого подключен к входу второго элемента задержки, причем тактовые вьходы первой группы блока управления подключены к управляющим входам коммутаторов соответствующих каскадов преобразования, так-, товые выходы второй группы блока управления подключены к тактовым вхо 8 Ядям первого и второго элементов зя -держки соответствующих кяскядов преобразования, адресный выход блока управления подключен к адресному вхо - ду блока постоянной памяти, выходы первой группы которого подключены к вторым входам умножителей соответствующих каскадов преобразования, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства в (31,-2)-м каскаде преобразования, выход второго операнда арифметического блока подключен к первому входу умножтеля, выход которого подключен к входу второго элемента задержки, выход второго операнда арифметического блока (3 Л + 1)-го каскада преобразования подключен к входу второго элемента задержки, в 31,-м каскаде преобразования первый выход арифметического блока подключен к первому входу второго умножителя, выход которого подключен к первому информационному входу коммутатора (31,+1)-го каскада, при этом каскады преобразования с номерами (ЗЬ) (1. = 1, Л + 1) содержат арифметический блок, коммутатор и четыре элемента задержки, при этом первый, второй и третий выходы коммутатора подключены соответственно к входам первого и второго элементов задержки и входу третьего операнда арифметического блока, входы первого и второго операндов которого подключены к выходам соответственно первого и второго элементов задержки, выход первого операнда арифметического блока, выходы третьего и четвертого элементов задержки подключены соответственно к первому, второму и третьему информационным входам коммутатора ЗЬ-го (1. = 1,Л) каскада преобразования, входы третьего и четвертого элементов задержки подключены при М =. 33 соответственно к выходам второго и третьего операндов арифметического блока, а при И ) ЗЛ - соответственно к выходам третьего и второго операндов арифметического блока, при этом выходы второй группы блока постоянной памяти подключены к вторым входам вторых умножителей соответствующих каскадов преобразования.1520538 ч съ"з 1ь ,сь Составитель А.БарановРедактор В,Бугренкова Техред Л.Сердюкова Корректор Л.Патай Подписно ж 6 Производственно-издательский комбинат "Патент Гагарина, 10 од, у Заказ 6760/51 Т ВНИИПИ Государственного коми 113035, Мосета по изобретениям и открьгтиям при ГКНТ ССд, Ж, Раушская наб., д. 45

СмотретьЗаявка

4288252, 21.07.1987

ОДЕССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

СВЕДЛИК МЕШУЛИМ БЕНИЯМИНОВИЧ, НАЗАРЕНКО АНАТОЛИЙ АНАТОЛЬЕВИЧ, ЕВСЕЕВ ВАЛЕРИЙ ЛЕОНИДОВИЧ, ГОРИНШТЕЙН БОРИС ГИДАЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, выполнения, преобразования, фурье

Опубликовано: 07.11.1989

Код ссылки

<a href="https://patents.su/6-1520538-ustrojjstvo-dlya-vypolneniya-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выполнения быстрого преобразования фурье</a>

Предыдущий патент: Устройство для моделирования систем радиосвязи

Следующий патент: Устройство для преобразования в базисе кусочно-квадратичных функций уолша

Случайный патент: Устройство для отбражения информации