Приемник цифровых высокоскоростных фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

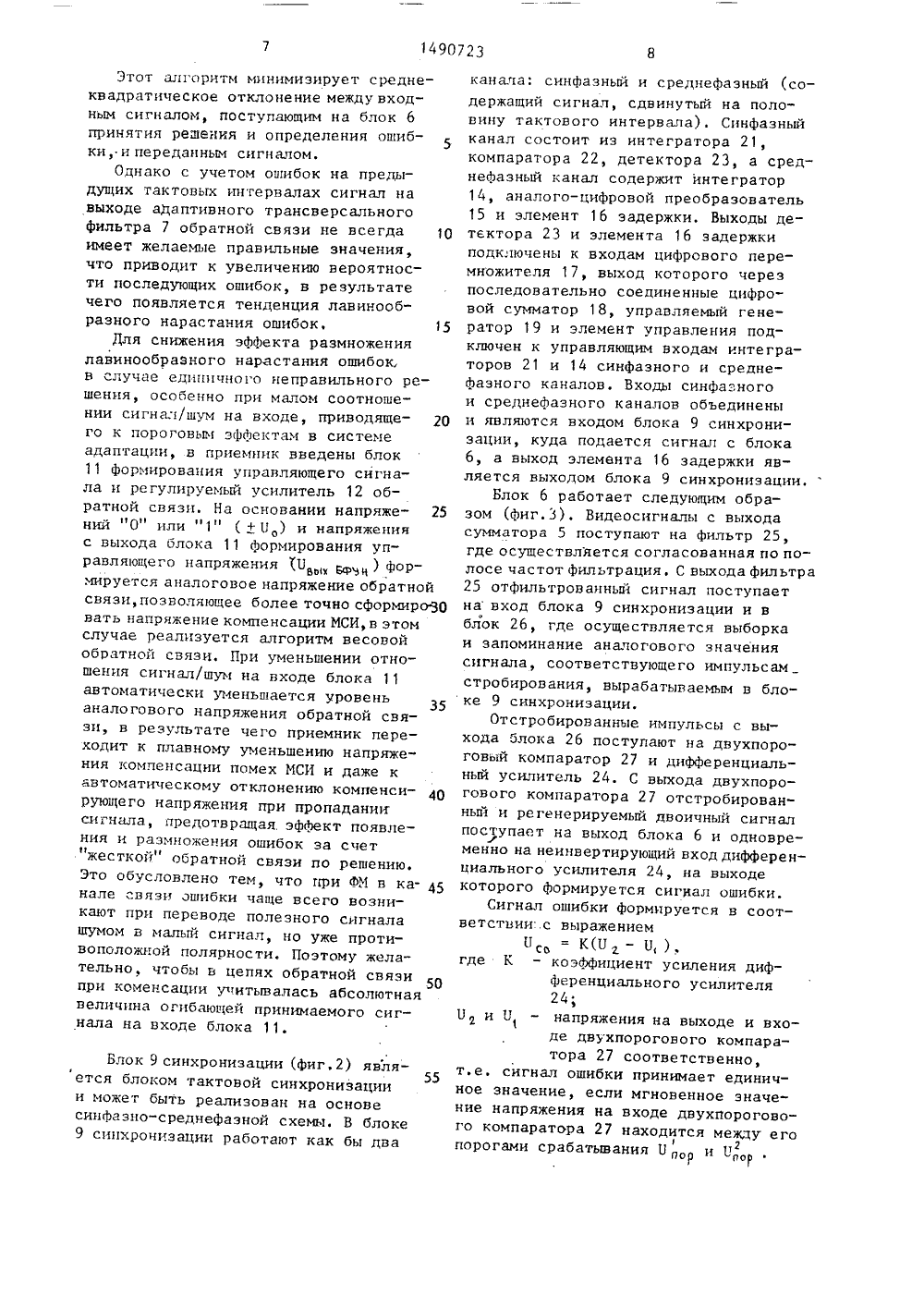

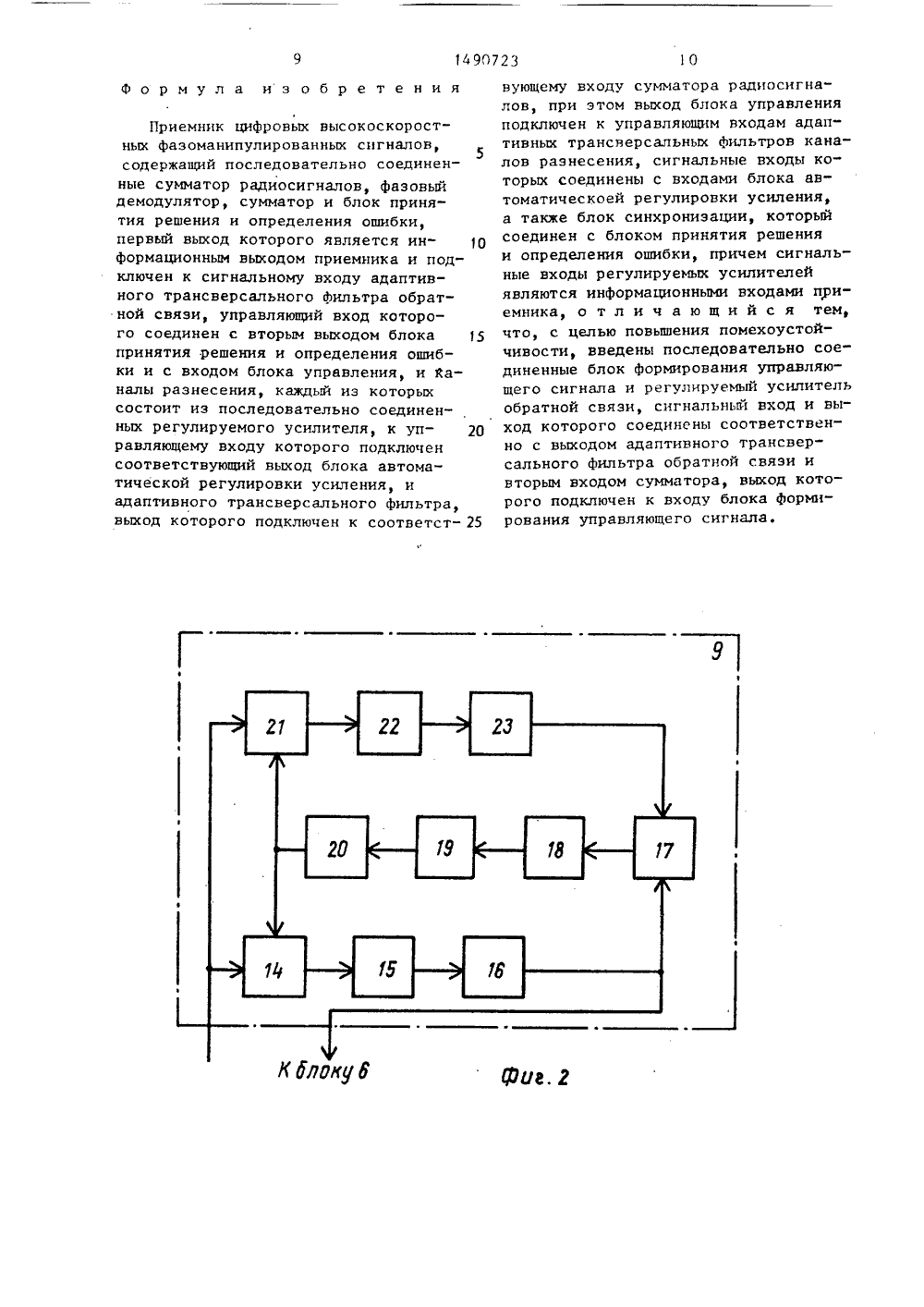

(П 14 Н 04 1. 27/ ПИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВУ АВТОРСК ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР(54) ПРИЕМНИК ЦИФРОВЫХ ВЫСОКОСКОРОСТНЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ(57) Изобретение относится к радиотехнике. Цель изобретения - повышениепомехоустойчивости. Приемник содержит каналы 1 разнесения, состоящиекаждый из адаптивного трансверсального фильтра 2 и регулируемого усилителя 3, Фазовый демодулятор 4, сумматор 5, блок 6 принятия решения и определения ошибки, адаптивный трансверсальный Фильтр 7 обратной связи,блок 8 управления, блок 9 синхронизации, блок 10 автоматической регулировки усиления, блок 11 Формирования управляющего сигнала, регулируемый усилитель 12 обратной связи и сумматор 13 радиосигналов. ВходныеФсигналы через канющ 1 поступают в сумматор 13, где линейно суммируются. Далее полученный сигнал подвергается фазовой демодуляции и поступает в сумматор 5, где обеспечивается компенсация помех межсимвольной интерФеренции. Блок 6 принятия решения и определения ошибки из полученного сигнала Формирует выходной информационный сигнал и сигнал ошибки. Цель достигается введением блока 11 формирования управляющего сигнала и усилителя 12, с помощью которых формируется компенсирующее напряжение помехи, определяемое соотношением сигнал/шум в канале. 3 ил.Изобрете ие относится к радиотехнике и может быть использовано в системах высокоскоростной передачи данных методами Фазовой манипуляции (щ).Цель изобретения - повышение помехоустойчивости.На Фиг.1 представлена структурная электрическая схема предлагаемого приемника; на фиг.2 - схема блока синхронизации; на Фиг.З - схема блока ггрпцятия решения и определения ошибки.Приемник цифровых высокоскоростных 15 Фазоманипулированцых сигналов содержит (фиг.1) каналы 1-1 разнесения, ка.кдый из которых состоит из адаптивного грацсверсального фильтра 2 и регулируемого усилителя 3, фазовый 20 демодулятор 4, сумматор 5, блок 6 принятия решения и определения ошибки, адаптивный трансверсальный фильтр 7 обратной связи, блок 8 управления, блок 9 синхронизации, блок 10 автома" 25 тической регулировки усиления, блок 11 формирования управляющего сигнала, регулцру:мый усилитель 12 обратной связи ц сумматор 13 радиосигналов.Блок 9 синхронизации включает 30 (Фиг.2) средцефазцый канал, состоящий из интегратора 14, аналого-цифрового преобразователя 15 и элемента 16 задержки, цифровой перемножитель 17, цифровой сумматор 18, управляемый 35 генератор 19, элемент 20 управления и синфазцый канал, состоящий из ин-. тегратора 21, компаратора 22 и детек тора 23.Блок 6 принятия решения и опреде пения ошибки образуют (фиг.З) дифференциальный усилитель 24, фильтр 25 шгжцих частот, блок 26 выборки и хранения и двухпороговый компаратор 27. 45Приемник работает следующим образом.В статическом состоянии приемник цифровых высокоскоростных ФМ сигналов имеет следующие связи между узлами и блоками. Входы и ветвей разнесения являются входами предлагаемого устройства, каждая ветвь разнесения содержит последовательно соединенные регулируемый усилитель и адаптивный трансверсальцый фильтр 2, выходы адаптивных трансверсальных Фильтров 2 соединены с п входами сумматора 13 радиосигналов, выход которого чероз последовательно соединенные фазовый демодулятор 4 и первый вход сумматора 5 подключен к блоку 6 принятия решения и определения ошибки, первый выход которого является выходом предлагаемого устройства и подключен к входу адаптивного трансверсального Фильтра 7 обратной связи. Второй выход блока 6 принятия решения и определения ошибки ппдключен одновременно к управляющему входу адаптивного трансверсального Фильтра 7 обратной связи и входу блока 8 управления адаптивными трансверсальными Фильтрами. Кроме того, блок 6 принятия решения и определения ошибки соединен с блоком 9 синхронизации, Выходы регулируемых усилителей 3 ветвей разнесения подключены к и входам блока 10 автоматической регулировки усилия, выход которого подключен одновременно к всем управляющим входам регулируемых усилителей 3 ветвей разнесения, Вход блока 11 формирования управляющего сигнала подклю .ен к выходу сумматора 5, выход этого блока соединен с управляющим входом регулируемого усилителя 12 обратной связи. Выход адаптивного трацсверсального Фильтра 7 обратной связи через регулируемый усилитель 12 обратной связи подключен к второму входу счматора 5.Гегулируемые усилители 3 каналов 1-1 д разнесения предназначены (Фиг.1) для согласования большого динамического диапазона входных сигналов с относительно небольшим динамическим диапазоном адаптивных трансверсальнь". Фильтров 2, которые обеспечивают управляемую Фильтрацию сигналов соответствующих каналов 1-11 разнесения. Сумматор 13 радиосигналов предназначен для линейного суммирования сигналов п каналов разнесения 1-1 л. Фазовый демодулятор 4 предназначен для Фазовой демодуляции суммарного сигнала. Сумматор 5 обеспечивает компенсацию помех межсимвольной интерференции (МСИ). Блок 6 принятия решения и определения ошибки является по существу решающим блоком, формирующим выходной информационный сигнал, и одновременно обеспечивает получение сигнала ошибки, Адаптивный трансверсальный Фильтр 7 обратной связи предназначен для формирбвация напряжения оценки помехи.1490723 канала: синфазный ц среднефазный (содержащий сигнал, сдвинутый на половину тактового интервала). Сцнфазный канал состоит из интегратора 21, компаратора 22, детектора 23, а среднефазный канал содержит интегратор 14, аналого-цифровой преобразователь 15 и элемент 16 задержки. Выходы детектора 23 и элемента 16 задержки подключены к входам цифрового пере- множителя 17, выход которого через последовательно соединенные цифровой сумматор 18, управляемый генератор 19 и элемент управления подключен к управляющим входам интеграторов 21 и 14 синфазного и среднефаэного каналов. Входы синфазного и среднефазного каналов объединены и являются входом блока 9 синхронизации, куда подается сигнал с блока 6, а выход элемента 16 задержки является выходом блока 9 синхронизации.Блок 6 работает следующим образом (фиг.3), Видеосигналы с выхода сумматора 5 поступают на фильтр 25, где осуществляется согласованная по полосе частот фильтрация. С выхода фильтра 25 отфильтрованный сигнал поступает на вход блока 9 синхронизации и в блок 26, где осуществляется выборка и запоминание аналогового значения сигнала, соответствующего импульсам стробирования, вырабатываемым в блоке 9 синхронизации.Отстробированные импульсы с выхода блока 26 поступают на двухпороговый компаратор 27 и дифференциальный усилитель 24. С выхода двухпорогового компаратора 27 отстробированный и регенерируемый двоичный сигнал поступает на выход блока 6 и одновременно на неинвертирующий вход дифференциального усилителя 24, на выходе которого формируется сигнал ошибки.Сигнал ошибки формируется в соответствии .с выражениемсо 1 ф П )где Е - коэффициент усиления дифференциального усилителя24;У и У - напряжения на выходе и вхо 1де двухпорогового компаратора 27 соответственно, т.е. сигнал ошибки принимает единичное значение, если мгновенное значение напряжения на входе двухпорогового компаратора 27 находится между егопорогами срабатывания Ни Ппор Блок 9 синхронизации (фиг,2) является блоком тактовой синхронизации55 и может быть реализован на основе синфазно-среднефазной схемы. В блоке 9 синхронизации работают как бы два Этот алгоритм минимизирует средне- квадратическое отклонение между входным сигналом, поступающим на блок 6 принятия решения и определения ошибки, и переданным сигналом.Однако с учетом ошибок на преды - дущих тактовых интервалах сигнал на выходе адаптивного трансверсального фильтра 7 обратной связи не всегда 10 имеет желаемые правильные значения, что приводит к увеличению вероятности последующих ошибок, в результате чего появляется тенденция лавинообразного нарастания ошибок, 15Для снижения эффекта размножения лавинообразного нарастания ошибок, в случае единичного неправильного решения, особенно прц малом соотношении сигнал/шум на входе, приводящего к пороговым эффектам в системе адаптации, в приемник введены блок 11 формирования управляющего сигнала и регулируемый усилитель 12 обратной связи, На основании напряже ний "О" цли " 1" ( + Н ) и напряжения с выхода блока 11 формирования управляющего напряжения Ур, ) формируется аналоговое напряжение обратной связи, позволяющее более точно сформиро.30 вать напряжение компенсации МСИ,в этом случае реализуется алгоритм весовой обратной связи. При уменьшении отношения сигнал/шум на входе блока 11автоматически уменьшается уровень35аналогового напряжения обратной связи, в результате чего приемник переходит к плавному уменьшению напряже"ния компенсации помех МСИ и даже кавтоматическому отклонению компенсирующего напряжения при пропаданиисигнала, предотвращая, эффект появления и размножения ошибок за счети 11жесткои обратной связи по решению.Это обусловлено тем, что при ФМ в канале -"вязи ошибки чаще всего возникают прц переводе полезного сигналашумом в малый сигнал, но уже противоположной полярности. Поэтому желательно, чтобы в цепях обратной связи50при коменсации учитывалась абсолютнаявеличина огибающей принимаемого сигнала на входе блока 11.формула изобретения Приемник цифровых высокоскоростных фазоманипулированных сигналов, содержащий последовательно соединенные сумматор радиосигналов, фазовый демодулятор, сумматор и блок принятия решения и определения ошибки, первый выход которого является ин формационным выходом приемника и подключен к сигнальному входу адаптивного трансверсального фильтра обратной связи, управляющий вход которого соединен с вторым выходом блока 15 принятия решения и определения ошибки и с входом блока управления, и каналы разнесения, каждый иэ которых состоит из последовательно соединенных регулируемого усилителя, к уп равляющему входу которого подключен соответствующий выход блока автоматической регулировки усиления, и адаптивного трансверсального фильтра, выход которого подключен к соответст вующему входу сумматора радиосигналов, при этом выход блока управленияподключен к управляющим входам адаптивных трансверсальных фильтров каналов разнесения, сигнальные входы которых соединены с входами блока автоматическоей регулировки усиления,а также блок синхронизации, которыйсоединен с блоком принятия решенияи определения ошибки, причем сигнальные входы регулируемых усилителейявляются информационными входами пуиемника, о т л и ч а ю щ и й с я тем,что, с целью повышения помехоустойчивости, введены последовательно соединенные блок формирования управляющего сигнала и регулируемый усилительобратной связи, сигнальный вход и выход которого соединены соответственно с выходом адаптивного трансверсального фильтра обратной связи ивторым входом сумматора, выход которого подключен к входу блока формирования управляющего сигнала.1490723 Ю благу У И она Ы 7 Ю сига сшц 6Ф Юл,Составитель А.Москевичедактор А.Огар Техред М.Дидык Корректор С.Черни Заказ 3761/57 Тирак 626 Подписное НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб., д. 4/5оизводственно-издательский комбинат "Патент", г. Укгород, ул. Гагарин

СмотретьЗаявка

4222014, 06.04.1987

ВОЙСКОВАЯ ЧАСТЬ 25871

БУРАЧЕНКО ДМИТРИЙ ЛЕОНИДОВИЧ, БОГАТЫРЕВ ВЛАДИМИР НИКОЛАЕВИЧ, ВОЗНЮК МИХАИЛ АЛЕКСЕЕВИЧ, ТКАЧЕНКО ОЛЕГ СТЕПАНОВИЧ, ШЕПЕЛЕВ ВЛАДИСЛАВ ГЕРМАНОВИЧ, ШИНКАРЕНКО ДМИТРИЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: высокоскоростных, приемник, сигналов, фазоманипулированных, цифровых

Опубликовано: 30.06.1989

Код ссылки

<a href="https://patents.su/6-1490723-priemnik-cifrovykh-vysokoskorostnykh-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Приемник цифровых высокоскоростных фазоманипулированных сигналов</a>

Предыдущий патент: Устройство для передачи информации

Следующий патент: Приемник дискретной информации

Случайный патент: Устройство для управления намоткой нити