Дельта-модулятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

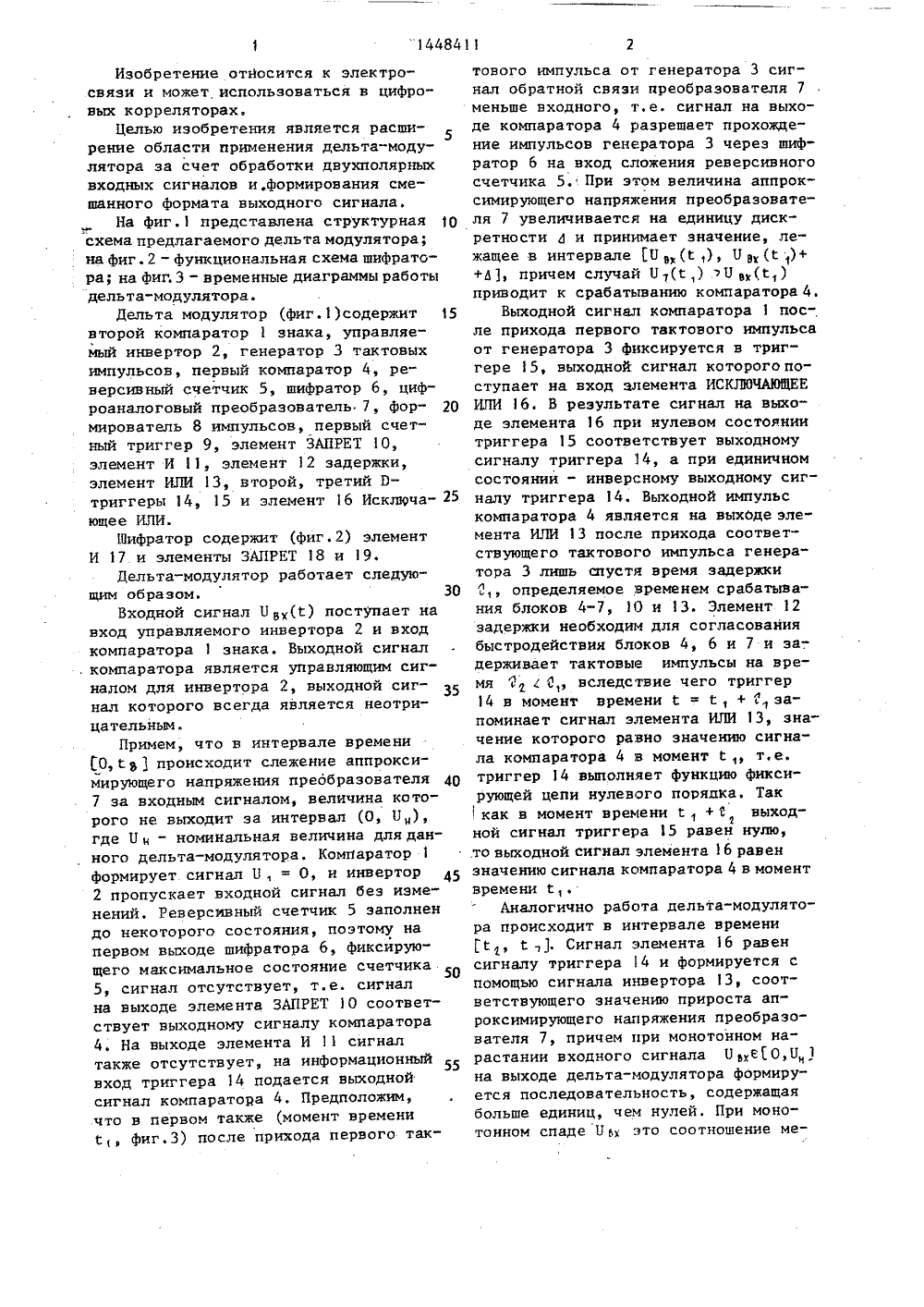

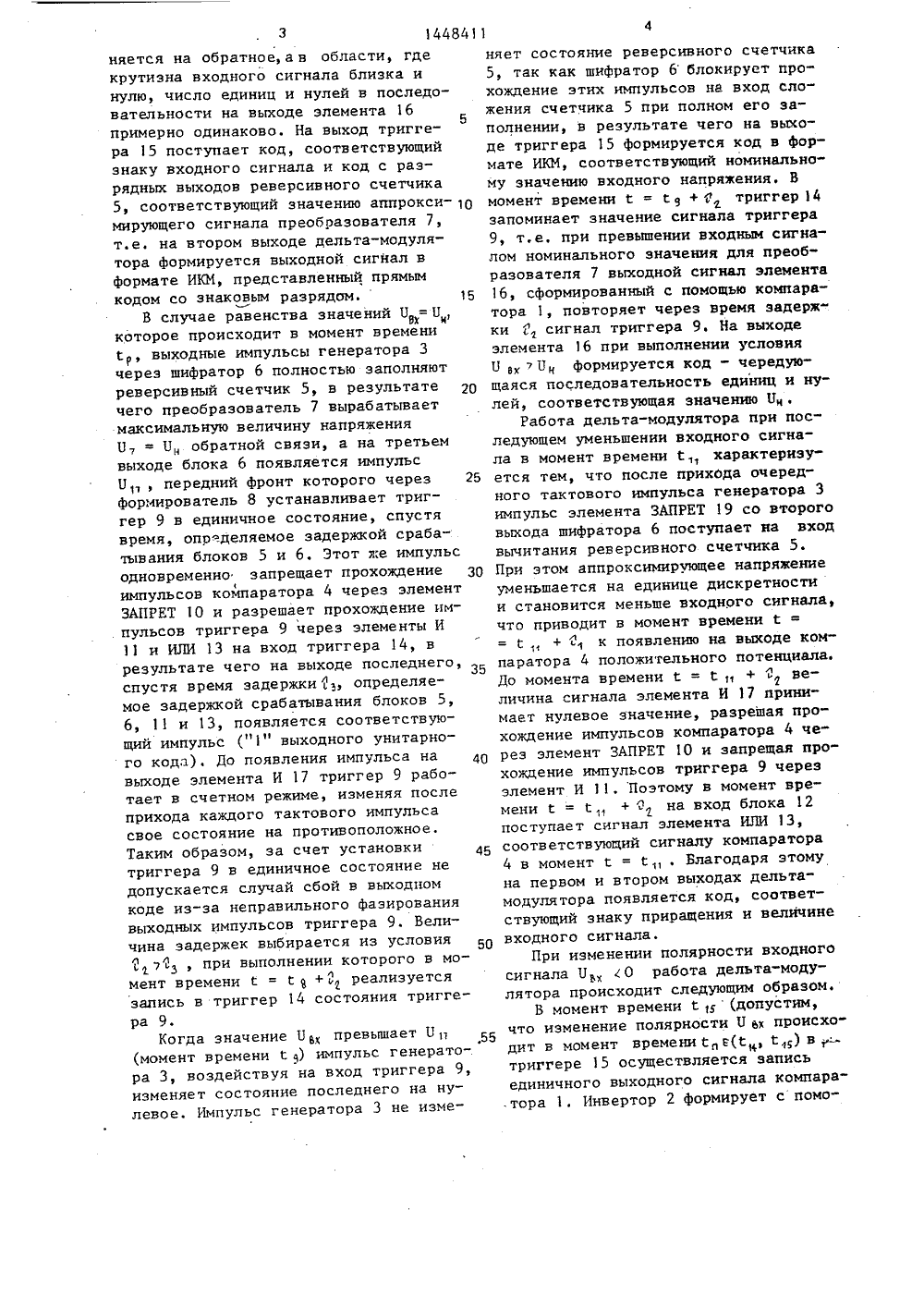

союз советскихсоцидлистических УБЛИК 3 М 3 0 ИСАНИЕ ИЗОБРЕТЕН ЕТЕПЬСТВ.Пристайко621,378(088Погрибной Вяция в сист Линейная дельах обработки сидовой модуляцие84, к, с.56-5тельство СССР3 М 3/02, 1985. а модул лов с - Рад импульсно-к иотехника, 1 АвторскоУ 1257849,в ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЬПИЯПРИ ГКНТ СССР 4238148/24-2404.05.8730.12,88. Бюл. У 48А.В.Тимченко, В.А.Погрибной(57) Изобретение относится к электросвязи и может использоваться в цифровых корреляторах. Изобретение позволяет расширить область применениядельта-модулятора эа.счет обработкидвухполярных входных сигналов и формирования смешанного формата выходного сигнала. Дельта-модулятор содержиткомпараторы 1 и 4, управляемый инвертор 2, генератор 3 тактовых импуль- .сов, реверсивный счетчик 5, шифраторб, цифроаналоговь;й преобразователь 7,формирователь 8 импульсов, триггеры 9,14 и 15, элемент ЗАПРЕТ О, элемент И 11,элемент 12 задержки элемент ИЛИ 13 иэлемент ИСКЛ 10 ЧАЮЩЕЕ ИЛИ 16. 3 ил.Изобретение относится к электросвязи и может использоваться в цифровых корреляторах.Целью изобретения является расши 5рение области применения дельта-модулятора за счет обработки двухполярныхвходных сигналов и,формирования смешанного формата выходного сигнала.На Фиг. представлена структурная 10схема предлагаемого дельта модулятора;на Фиг. 2 - функциональная схема шифратора; на фиг. 3 - временные диаграммы работыдельта-модулятора.Дельта модулятор (Фиг.1)содержит 15второй компаратор 1 знака, управляемый инвертар 2, генератор 3 тактовыхимпульсов, первый компаратор 4, реверсивный счетчик 5, шифратор 6, цифроаналоговый преобразователь 7, формирователь 8 импульсов, первый счетный триггер 9, элемент ЗАПРЕТ 10,элемент И 11, элемент 12 задержки,элемент ИЛИ 13, второй, третий 0 триггеры 14, 15 и элемент 16 Исключающее ИЛИ.Шифратор содержит (фиг.2) элементИ 17 и элементы ЗАПРЕТ 18 и 19,Дельта-модулятор работает следующим образом. 30Входной сигнал Б ц поступает навход управляемого инвертора 2 и входкомпаратора 1 знака. Выходной сигнал.компаратора является управляющим сигналом для инвертора 2, выходной сигнал которого всегда является неотрицательным.Примем, что в интервале времени0, Эпроисходит слежение аппроксимирующего напряжения преобразователя 407 за входным сигналом, величина которого не выходит за интервал (О, Б),где Бн - номинальная величина для данного дельта-модулятора. Компаратор 1формирует сигнал Б= О, и инвертор 452 пропускает входной сигнал беэ изменений, Реверсивный счетчик 5 заполнендо некоторого состояния, поэтому напервом выходе шифратора 6, фиксирующего максимальное состояние счетчика5, сигнал отсутствует, т.е. сигнална выходе элемента ЗАПРЕТ О соответствует выходному сигналу компаратора4, На выходе элемента И 1 сигналтакже отсутствует, на информационныйвход триггера 14 подается выходнойсигнал компаратора 4, Предположим,что в первом также (момент времениС фиг.3) после прихода первого тактового импульса от генератора 3 сигнал обратной связи преобразователя 7 меньше входного, т,е. сигнал на выходе компаратора 4 разрешает прохождение импульсов генератора 3 через шифратор 6 на вход сложения реверсивного счетчика 5. При этом величина аппроксимирующего напряжения преобразователя 7 увеличивается на единицу дискретности д и принимает значение, лежащее в интервале ГП е( д П вх( 1)+ +Ь, причем случай П(,) П в приводит к срабатыванию компаратора 4.Выходной сигнал компаратора 1 после прихода первого тактового импульса от генератора 3 Фиксируется в триггере 15, выходной сигнал которогопоступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16. В результате сигнал иа выходе элемента 16 при нулевом состоянии триггера 15 соответствует выходному сигналу триггера 14, а при единичном состоянии - инверсному выходному сигналу триггера 14, Выходной импульс комнаратора 4 является на выходе элемента ИЛИ 13 после прихода соответствующего тактового импульса генератора 3 лишь спустя время задержкиопределяемое временем срабатывания блоков 4-7, 10 и 13. Элемент 12 задержки необходим для согласования быстродействия блоков 4, 6 и 7 и задерживает тактовые импульсы на время 7,вследствие чего триггер 14 в момент времени 1й, +запоминает сигнал элемента ИЛИ 13, значение которого равно значению сигнала компаратора 4 в моментт,е. триггер 14 выполняет функцию фиксирующей цепи нулевого порядка. Таккак в момент времени+ 2, выходной сигнал триггера 15 равен нулю, .то выходной сигнал элемента 16 равен значению сигнала компаратора 4 в момент времени С.Аналогично работа дельта-модулятора происходит в интервале времениСигнал элемента 16 равен сигналу триггера 14 и формируется с помощью сигнала инвертора 13, соответствующего значению прироста апроксимирующего напряжения преобразователя 7, причем при монотонном нарастании входного сигнала 0 60,0 1 на выходе дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей. При монотонном спаде Бэто соотношение ме з 144841 няется на обратное, а в области, где крутизна входного сигнала близка и нулю, число единиц и нулей в последовательности на выходе элемента 165 примерно одинаково. На выход триггера 15 поступает код, соответствующий знаку входного сигнала и код с разрядных выходов реверсивного счетчика 5, соответствующий значению аппрокси О мирующего сигнала преобразователя 7, т.е. на втором выходе дельта-модулятора формируется выходной сигнал в формате ИКИ, представленный прямым кодом со знаковым разрядом. 15В случае равенства значений П =П, которое происходит в момент времени С, выходные импульсы генератора 3 через шифратор 6 полностью заполняют реверсивный счетчик 5, в результате чего преобразователь 7 вырабатывает максимальную величину напряжения 11 = 11, обратной связи, а на третьем выходе блока 6 появляется импульс У 1 передний фронт которого через 25 формирователь 8 устанавливает триггер 9 в единичное состояние, спустя время, опр .деляемое задержкой срабатывания блоков 5 и 6. Этот же импульс одновременно запрещает прохождение ЗО импульсов компаратора 4 через элемент ЗАПРЕТ 10 и разрешает прохождение импульсов триггера 9 через элементы И 11 и ИЛИ 13 на вход триггера 14, в результате чего на выходе последнего 35 спустя время задержки , определяемое задержкой срабатывания блоков 5, 6, 11 и 13, появляется соответствующий импульс ("1" выходного унитарного кодл). До появления импульса на 40 выходе элемента И 17 триггер 9 работает в счетном режиме, изменяя после прихода каждого тактового импульса свое состояние на противоположное.Таким образом, за счет установки45 триггера 9 в единичное состояние не допускается случай сбой в выходном коде из-за неправильного фаэирования выходных импульсов триггера 9. Величина задержек выбирается из условияпри выполнении которого в момент времени с = с+ 3 реализуется зались в триггер 14 состояния триггера 9.Когда значение Пьпревышает Уп (момент времени С ) импульс генератора 3, воздействуя на вход триггера 9, изменяет состояние последнего на нулевое. Импульс генератора 3 не изменяет состояние реверсивного счетчика 5, так как шифратор 6 блокирует прохождение этих импульсов на вход сло" жения счетчика 5 при полном его заполнении, в результате чего на выходе триггера 15 формируется код в формате ИКМ, соответствующий номинально" му значению входного напряжения, В момент времени с = с з + У триггер 14а запоминает значение сигнала триггера 9, т,е, при превышении входным сигналом номинального значения для преобразователя 7 выходной сигнал элемента16, сформированный с помощью компаратора 1, повторяет через время задержки 8 сигнал триггера 9. На выходе элемента 16 при выполнении условия ППц формируется код - чередующаяся последовательность единиц и нулей, соответствующая значению У.Работа дельта-модулятора при последующем уменьшении входного сигнала в момент времени Схарактеризуется тем, что после прихода очередного тактового импульса генератора 3 импульс элемента ЗАПРЕТ 19 со второго выхода шифратора 6 поступает на вход вычитания реверсивного счетчика 5. При этом аппроксимирующее напряжение уменьшается на единице дискретности и становится меньше входного сигнала, что приводит в момент времени С = - +к появлению на выходе компаратора 4 положительного потенциала. До момента времени=+3 величина сигнала элемента И 17 прини" мает нулевое значение, разрешая прохождение импульсов компаратора 4 через элемент ЗАПРЕТ 10 и запрещая прохождение импульсов триггера 9 через элемент И 11. Поэтому в момент времени= с +на вход блока 122поступает сигнал элемента ИЛИ 13, соответствующий сигналу компаратора 4 в момент с = , . Благодаря этому на первом и втором выходах дельта" модулятора появляется код, соответствующий знаку приращения и величине входного сигнала.При изменении полярности входного сигнала У( 0 работа дельта-моду" лятора происходит следующим образом.В момент времени ,(допустим, что изменение полярности 11 ь происхо"дит в момент времение(, ) в; триггере 15 осуществляется запись единичного выходного сигнала компара.тора 1. Инвертор 2 формирует с помо 1448411щью управляющего сигнала компаратора 1 выходной сигнал 11 .в -01 . Аппроксимирующий сигнал преобразователя 7 в последующие моменты времениосуществляет слежение за сигналом11 р как описано, причем на выходетриггера 14 при монотонном нарастании сигнала 101 еО, И 1 формируется последовательность, содержащая 10больше единиц чем нулей, при монотонном спаде это соотношение меняетсяна обратное, а в области, где 1.У УДформируется последовательность из чередующихся единиц и нулей. На первом 15выходе дельта-модулятора при помощиэлемента 16 по единичному сигналутриггера 15 соотношение нулеи и единиц в указанных последовательностяхизменяется на обратное, т.е. при монотонном возрастании Пвх 1 Я 8 ( О),что соответствует монотонному спадуП , на первом выходе дельта-модулятора формируется последовательность,содержащая больше нулей, чем единиц. 25Аналогично, при монотонном спаде101(У(0), что соответствует монотонному нарастанию Б, на первомвыходе дельта-модулятора формируетсяпоследовательность, содержащая больше 30единиц, чем нулей, а при П ь-Уна выходе дельта-модулятора, как и впредыдущем случае, формируется чередующаяся последовательность нулей иединиц. Выходной сигнал дельта-модулятора на его втором выходе соответствует значению аппроксимирующего напряжения преобразователя 7, т.е, сточностью до дискрета д соответствуетвеличине Бьх, знак которого записан 40в триггере 15. Таким образом, на первом выходе устойчиво работающего дельта-модулятора формируется одноразрядная дель та-последовательность, соответствующая входному сигналу в диапазоне Пе Пн П н 1 а на втором выходе формируется сигнал, соответствующий модулю и знаку аппроксимирующего сиг- б 0 нала дельта-модулятора в указанном диапазоне. При выходе входного сигнала за указанный диапазон на первом выходе дельта-модулятора формируется чередующаяся последовательность нулей 55 и единиц, соответствующая ограничению Б= Ун, а на втором выходе - сигнал в формате ИЮ, равным приведенному ограничению. Работа шифратора 6 приведена на фиг,2.Таким образом, предлагаемый дельта-модулятор в промежутки времениблокирует выход компаратора 4 и одновременно формирует чередующуюся из нулей и единиц импульсную последовательность, что соответствует ограничению входного сигнала Уц на уровне Бн, т.е. на выходные сигналы дельта-модулятора вне зоны ограничения всегда соответствуот входному сигналу независимо от того, сколько раз и на какую длительность Б,1 -ЦнПн 3формула изобретенияДельта-модулятор, содержащий генератор тактовых импульсов, выход которого соединен непосредственно с первым входом шифратора, тактовым входом первого триггера и через элемент задержки с тактовым входом второго триггера, первый компаратор, выход кото" рого соединен с прямым входом элемента ЗАПРЕТ и вторым входом шифратора, первый и второй выходы которого соединены соответственно с одноименными входами реверсивного счетчика, выходы которого соединены с соответствующими третьими входами шифратора и входами цифро-аналогового преобразователя, выход которого соединен с первым входом первого компаратора, третий выход шифратора соединен через формирователь импульсов с установочным входом первого триггера, выход которого соединен с первым входом элемента И, выход которого и выход элемента ЗАПРЕТ соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с информационным входом второго триггера, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения дельта-модулятора за счет обработки двухполярных входных сигналов и формирования смешанного формата выходного сигнала, в него введены второй компаратор, управляемый инвертор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и третий триггер, информационный вход управляемого инвертора объединен с входом второго компаратора и является входом дельта-модулятора, выход второго компаратора соединен с информационным входом третьего триггера и7 ,14 управляющим входом управляемого ин" вертора, выход которого соединен с вторым входом первого компаратора, инверсный вход элемента ЗАПРЕТ объе. динен с вторым входом элемента И и подключен к третьему выходу шифратора, выход второго триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первым 4841выходом дельта"модулятора, тактовый вход третьего триггера подключен к выходу генератора тактовых импульсов, выход третьего триггера соединен с, вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является вторым выходом дельта- модулятора, выходы реверсивного счетчика являются третьими выходами дель" 10 та-модулятора..Парфеио водственно-яолиграфическое предприятие г. Ужгород, ул, Проектная,ЗаказНИИПИ Ю 56 Тираж 9 осударственного комите113 О 35, Москва 9 Подписноеа по изобретениям и открытиям при ГКНТ С Б, Раушская наб., д. 4/5

СмотретьЗаявка

4238148, 04.05.1987

ПРЕДПРИЯТИЕ ПЯ В-8751, ФИЗИКО-МЕХАНИЧЕСКИЙ ИНСТИТУТ ИМ. Г. В. КАРПЕНКО

ТИМЧЕНКО АЛЕКСАНДР ВЛАДИМИРОВИЧ, ПОГРИБНОЙ ВЛАДИМИР АЛЕКСАНДРОВИЧ, ПРИСТАЙКО ОЛЕГ РОМАНОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-модулятор

Опубликовано: 30.12.1988

Код ссылки

<a href="https://patents.su/6-1448411-delta-modulyator.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-модулятор</a>

Предыдущий патент: Цифровой синтезатор частот

Следующий патент: Преобразователь двоичного кода в двоично-десятичный

Случайный патент: Способ консервации целлюлозосодержащего материала