Процессор для преобразования цифровых сигналов по хааро подобным базисам

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1418745

Автор: Исмагилов

Текст

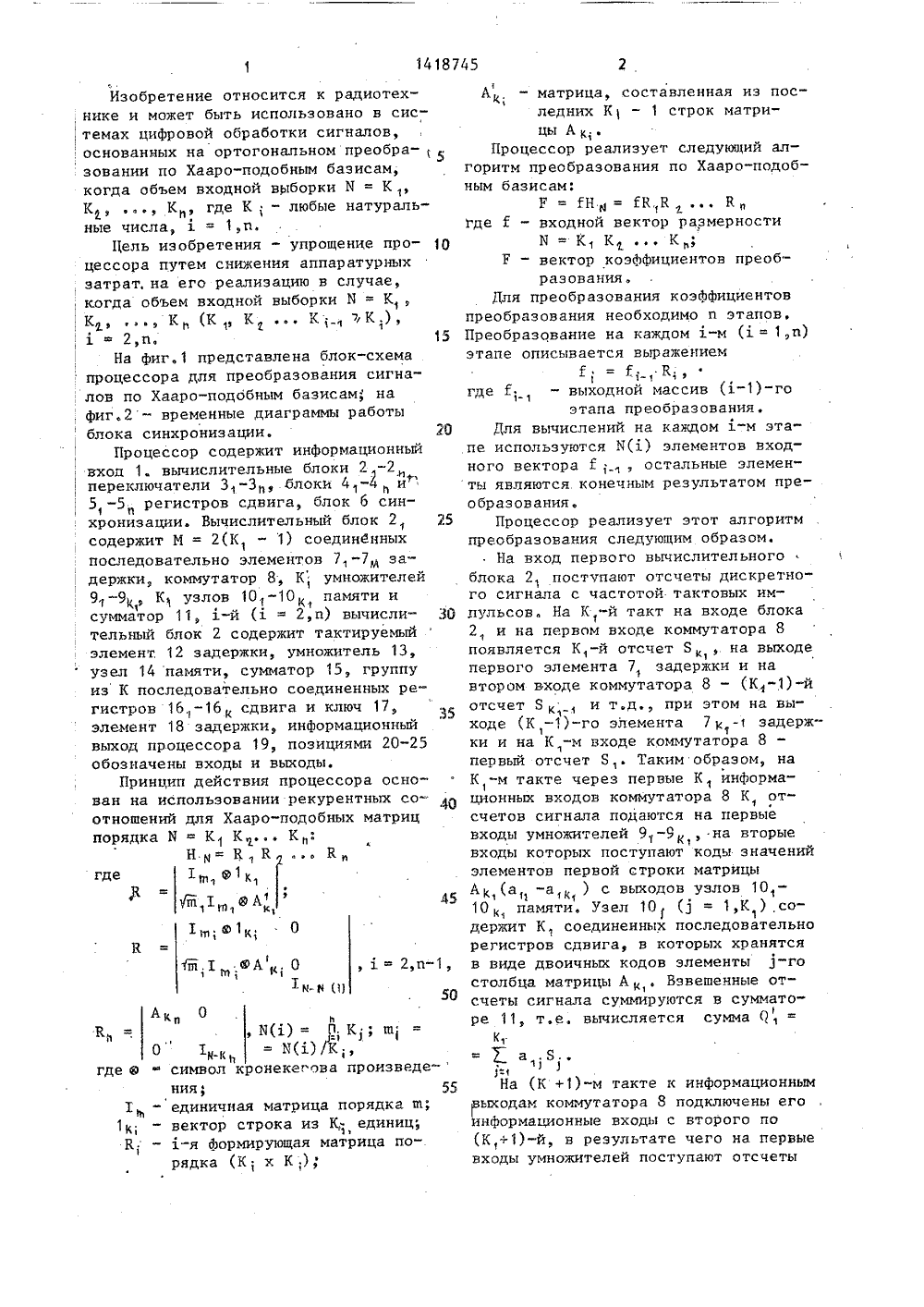

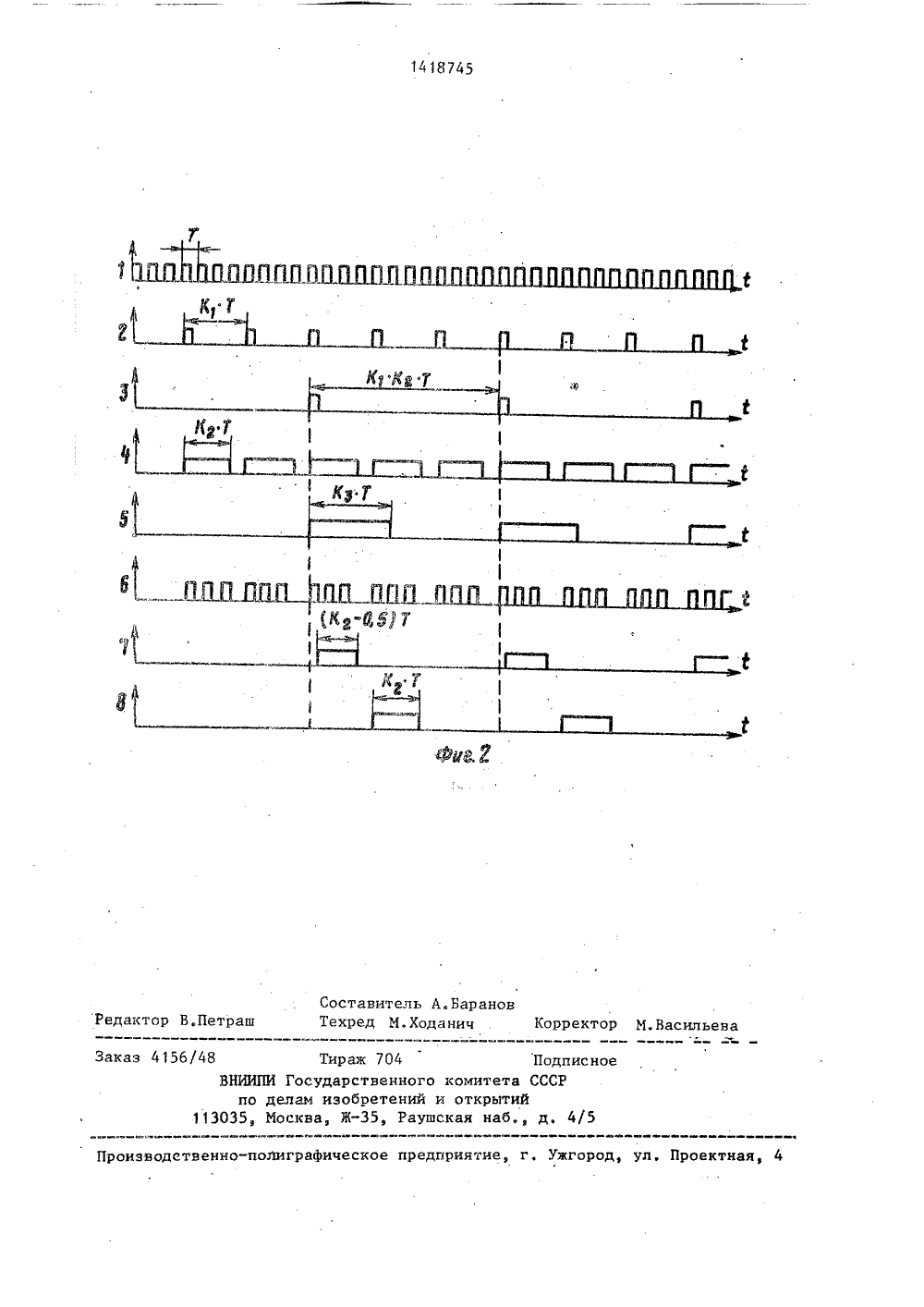

СОЮЗ СОВЕТСКИХСОЦИАЛ ИСТИЧЕСНИРЕСПУБЛИК 801418 4 С 06 Г 15/3 САНИЕ ИЗОБРЕТЕНИ ЕЛЬСТВУ ВТОРСКОМУ Узенажит15,Проки ован гнаГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Рабинер Л Гоулд Б, Теорияприменение цифровой обработки сиглов.- М.: Мир, 1978.Авторское свидетельство СССРВ 168966, кл. С 06 Р 15/332, 198,(54) ПРОЦЕССОР ДЛЯ ПРЕОБРАЗОВАНИЯЦИФРОВЫХ СИГНАЛОВ ПО ХААРО-ПОДОБН(57) Изобретение относится к радиэлектронике и может быть использов системах цифровой обработки си лов, основанных на ортогональном преобразовании по Хааро-подобным базисам, когда объем входной выборки И = К,КК, где К; - натуральные числа. Цель изобретения - упрощение устройства. Процессор содержит информационный вход 1, вычислительные. бло" ки 2-2, переключатель 3-3, блоки регистров сдвига 4 -4, 5,-5 ,блок синхронизации 6. Вычислительный блок 2, содержит элементы задержки 7, -, коммутатор 8, К умножителей 9,-9, К узлов памяти 10,-10 к, и сумматор 11, 1-й ( = 2,п) вычислительный блок 2 содержит элемент задержки 12, умноель 13, узел памяти 14, сумматор Ярегистры сдвига 16-16 к и ключ.1цессор также имеет элемент задерж 18 и информационный выход 19.2 илГИзобретение относится к радиотехнике и может быть использовано в сис; темах цифровой обработки сигналов, , основанных на ортогональном преобра-5 зовании по Хааро-подобным базисам, когда объем входной выборки М = КК. , К где К; - любые натуральные числа,= 1,п.Цель изобретения - упрощение процессора путем снижения аппаратурных затрат, на его реализацию в случае, когда объем входной выборки И = К, , Кйф " К (ККгщ 2,п. 15На Фиг,1 представлена блок-схема процессора для преобразования сигна" , лов по Хааро-подобным базисам," на Фиг,2 - временные диаграммы работы блока синхронизации. 2 ОПроцессор содержит информационный вход 1. вычислительные блоки 2 -2 переключатели 3-3 , блоки 4-1й" 5, -5 регистров сдвига, блок 6 синхронизации. Вычислительный блок 2 25содержит М = 2(К - 1) соединенных1последовательно элементов 7 -7 задержки, коммутатор 8, К, умножителей 9 -9, К узлов 10 впамяти и1сумматор 11, х-й (2,п) вычислительный блок 2 содержит тактируемыйэлемент. 12 задержки, умножитель 13, узел 14 памяти, сумматор 15, группу из К последовательно соециненных регистров 16-16сдвига и ключ 17,элемент 18 задержки, информационныйвыход процессора 19, позициями 20-25обозначены входы и выходы.Принцип действия процессора основан на использовании рекурентных соотношений для Хааро-подобных матриц порядка И = К 1 КК.Н= ННВи 1,1 ш 1 ю фА 1 щв 1 к, 0" символ кронекегова произведе-ния; 55 единичная матрица порядка ш; вектор строка из К;, единиц; х-я формирующая матрица порядка (К; х К) ф А, - матрица, составленная из пос 1ледних К 1 - 1 строк матрицы А,.Процессор реализует следующий алгоритм преобразования по Хааро-подобным базисам:где Е - входной вектор размерностиИ = К К,Р - вектор коэффициентов преобразования.Для преобразования коэффициентовпреобразования необходимо и этапов,Преобразование на каждом -м ( = 1,п)этапе описывается выражениемГ; = Г;, К;,где Г;, - выходнои массив (1.-1)-гоэтапа преобразования,Для вычислений на каждом д-м этапе используются И(х) элементов входного вектора Е; , остальные элементы являются конечным результатом преобразования,Процессор реализует этот алгоритмпреобразования следующим образом.На вход первого вычислительногоблока 2 поступают отсчеты дискретного сигнала с частотой тактовых имО пульсов. На К,-й такт на входе блока2 и на первом входе коммутатора 8появляется К,-й отсчет Я, на выходепервого элемента 7, задержки и навтором входе коммутатора 8 - (К"1)"йотсчет Я, и т,д., при этом на выходе (К -1)-го элемента 7 к - задержки и на К,-м входе коммутатора 8первый отсчет Б,. Таким образом, наК,-м такте через первые К информационных входов коммутатора 8 К, отсчетов сигнала подаются на первыевходы умножителей 9.,-9 К , на вторыеКэвходы которых поступают коды значенийэлементов первой строки матрицыА,(а-а ) с выходов узлов 10- 10 памяти, Узел 10 (3 = 1,К) содержит К соединенных последовательнорегистров сдвига, в которых хранятсяв виде двоичных кодов элементы 1-гостолбца матрицы А к . Взвешенные отсчеты сигнала суммируются в сумматоре 11, т.е. вычисляется сумма Ц,К,= 2 .8.,11На (К +1)-м такте к информационнымыходам коммутатора 8 подключены егонформационные входы с второго по(К,+ 1)-й, в результате чего на первыевходы умножителей поступают отсчетыБ,-Б. На вторые входы умножителей 9,-9 к подаются элементы второй стро- ки матрицы Ак, с выходов узлов 10 10 к, памяти. В результате на сумма- торе вычисляется сумма ц 2 = .- а . х х Б 1- 1Ч 2Таким образом, последовательно вы 10 числяются суммы ч = 2 а Б., приг 21 1 ф этом на (2 К -1)-м такте первый вычис 1лительный блок 2 заканчивает преобразование по основанию Кпервых К, отсчетов сигнала.Первая из К, вычисленных сумм Ц, через первый выход переключателя 3,1 ( на К-м такте переписывается в элемент 12 задержки второго вычислительного блока 22. На остальных К-х тактах 20 переключатель 3, включен на второй вход и остальные (К,-1) вычисляемых сумм 0; 1 = 2, К являющиеся коэффицивнтами преобразования по Хаароподобному базису с номерами (в+ 1)- 25 (ш 1+К 1-1), поступают на вход регистров 4, первого блока, на которые подаются тактовые импульсы в течение Ктактов.Следующие К тактов, начиная с 2 К,-го, первый вычислительный блок производит преобразование следующих К вхоДных отсчетов (Б К +1)-Б 2 к и т.д.После М-го такта на вход первого 35 вычислительного блока начинают поступать отсчеты следующей выборки, составленной из М отсчетов, а сумматор 11 за Ктактов вычисляет последние К -1 коэффициентов преобразования 40 предыдущей выборки с порядковыми но-мерами с (И-К+2)-го по М-й, которые через переключатель 3, поступают на вход группы регистров 4 1 сдвига,На следующем такте первый вычислительный блок 2 вычисляет первую сумму О, от первых К отсчетов второй выборки. На этом такте из блока синхронизации подается стробирующий им- пульс на вход разрешения записи пер вой группы регистров сдвига второго блока, разрешающий поступление коэффициентов преобразования из группы регистров 4 сдвига в соответствующую группу регистров 5, сдвига, 55Второй вычислительный блок 2 работает следующим образом. Записанная с выхода блока 2, через переключатель 3 на К -м такте в элемент 12 задерж 1 1ки сумма 0 подается на первый входЪумножителя 13, на второй вход которого поступает первый элемент первойстроки матрицы А к с узла 14 памяти.Узел 14 памяти содержит К последогвательно соединенных регистров сдвига, в которых последовательно записаны в виде двоичных кодов столбцы матрицы Ак, На следующих К 2-1 тактахна второй вход умножителя 13 последовательно подаются элементы первогостолбца матрицы А к -а 2 а з,а к 22 цВзвешенные значения Ц 1 с выхода умножителя подаются на первый вход сумматора 15, выход которого подключенк входу регистра 161 сдвига. На второй вход сумматора через ключ 1 подключен выход регистра 16 к . Ключ 17в течение этих К 2 тактов закрыт, поэтому на второй вход сумматора 15 втечение первых К 2 тактов поступаетуровень логического 0. При этом нарегистрах 16, - 16 к сдвига записанысоответственно значения произведенийц а , 0 ,аЯ а О, ана выходе сумматора - значениеа .1На 2 К -м такте в элемент 12 задержкизаписывается значение Я второй группы отсчетов сигнала Б к +, -Б 2 к, которое в умножителе 13 перемножается свторым элементом а, первой строкиматрицы А и сумматор 15 производитсуммирование текущего результата умножения,со значением произведенияЯа 1, предыдущего цикла обработки,котооое поступает на второй вход сумматора 15 через открытый ключ 17 свыхода Х -го регистра сдвига. На этомтакте тактовые импульсы подаются врегистры 16, - 16 сдвига и информацияк 2в них сдвигается, при этом в первомрегистре 16 сдвига записывается произведение ,а кпредыдущего циклаобработки. На следующем (2 К 1+1)мтакте в умножителе 13 Я умножается1на элемент а и суммируется созначением Я,а , предыдущего цикла свыхода К 2-го регистра сдвига, т.е.формируется частичная сумма Р 2= Я,а 2 + Я 1 а . Таким образом осуществляется К -2 последовательных формирований частичных сумм РЗРк 2в течение следующих тактов. Далеепроцесс формирования частичных суммпродолжается со значениями ЯЗ 1,На (К К )-м такте на выходесумматора 15 значение5 10 15 Р 1 - 01 а 11 +Ч а 1 г+..+ 0 а 1 к,г кгкоторое через переключатель 3 вклюценный на этом такте на первый выходпоступает на третий вычислительныйблок 2 З и записывается вего элемент12 задержки. На следующих Ктактахпереключатель Зг включен на второйвыход и остальные Ксумм Р 11д - 01 а ,3 2,К, являющиеся коЬэффициентами преобразования по Хааропгдобному базису с номерами (ш +1)(ш+К -1).-поступают на вход регистров4 сдвига второй группы первого блока.Следующие К, К тактов, начиная с(КК+К,)-го такта, второй вычислительный блок производит преобразование следующих Ксумм Ц г"фгс выхода вычислительного блока21 и т.д.Последующие вычислительные блоки2-2работают аналогичным образом,На входы разрешения записи второйгруппы регистров 5-5, сдвига стробирующие импульсы разрешения записиподаются тогда, когда полностью заполнены регистры сдвига 4,-4соответствующих групп второго блока, т.е,перезапись информации осуществляетсяна (И+К;)-м такте, Переключатель 3подключает к выходу свой первый входв течение К тактов с задержкой наК Зов = Кмюкс(К, - 1), где К,= шах (К ; К, , К , ) тактов относительно момента поступления навход устройств Я-го отсчета, и через него на выход процессора поступают первые К коэффициентов преобразования, задержанные в элементе 18 задержки на К тактов. Необходимость использования линии задержки возникаетлишь в том случае, когда хотя бы одинК ь = 1,ибольше К . В случае,когда К,К для всех= 1,и, отсутствует необходимость использованиялинии задержки и формирования отдельных стробирующих импульсов разрешения записи для каждой группы регистров сдвига в отдельности, можно вырабатывать единый импульс с учетом максимального К 1 -" 1 и 1На следующих тактах переключатель3 подключает к выходу второй вход,на тактовые входы регистров 5,-5 ,сдвига второй группы подается такто.вая частота, с которой оставшиеся 20 25 30 35 40 45 50 55 И-К коэффициентов преобразования последовательно передаются на выход процессора. Необходимость введения (КК+1)-го регистра сдвига в (и) (и)-ю группу регистров сдвига второго блока связано стем, что отсутствие этого регистра сдвига при выводе коэффициентов привело бы к потере (К + 1)-го коэффициента преобразования (в случае отсутствия записи их в буферную память), так как первый тактовый импульс вызывает сдвиг информации на один регистр сдвига и на этом такте на выходе процессора имеется (К+2) -й коэффициент преобразования.Формула из обретенияПроцессор для преобразования цифровых сигналов по Хааро-подобным базисам, содержащий И (И = К, К. е, К, И - размер преобразования) вычислительных блоков, блок синхронизации, первый и второй блоки регистров сдвига и и переключателей, причем выход 1-го ( = 1,и) вычислительного блока подключен к первому информационному входу -го переключателя, первый вход которого подключен к информационному входу (+1)-го вычислительного блока, а выход и-го переключателя является информационным выходом процес- сора, при этом первый вычислительный блок содержит 2(К,-1) элементов задержки, коммутатор, К умножителей, К, узлов памяти и сумматор, причем первый информационный вход коммутатора соединен с входом первого элемента задержки и является информационным входом процессора, выход 3-го1 - 1, 2, , (К 1-3)3 элемента задержки подключен к входу (3+1)-го элемента задержки и (3+1)-му информационному входу коммутатора, (2 К 1-1)-й инФормационный вход которого подключен к выходу 2(К,-1)-го элемента задержки, 3-й (3 = 1, , К ) выход коммутатора подключен к первому входу 1-го умножителя, выход 3-го узла памяти подключен к информационному входу 3-го узла памяти и второму входу 3-го умножителя, выход котоиого подключен к 3-му входу сумматора, выход которого является выходом первого вычислительного блока, первый блок регистров сдвига содержит игрупп регистров сдвига по (К,-1)К;1 + 1 1фпоследовательно соединенных регистровсдвига в д-й (1 = 1,и) группе, второй блок регистров сдвига содержит и групп регистров сдвига, по (К;-1) К; , К последовательно сседи-Ч , Ьненных регистров сдвига в -й ( = 1,К) группе и одну группу регистров сдвига из (К)К +11-х последовательно соединенных регистров сдвига, выход -го Ц = 1, (К; - .1) (К, К)1 О регистра сдвига 1.-й ( = 1,и) группы первого блока регистров сдвига подключен к информационному входу 1-го регистра сдвига ь-й группы второго блоков регистров сдвига, выход 1 Б (К;-1), Х 1 К;-го регистра сдвига 1-й (х = 1,и) группы второго блока регистров сдвига, подключен к информационному входу первого регистра сдвига (1+1)-й группы второго 20 блска регистров сдвига, Выход (Х ,- -1)К+1 -го регистра сдвига (и)-й группы второго блока регистров сдви" га подключен к второму информационному входу и-го переключателя., второй выход 1-го (1 = 1,и) переключателя ,подключен к информационному входу первого регистра сдвига д-й группы первого блока регистров сдвига, первый выход первой группы блока синхрс- Зб низации подключен к управляющим входам узлов памяти и коммутатора первого вычислительного блока, -й (1,и) выход второй группы блока синхронизации подключен к управляющему входу -го переключателя, а вход запуска блока синхронизации является входом запуска процессора, о т л и - ч а ю щ и й с я тем, что, с целью упрощения, ок содержит элемент за б держки, причем -й (1 = 2,и) вычислительный блок содержит тактируемый элемент задержки умножитель, узел памяти, сумматор, ключ и группу из К; последовательно сседикеккьх регистров сдвига, при этом икфарь";ионный вход тактируемого элемента задержки является икформационным входом 1-го вычислител кого блока, выход тактируемого элемента задержки подключен к первому входу умножителя, Выход узла памяти подключен к информационному входу 1 зла памяти и второму Входу умнсжителя, выксд которого подключен к первому входу сумматора, второй Вход стсрсго пбдключен к выходу К 1-го регистра сдвига, выход сумматора подключен к информационному Входу пеивого регистра сдви."а н является информационным вь 1 ходсм -го вычислителькогс блока, при этом -й выход первой гругиы блока синхронизации подключен к управляющему входу узла памяти и тактовым Входам регистров сдвига х-гс Вычислительного блока, х-й (1 = 1,и) выход второй группы олока сикхгокизации подключен к тактовому входу тактируемсго элемента задержки (+1)-гс вычислительного блока, х-й ( = 1 и) выход третьей группы блока синхронизации подключен к управляющему Входу ключа (+1)-го вычислительного блока, тактсвые входы реги трОВ сдВига 1 х (1. = 1 и 1 ) групп перьсго и втсрсгс блоков регистров сдвига подключены к -м выходам соответственно четвертой и пятой групп блока синхронизации, а входы разрещеккя запис . регистров сдвига 1-Й ( . 1 и) группы втоссго Олока сдвиговых регистров подключены к х-пц выходу юестсй группы блока синхронизации, при этом информационный выход и-го Вычислительного блока подключен к входу элемекта задержки, выход которого подключен к первому информационному вхсцу и-гс переключателя1418745 ЗЛЯ Й 1 .ПО йод ОНО Составитель А.БарановТехред М.Ходанич Карре едактор В.Петраш силье аказ 4156 н 130 изюодетвенно-полиграфическое предприятие, г, Ужгород, ул. Проектная,Тираж 70 Государстве елям изобрет сква, Ж,Подпиого комитета СССРий и открытийаушская наб д, 4

СмотретьЗаявка

4185975, 22.01.1987

ХОЗРАСЧЕТНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ "АЛГОРИТМ" ПРИ УЗБЕКСКОМ НАУЧНО-ПРОИЗВОДСТВЕННОМ ОБЪЕДИНЕНИИ "КИБЕРНЕТИКА" АН УЗССР

ИСМАГИЛОВ ИЛЬЯС ИДРИСОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: базисам, подобным, преобразования, процессор, сигналов, хааро, цифровых

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/6-1418745-processor-dlya-preobrazovaniya-cifrovykh-signalov-po-khaaro-podobnym-bazisam.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для преобразования цифровых сигналов по хааро подобным базисам</a>

Предыдущий патент: Устройство для моделирования процесса обслуживания заявок

Следующий патент: Устройство для вычисления скользящего спектра

Случайный патент: Приспособление для закрепленияпартии образцов при испытаниина усталость