Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

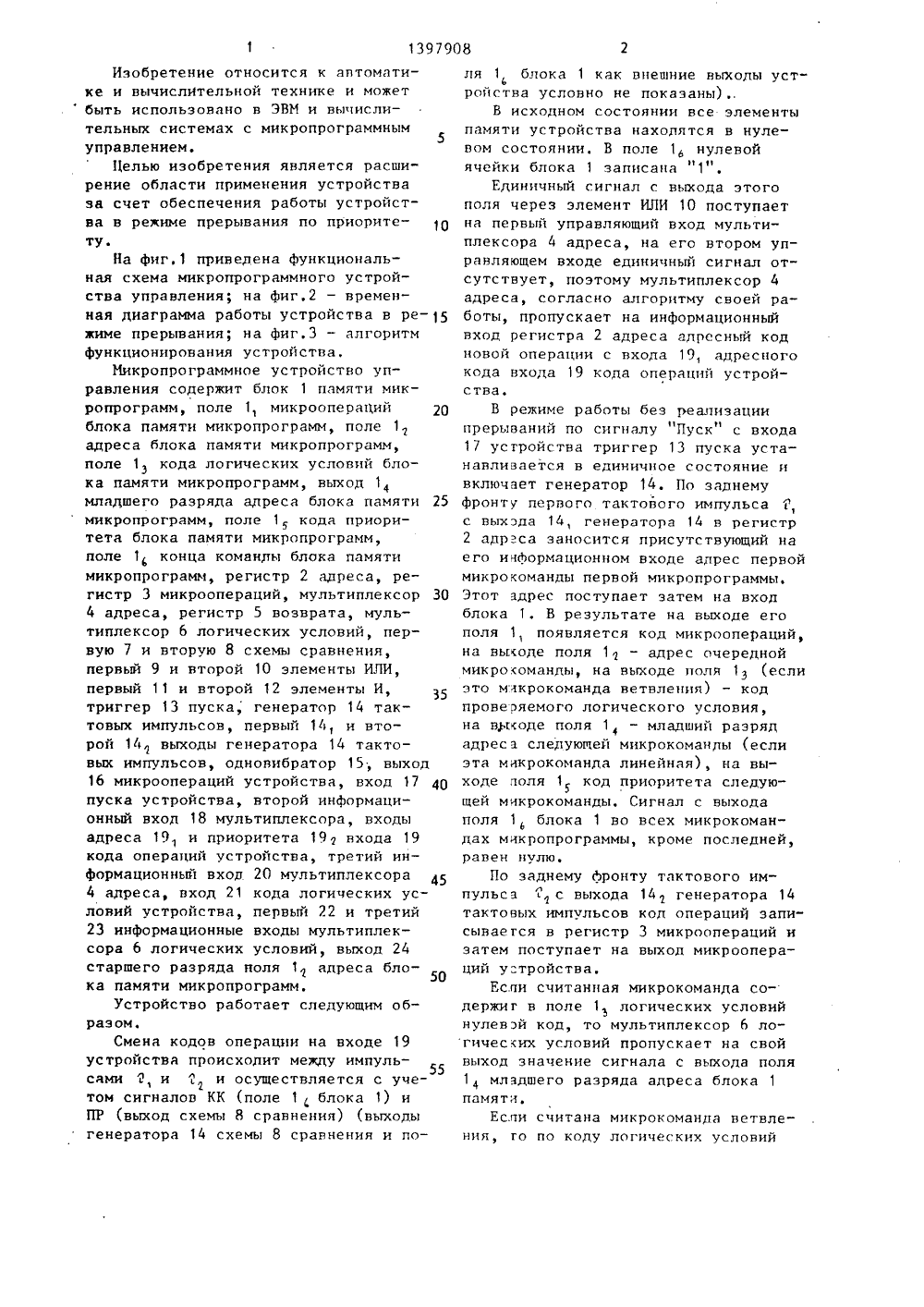

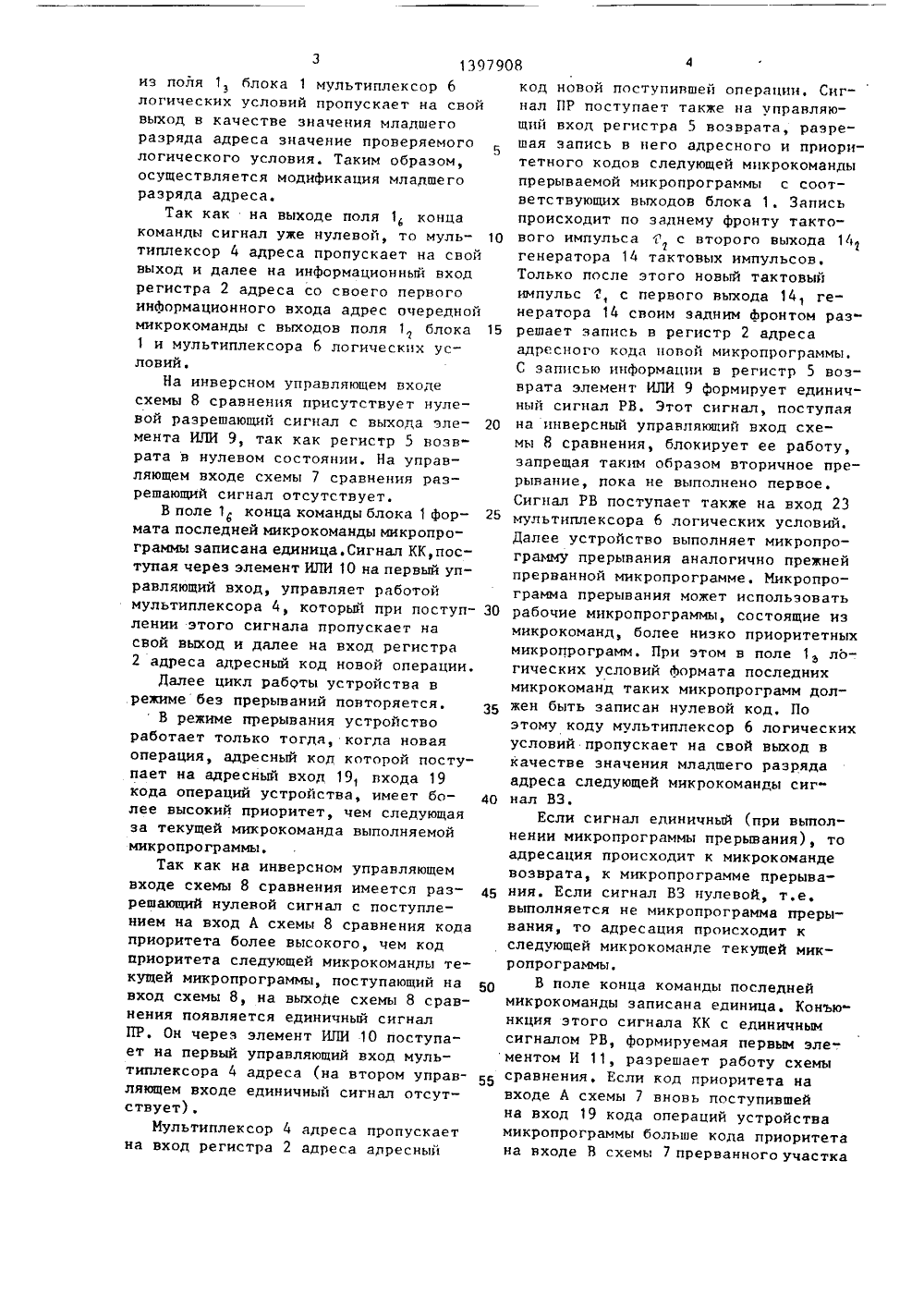

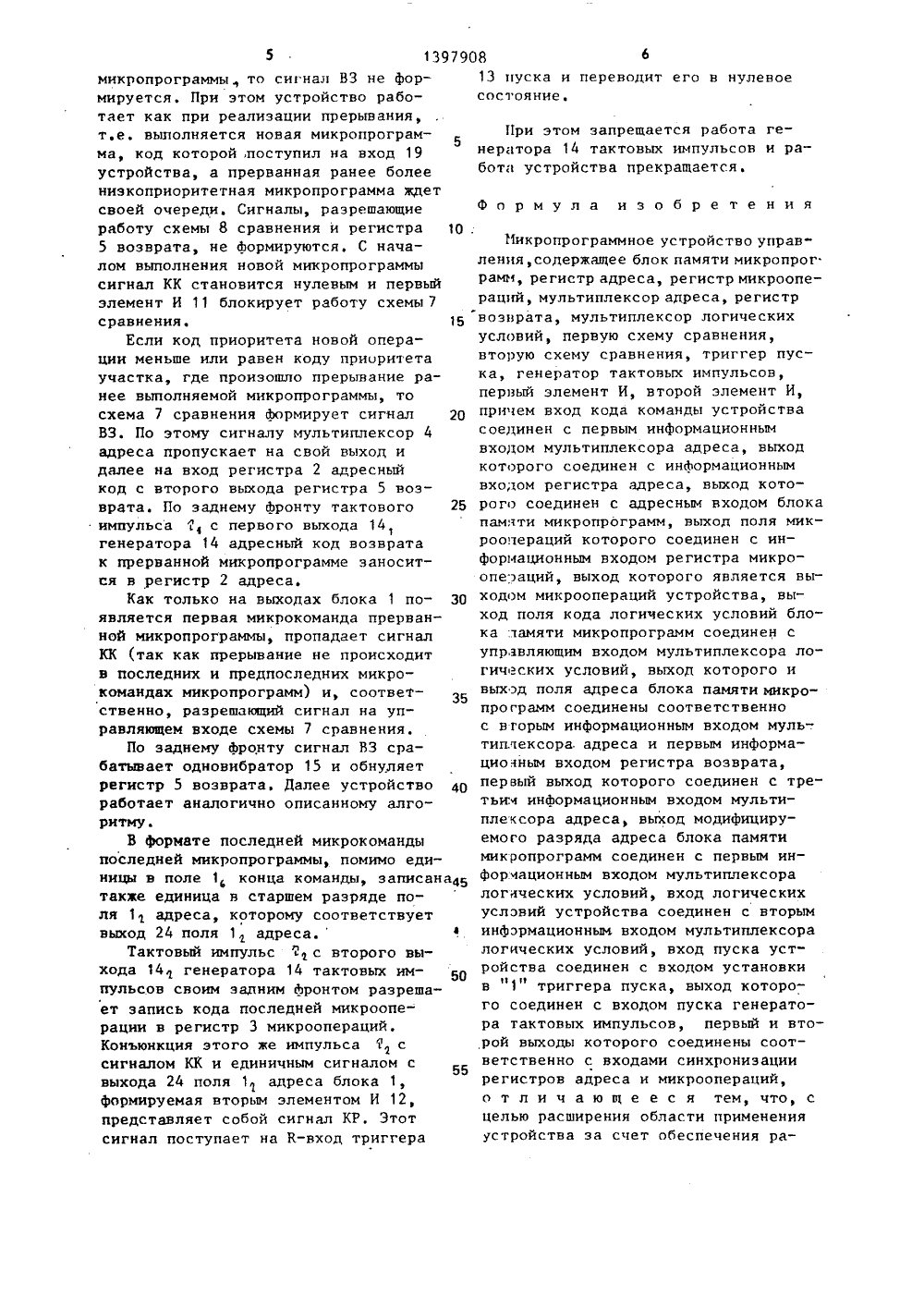

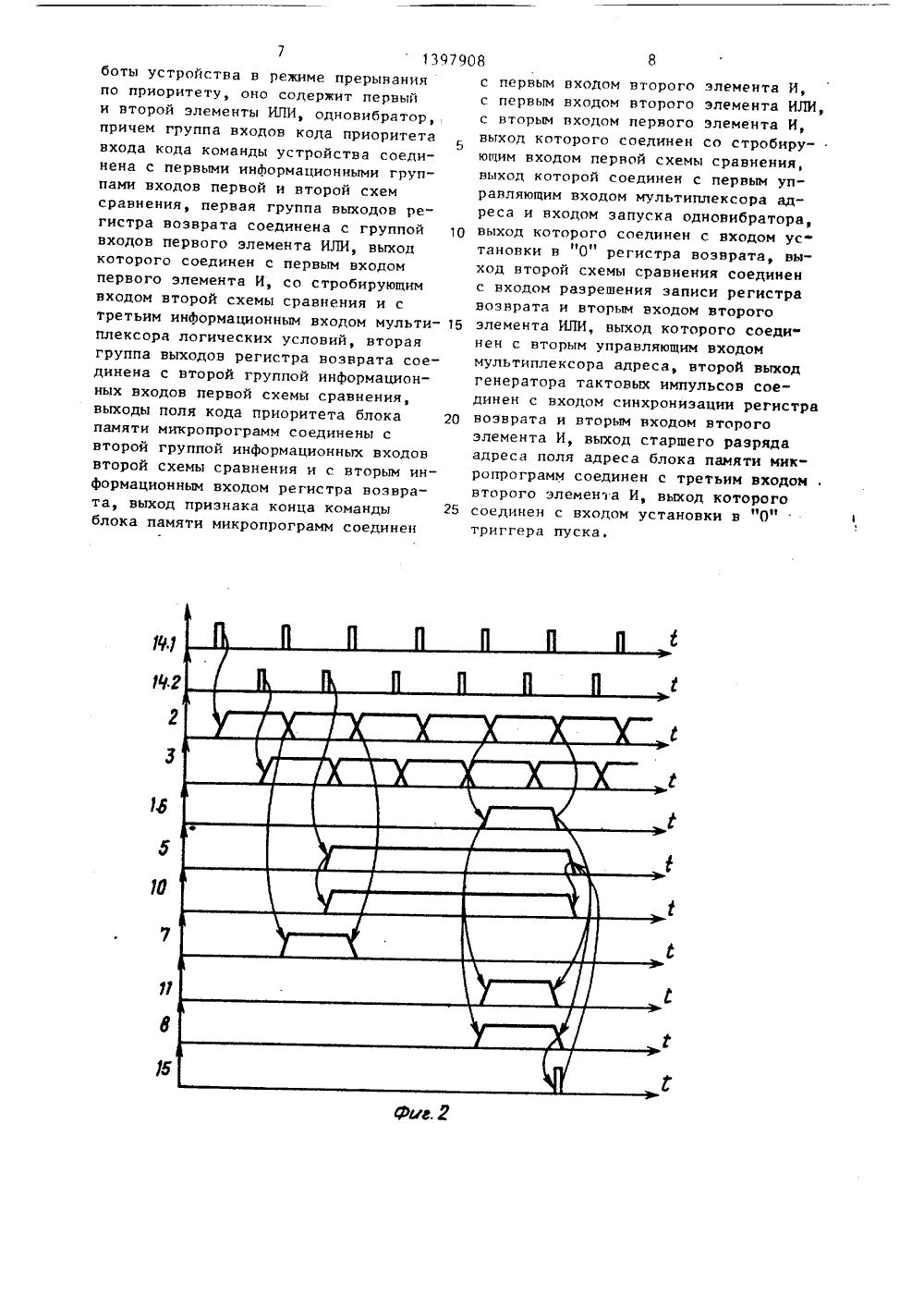

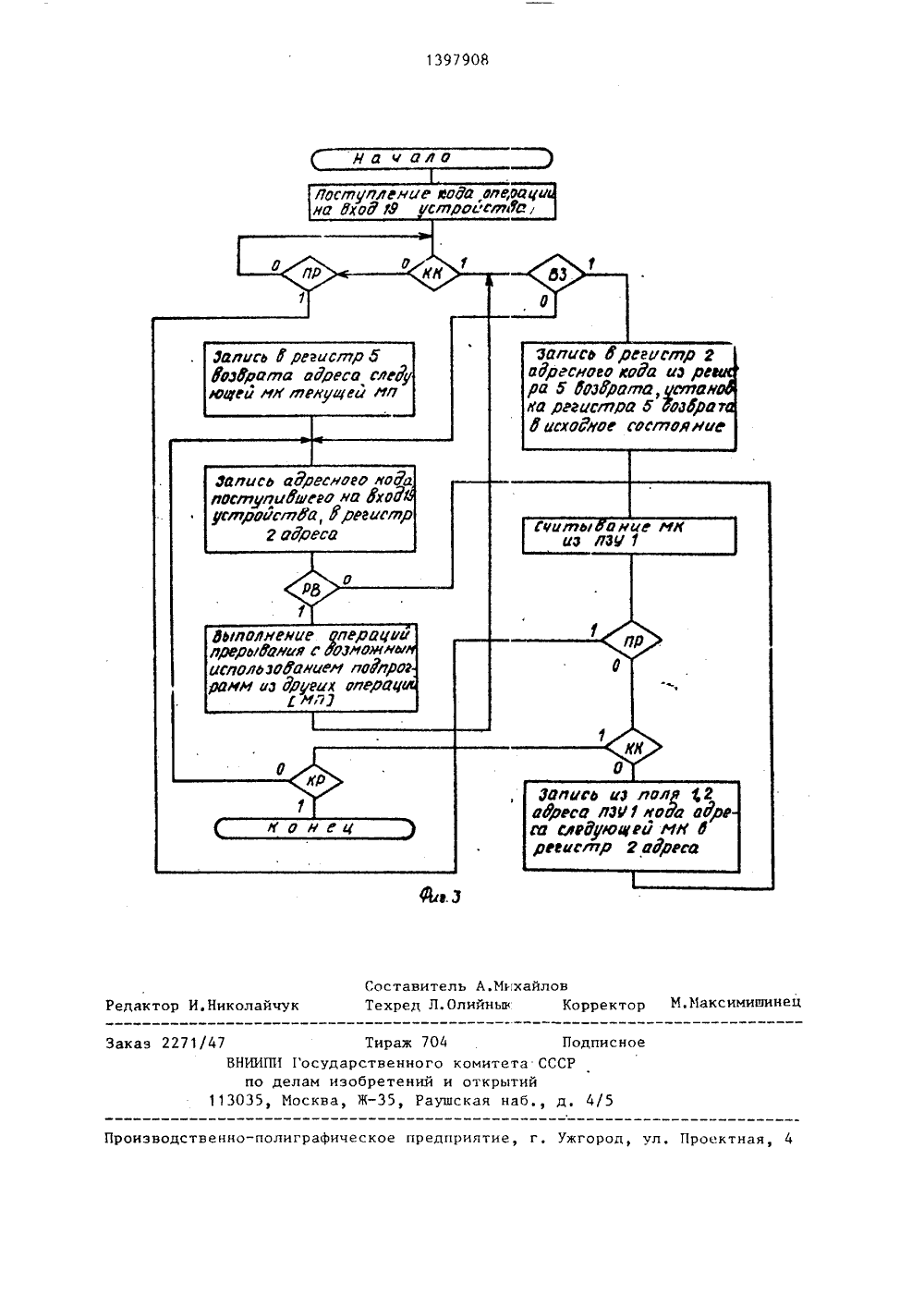

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ЯО 13979 А 1 54 С 06 Р 9 11 00 ОПИСАНИЕ ИЗОБРЕТЕНИЯ л. У 19 о, В.С.Х Е.Марков ченко,С.Н.Тка идетельство СССР6 Р 9/22, 1980.етельство СССР06 Р 9/22,(54) МИКРОПРОГРАММНРАВЛЕНИЯ(57) Изобретениетике и вычислите УСТРОЙСТВО УПотносится к автома ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свУ 955060, кл. С 0Авторское свидУ 1142833, кл. СС 06 Р 11/00, 198 жет. быть использовано в ЭВМ и вычислительных системах с микропрограммнымуправлением. Пелью изобретения является расширение области примененияустройства за счет обеспечения работы устройства в режиме прерывания поприоритету. Устройство содерзит блок1 памяти микропрограмм, регистр 2 адреса, регистр 3 микроопераций, мультиплексор 4 адреса, регистр 5 возврата, мультиплексор 6 логических условий, первую 7 и вторую 8 схемысравнения, первый 9 и второй 10 эле-.менты ИЛИ, первый 11 и второй 12 элементы И, триггер 13 пуска, генератор14 тактовых импульсов, одновибраторИзобретение относится к автоматике и вычислнтельной технике и может быть использовано в ЭВМ и вычислительных системах с микропрограммнымуправлением.Целью изобретения является расширение области применения устройства за счет обеспечения работы устройства в режиме прерывания по приоритету.На фиг,1 приведена функциональная схема микропрограммного устройства управления; на фиг,2 - временная диаграмма работы устройства в ре жиме прерывания; на фиг.3 - алгоритм функционирования устройства.Микропрограммное устройство управления содержит блок 1 памяти микропрограмм, поле 1, микроопераций 20 блока памяти микропрограмм, поле 12 адреса блока памяти микропрограмм, поле 1 кода логических условий блоЭка памяти микропрограмм, выход 1 младшего разряда адреса блока памяти 25 микропрограмм, поле 1 кода приоритета блока памяти микропрограмм, поле 1 конца команды блока памяти микропрограмм, регистр 2 адреса, регистр 3 микроопераций, мультиплексор 30 4 адреса, регистр 5 возврата, мультиплексор 6 логических условий, первую 7 и вторую 8 схемы сравнения, первый 9 и второй 10 элементы ИЛИ, первый 11 и второй 12 элементы И, триггер 13 пуска, генератор 14 тактовых импульсов, первый 14, и второй 142 выходы генератора 14 тактовых импульсов, одновибратор 15, выход 16 микроопераций устройства, вход 17 40 пуска устройства, второй информационный вход 18 мультиплексора, входы адреса 191 и приоритета 192 входа 19 кода операций устройства, третий информационньп вход 20 мультиплексора 4 адреса, вход 21 кода логических условий устройства, первый 22 и третий 23 информационные входы мультиплексора 6 логических условий, выход 24 старшего разряда поля 12 адреса блока памяти микропрограмм.Устройство работает следующим образом.Смена кодов операции на входе 19 устройства происходит между импульсами 7 и 7 и осуществляется с уче 1 2том сигналов КК (поле 1блока 1) и ПР (выход схемы Я сравнения) (выходы генератора 14 схемы 8 сравнения и поля 1 блока 1 как внешние выходы устройства условно не показаны)В исходном состоянии все элементыпамяти устройства находятся в нулевом состоянии. В поле 1 нулевойячейки блока 1 записана "1".Единичный сигнал с выхода этогополя через элемент ИЛИ 10 поступаетна первый управляющий вход мультиплексора 4 адреса, на его втором управляющем входе единичньп сигнал отсутствует, поэтому мультиплексор 4адреса, согласно алгоритму своей работы, пропускает на информационныйвход регистра 2 адреса адресный кодновой операции с входа 19, адресногокода входа 19 кода операций устройства.В режиме работы без реализациипрерываний по сигналу цПускц с входа17 устройства триггер 13 пуска устанавливается в единичное состояние ивключает генератор 14. По заднемуфронту первого тактового импульса Г,с выхэда 14, генератора 14 в регистр2 адрса заносится присутствующий наего ицформационном входе адрес первоймикрокоманды первой микропрограммы,Этот адрес поступает затем на входблока 1. В результате на выхопе егополя 1, появляется код микроопераций,на выходе поля 12 - адрес очередноймикроомацды, на выходе поля 1 З (еслиэто млкрокоманда ветвления) - кодпроверяемого логического условия,на виоде поля 1 - младший разрядадреса следующей микрокоманды (еслиэта мнкрокоманда линейная), на выходе поля 1 код приоритета следующей мцкрокоманды. Сигнал с выходаполя 1 блока 1 во всех микрокомандах микропрограммы, кроме последней,равен нулю.По заднему фронту тактового импульса 7 с выхода 142 генератора 14тактовых импульсов код операций записывается в регистр 3 микроопераций изатем поступает на выход микроопераций у:тройства.Если считанная микрокоманда содержиг в поле 1 логических условийнулевой код, то мультиплексор 6 логических условий пропускает на свойвыход значение сигнала с выхода поля1 младшего разряда адреса блока 1памятя,Если считана микрокомацда ветвления, го по коду логических условий08 13979 из поля 1 з блока 1 мультиплексор 6 логических условий пропускает на свой выход в качестве значения младшего разряда адреса значение проверяемого5 логического условия. Таким образом, осуществляется модификация младшего разряда адреса.Так как на выходе поля 1 конца команды сигнал уже нулевой, то муль типлексор 4 адреса пропускает на свой выход и далее на информационный вход регистра 2 адреса со своего первого информационного входа адрес очередной микрокоманды с выходов поля 1 блока 15 1 и мультиплексора 6 логических условий.На инверсном управляющем входе схемы 8 сравнения присутствует нулевой разрешающий сигнал с выхода зле мента ИЛИ 9, так как регистр 5 возврата в нулевом состоянии. На управляющем входе схемы 7 сравнения разрешающий сигнал отсутствует.В поле 1 конца команды блока 1 фор мата последней микрокоманды микропрограммы записана единица. Сигнал КК,поступая через элемент ИЛИ 10 на первый управляющий вход, управляет работой мультиплексора 4, который при поступ лении этого сигнала пропускает на свой выход и далее на вход регистра 2 адреса адресный код новой операции.Далее цикл работы устройства в режиме без прерываний повторяется.В режиме прерывания устройство работает только тогда, когда новая операция, адресный код которой поступает на адресный вход 191 входа 19 кода операций устройства, имеет бо лее высокий приоритет, чем следующая за текущей микрокоманда выполняемой микропрограммы.Так как на инверсном управляющем входе схемы 8 сравнения имеется раз решающий нулевой сигнал с поступлением на вход А схемы 8 сравнения кода приоритета более высокого, чем код приоритета следующей микрокоманды текущей микропрограммы, поступающий на 50 вход схемы 8, на выходе схемы 8 сравнения появляется единичный сигнал ПР. Он через элемент ИЛИ 10 поступает на первый управляющий вход мультиплексора 4 адреса (на втором управ 55 ляющем входе единичный сигнал отсутствует).Мультиплексор 4 адреса пропускает на вход регистра 2 адреса адресный код новой поступившей операции. Сигнал ПР поступает также на управляющий вход регистра 5 возврата, разрешая запись в него адресного и приоритетного кодов следующей микрокоманды прерываемой микропрограммы с соответствующих выходов блока 1. Зались происходит по заднему фронту тактового импульса Г с второго выхода 142 генератора 14 тактовых импульсов, Только после этого новый тактовый импульс 7, с первого выхода 141 генератора 14 своим задним фронтом разрешает запись в регистр 2 адреса адресного кода новой микропрограммы. С записью информации в регистр 5 возврата элемент ИЛИ 9 формирует единичный сигнал РВ. Этот сигнал, поступая на инверсный управляющий вход схемы 8 сравнения, блокирует ее работу, запрещая таким образом вторичное прерывание, пока не выполнено первое, Сигнал РВ поступает также на вход 23 мультиплексора 6 логических условий. Далее устройство выполняет микропрограмму прерывания аналогично прежней прерванной микропрограмме, Микропрограмма прерывания может испольэовать рабочие микропрограммь, состоящие из микрокоманд, более низко приоритетных микропрограмм. При этом в поле 1 лоз гических условий формата последних микрокоманд таких микропрограмм должен быть записан нулевой код, По этому коду мультиплексор 6 логических условий пропускает на свой выход в качестве значения младшего разряда адреса следующей микрокоманды сиг" нал ВЗ.Если сигнал единичный (при выполнении микропрограммы прерывания), то адресация происходит к микрокоманде возврата, к микропрограмме прерывания. Если сигнал ВЗ нулевой, т.е, выполняется не микропрограмма прерывания, то адресация происходит к следующей микрокоманде текущей микропрограммы.В поле конца команды последней микрокоманды записана единица. Конъю" нкция этого сигнала КК с единичным сигналом РВ, формируемая первым эле". ментом И 11, разрешает работу схемы сравнения. Если код приоритета на входе А схемы 7 вновь поступившей на вход 19 кода операций устройства микропрограммы больше коЛа приоритета на входе В схемы 7 прерванного участка5 139790микропрограммыто сигнал ВЗ не формируется. При этом устройство работает как при реализации прерывания,т.е. выполняется новая микропрограмма, код которой, поступил на вход 19устройства, а прерванная ранее болеенизкоприоритетная микропрограмма ждетсвоей очереди, Сигналы, разрешающиеработу схемы 8 сравнения и регистра 10,5 возврата, не формируются. С началом выполнения новой микропрограммысигнал КК становится нулевым и первыйэлемент И 11 блокирует работу схемы 7сравнения. 15Если код приоритета новой операции меньше или равен коду приоритетаучастка, где произошло прерывание ранее выполняемой микропрограммы, тосхема 7 сравнения формирует сигнал 20ВЗ. По этому сигналу мультиплексор 4адреса пропускает на свой выход идалее на вход регистра 2 адресныйкод с второго выхода регистра 5 возврата. По заднему фронту тактового 25импульса 7 с первого выхода 141генератора 14 адресный код возвратак прерванной микропрограмме заносится в регистр 2 адреса.Как только на выходах блока 1 появляется первая микрокоманда прерванной микропрограммы, пропадает сигналКК (так как прерывание не происходитв последних и предпоследних микрокомандах микропрограмм) и, соответственно, разрешающий сигнал на управляющем входе схемы 7 сравненияПо заднему фронту сигнал ВЗ срабатывает одновибратор 15 и обнуляетрегистр 5 возврата. Далее устройство 40работает аналогично описанному алгоритму.В формате последней микрокомандыпоследней микропрограммы, помимо единицы в поле 1 конца команды, записана 45также единица в старшем разряде поля 1 адреса, которому соответствуетвыход 24 поля 1 адреса.Тактовый импульс 7 с второго выхода 14 1 генератора 14 тактовых импульсов своим запним фронтом разрешает запись кода последней микрооперации в регистр 3 микроопераций,Конъюнкция этого же импульса 7 ссигналом КК и единичным сигналом свыхода 24 поля 11 адреса блока 1,формируемая вторым элементом И 12,представляет собой сигнал КР. Этотсигнал поступает на К-вход триггера 13 пуска и переводит его в нулевоесостояние11 ри этом запрещается работа генератора 14 тактовых импульсов и работа устройства прекращается. Формула изобретения 11 икропрограммное устройство управ" ления,содержащее блок памяти микропрог. рами, регистр адреса, регистр микроопераций, мультиплексор адреса, регистр возврата, мультиплексор логических условий, первую схему сравнения, вторую схему сравнения, триггер пуска, генератор тактовых импульсов, первый элемент И, второй элемент И, причем вход кода команды устройства соединен с первым информационным входом мультиплексора адреса, выход которого соединен с информационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход поля микроопераций которого соединен с информационным входом регистра микроопе аций, выход которого является вы - ходом микроопераций устройства, выход поля кода логических условий блока 1 амяти микропрограмм соединен с управляющим входом мультиплексора логических условий, выход которого и выход поля адреса блока памяти микропрограмм соединены соответственно с вгорым информационным входом мультип.чексора. адреса и первым информационным входом регистра возврата, первый выход которого соединен с третьим информационным входом мультиплексора адреса, выход модифицируемого разряда адреса блока памяти микропрограмм соединен с первым информационным входом мультиплексора логических условий, вход логических услэвий устройства соединен с вторым инфэрмационным входом мультиплексора логических условий, вход пуска уст" ройства соединен с входом установки в "1" триггера пуска, выход которого соединен с входом пуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистров адреса и микроопераций, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения ра 7 1 З 9 боты устройства в режиме прерывания по приоритету, оно содержит первый и второй элементы ИЛИ, одновибратор причем группа входов кода приоритета входа кода команды устройства соединена с первыми информационными группами входов первой и второй схем сравнения, первая группа выходов регистра возврата соединена с группой входов первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, со стробирующим входом второй схемы сравнения и с третьим информационным входом мультиПлексора логических условий, вторая группа выходов регистра возврата соединена с второй группой информационных входов первой схемы сравнения, выходы поля кода приоритета блока памяти микропрограмм соединены с второй группой информационных входов второй схемы сравнения и с вторым информационным входом регистра возврата, выход признака конца команды блока памяти микропрограмм соединен 7908с первым входом второго элемента И,с первым входом второго элемента ИЛИ,с вторым входом первого элемента И, 5выход которого соединен со стробирующим входом первой схемы сравнения,выход которой соединен с первым управляющим входом мультиплексора адреса и входом запуска одновибратора, 1 О выход которого соединен с входом установки в нОн регистра возврата, выход второй схемы сравнения соединенс входом разрешения записи регистравозврата и вторым входом второго 1 Б элемента ИЛИ, выход которого соединен с вторым управляющим входоммультиплексора адреса, второй выходгенератора тактовых импульсов соединен с входом синхронизации регистра 20 возврата и вторым входом второгоэлемента И, выход старшего разрядаадреса поля адреса блока памяти микропрограмм соединен с третьим входомвторого элемента И, выход которого 25 соединен с входом установки в 0"триггера пуска.1397908 Составитель А.МихайловТехред Л,Олийньв Корректор М.Максимишине дактор И. Никол Заказ 2271/47 ПодписноСР д, 4/5 Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4 Тираж 704 ВНИИПИ Государственного по делам изобретений и 113035, Москва, Ж, Раушкомитета открытий ская наб

СмотретьЗаявка

4144404, 10.11.1986

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, МАРКОВ ПЕТР ЕВГЕНЬЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 11/36

Метки: микропрограммное

Опубликовано: 23.05.1988

Код ссылки

<a href="https://patents.su/6-1397908-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Приоритетное устройство

Случайный патент: Многоцилиндровый двухтактный двигатель-компрессор