Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

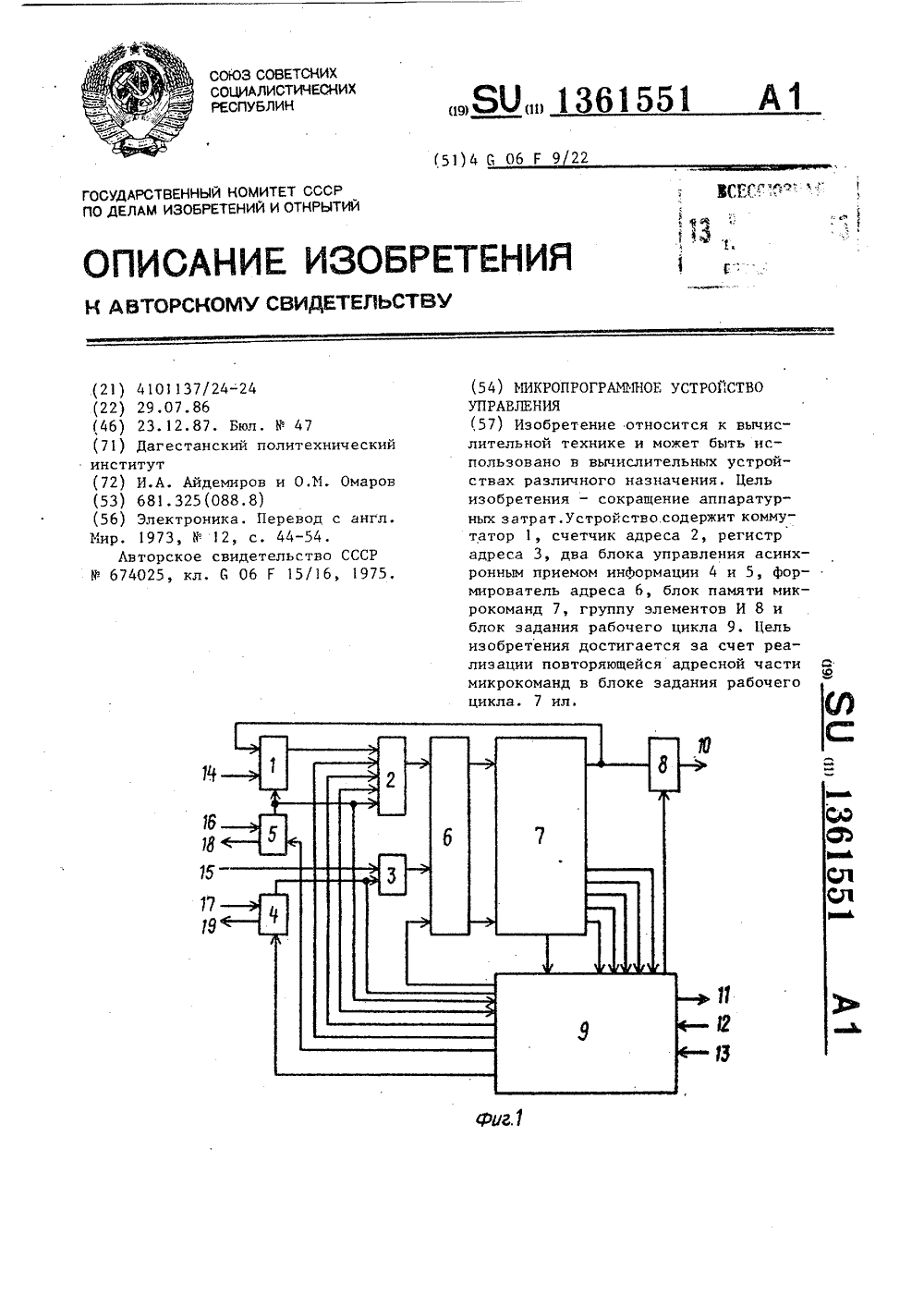

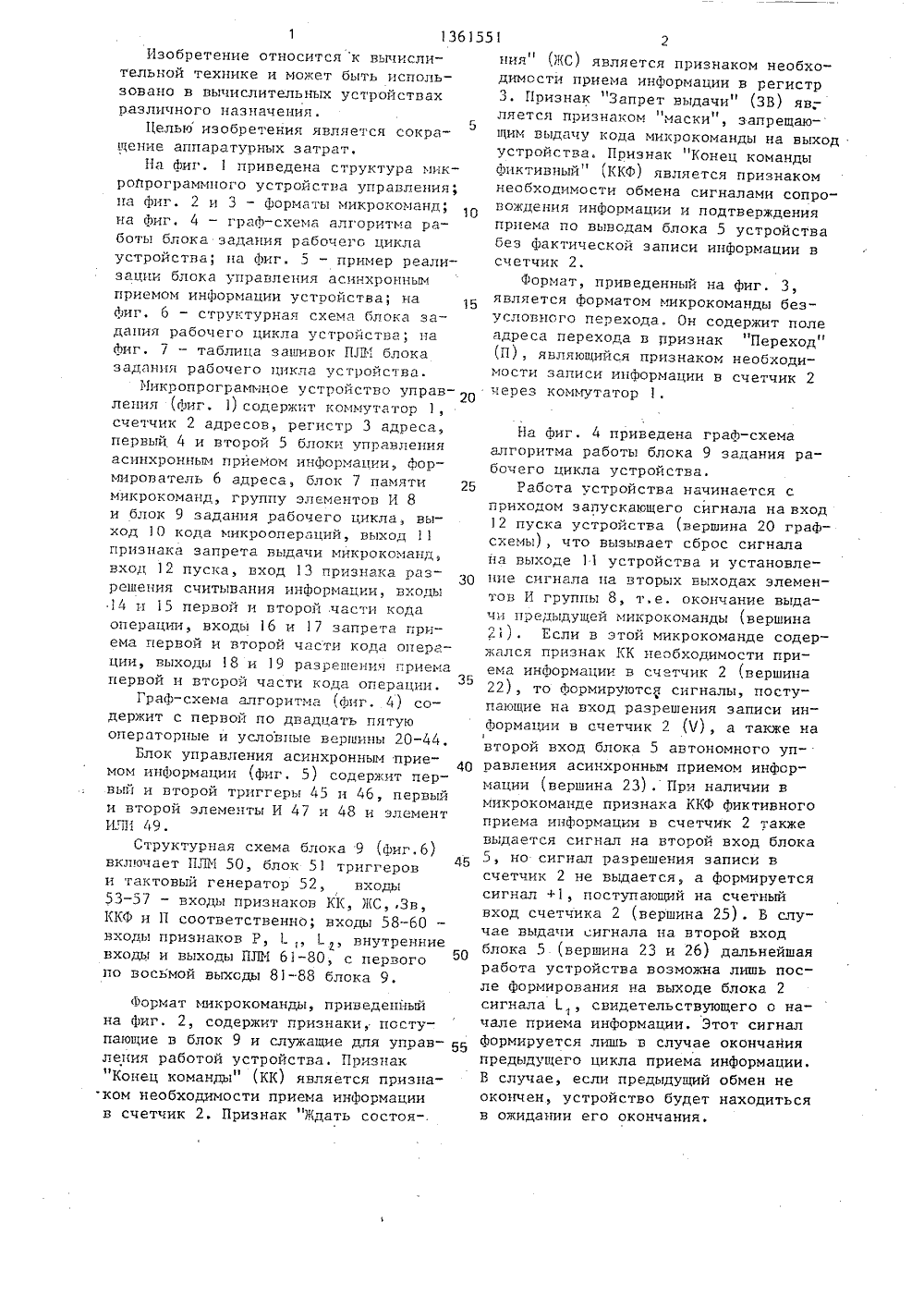

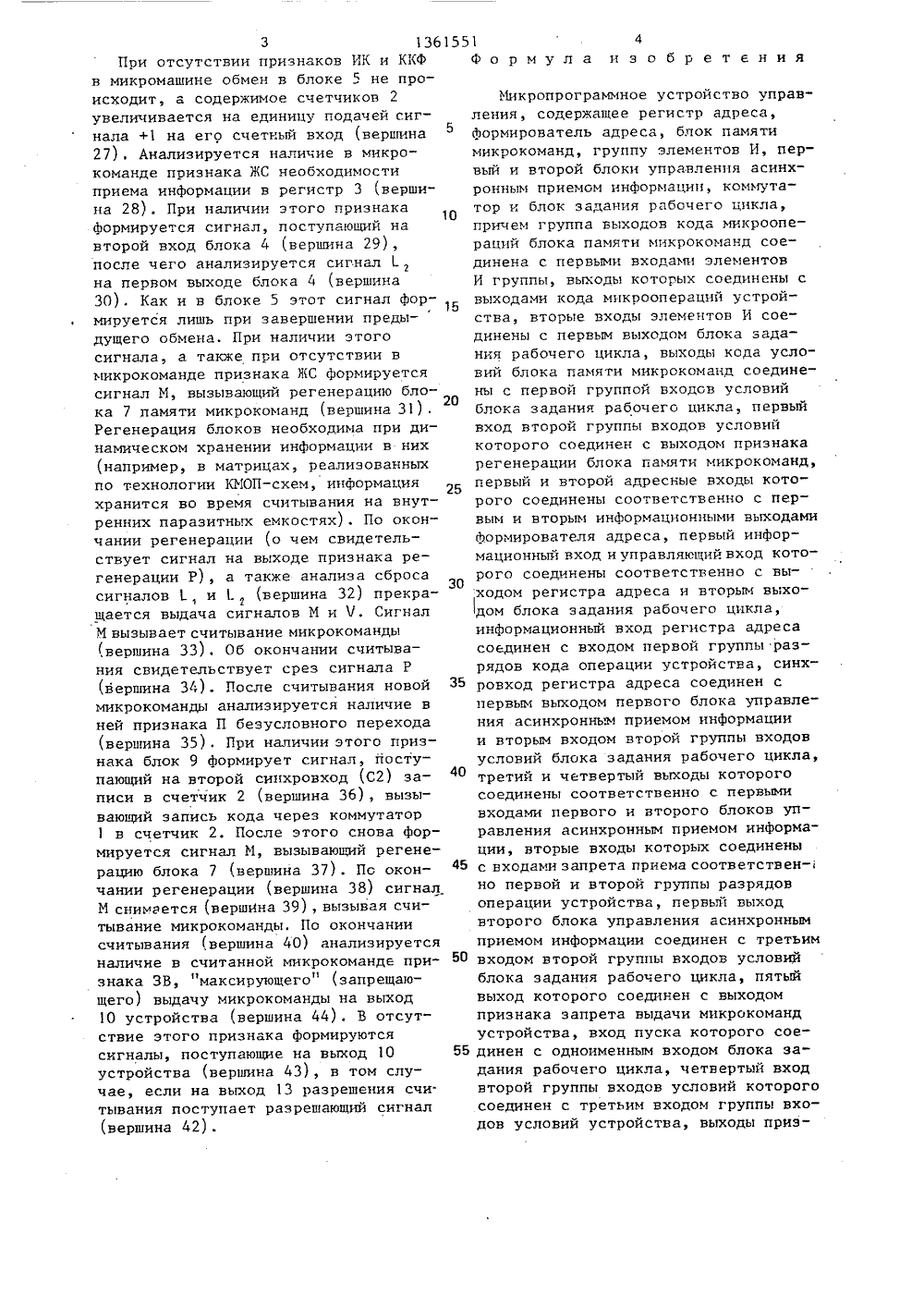

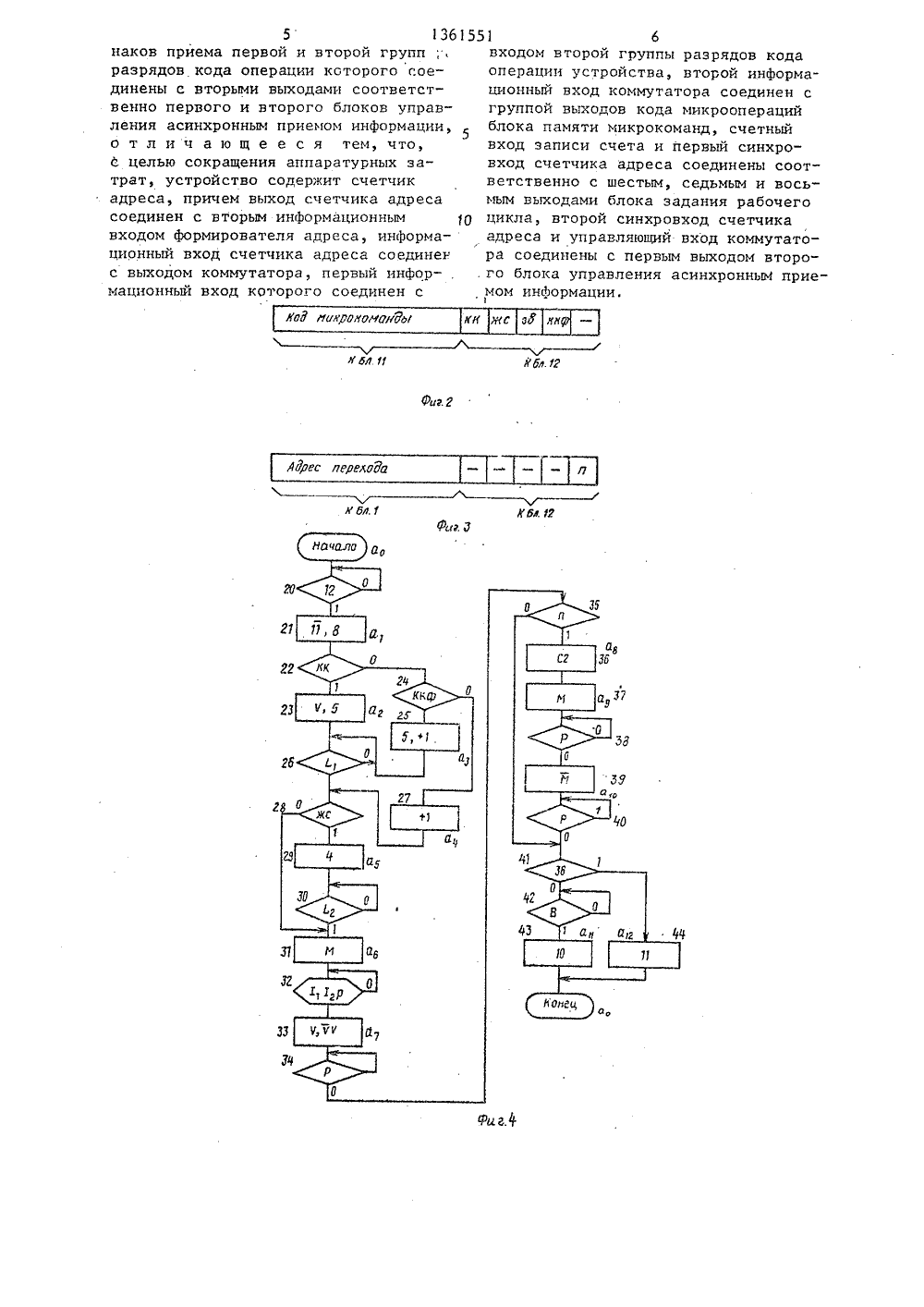

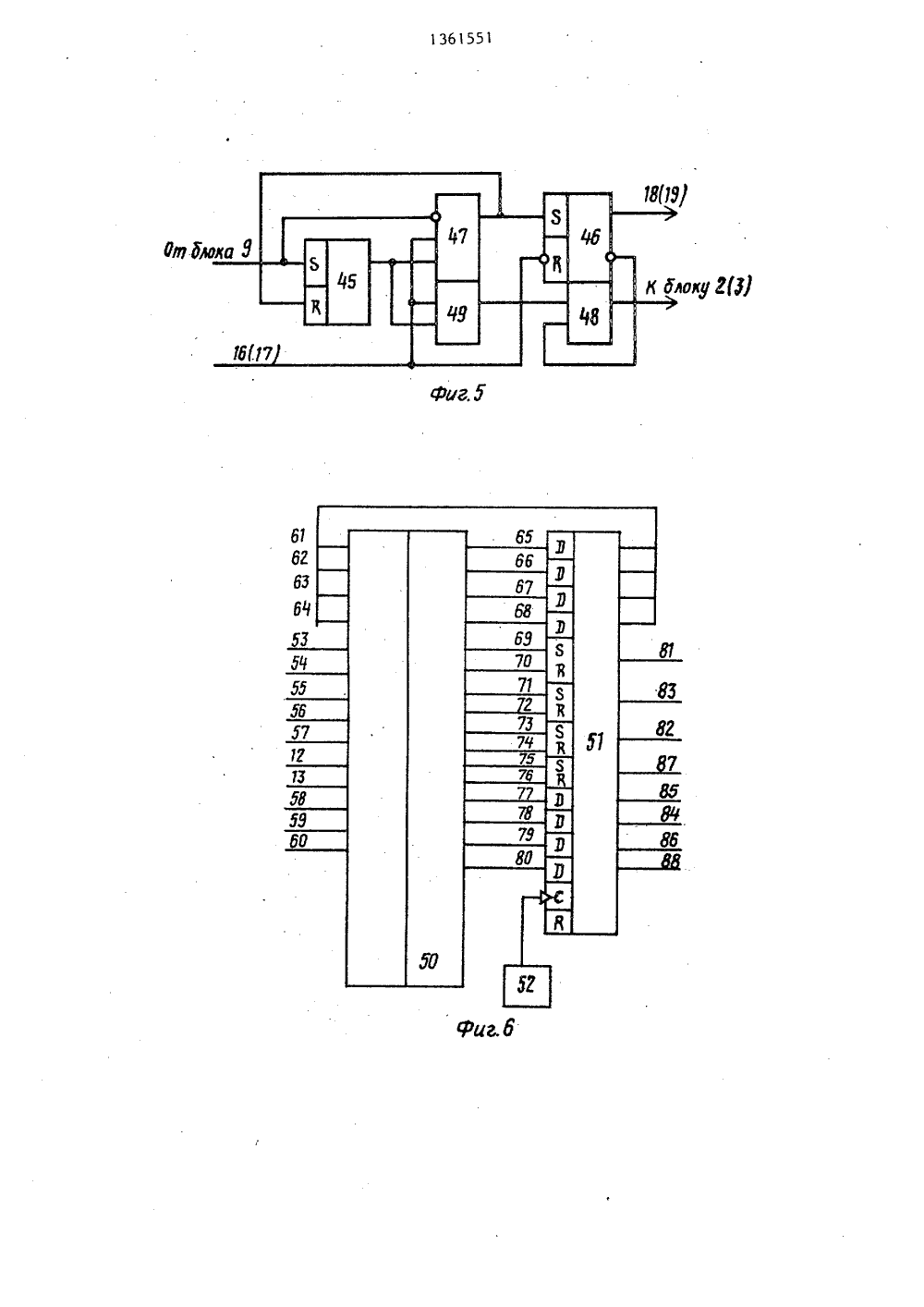

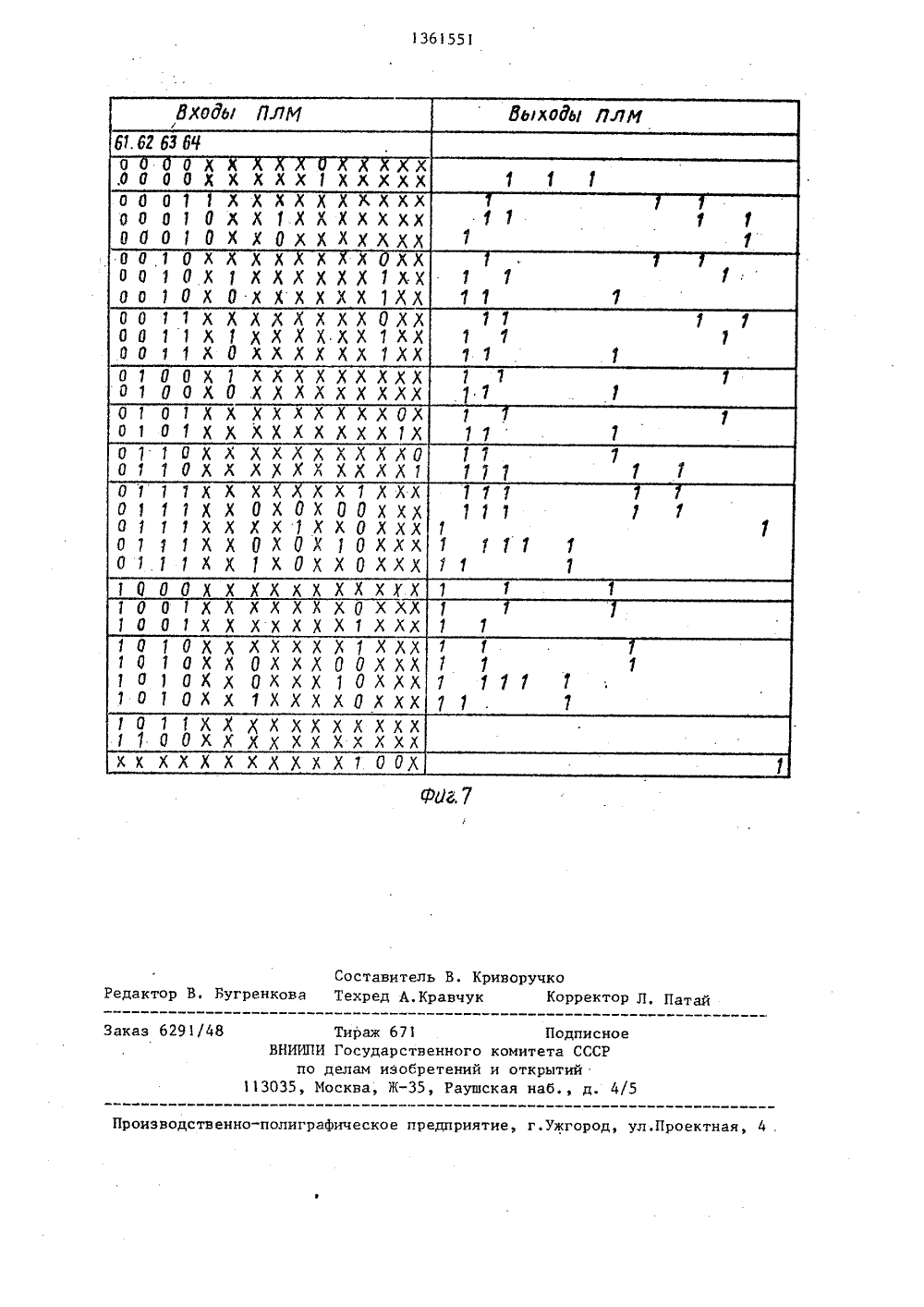

(51)4 О 0 ИСАНИЕ ИЗОБРЕТЕНИ ПЬСТВУ АВТОРСКОМУ СВ 7/24-248687. Бюл, Кф нский политехнический ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(57) Изобретение относится к вычислительной технике и может быть исьзовано в вычислительных устро ствах различного назначения. Цельизобретения - сокращение аппаратурных затрат. Устройство. содержит коммутатор 1, счетчик адреса 2, регистр адреса 3, два блока управления асинхронным приемом информации 4 и 5, формирователь адреса 6, блок памяти микрокоманд 7, группу элементов И 8 и блок задания рабочего цикла 9. Цель изобретения достигается за счет реализации повторяющейся адресной части с микрокоманд в блоке задания рабочего цикла. 7 ил.Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствахразличного назначения.5Целью изобретения является сокращение аппаратурных затрат,На фиг, 1 приведена структура микропрограммного устройства управления;па фиг. 2 и 3 - форматы микрокоманд;на йиг. 4 - граф-схема алгоритма работы блока зацания рабочего циклаустройства; на фиг. 5 - пример реализации блока управления асинхроннымприемом информации устройства; надиг. 6 - структурная схема блока задания рабочего цикла устройства; найиг, 7 - таблица зашивок ПЛ блоказадания рабочего цикла устройства.1 икропрограммное устройство управлепия (фиг. 1) содержит коммутатор 1,счетчик 2 адресов, регистр 3 адреса,первый 4 и второй 5 блоки управленияасинхронным прйемом информации, формирователь 6 ацреса, блок 7 памятимикрокоманд, группу элементов И 8и блок 9 задания рабочего цикла, выход 10 кода микроопераций, выход 11признака запрета выдачи микрокоманд,вход 12 пуска, вход 13 признака разрешения считывания информации, входы14 и 15 первой и второй части кодаоперации, входы 16 и 17 запрета приема первой и второй части кода операции, выходы 18 и 19 разрешения приемапервой и второй части коца операции.Граф-схема алгоритма (фиг. 4) содержит с первой по двадцать пятуюоператорные и условные вершины 20-44,Блок управления асинхронным приемом информации (фиг. 5) содержит первый и второй триггеры 45 и 46, первыйи второй элементы И 47 и 48 и элементИ.П 49,Структурная схема блока 9 (фиг.6)включает ПЛИ 50, блок 51 триггерови тактовый генератор 52, входы53-57 - входы признаков КК, ЖС, Зв,ККФ и П соответственно; входы 58-60 -входы признаков Р, 1 , 1. , внутренниевходы и выходы ПЛМ 61-80, с первогопо восьмой выходы 81-88 блока 9. Формат микрокоманды, приведенйый на фиг. 2, содержит признаки, поступающие в блок 9 и служащие для управ ления работой устройства. Признак Конец команды" (КК) является признаком необходимости приема информации в счетчик 2. Признак "Ждать состоя-. ния (ЖС) является признаком необходимости приема информации в регистр 3. Гризнак "Запрет выдачи" (ЗВ) яв; ляется признаком маски, запрещающим выдачу кода микрокоманды на выход устройства. Признак "Конец команды фиктивный" (ККФ) является признаком необходимости обмена сигналами сопровождения информации и подтверждения приема по выводам блока 5 устройства без фактической записи информации в счетчик 2.Формат, приведенный на фиг, 3, является форматом микрокоманды безусловного перехода, Он содержит поле адреса перехода в признак Переход" (П), являюшийся признаком необходимости записи информации в счетчик 2 через коммутатор 1. На фиг. 4 приведена грай-схема алгоритма работы блока 9 задания рабочего цикла устройства.Работа устройства начинается с приходом запускающего сигнала на вход 12 пуска устройства (вершина 20 граф- схемы), что вызывает сброс сигнала на выходе 11 устройства и установление сигнала на вторых выходах элементов И группы 8, т.е, окончание выдачи предыдущей микрокоманды (вершина 21), Если в этой микрокоманде содержался признак КК необходимости приема информации в счетчик 2 (вершина 22), то дюрмируются сигналы, поступающие на вход разрешения записи информации в счетчик 2 (Ч), а также на 1второй вход блока 5 автономного управления асинхронным приемом информации (вершина 23). При наличии в микрокоманде признака ККФ фиктивного приема информации в счетчик 2 также выдается сигнал на второй вход блока 5, но сигнал разрешения записи в счетчик 2 не выдается, а формируется сигнал +1, поступающий на счетный вход счетчика 2 (вершина 25) . В случае выдачи сигнала на второй вход блока 5 (вершина 23 и 26),цальнейшая работа устройства возможна лишь после формирования на выходе блока 2 сигналасвидетельствующего о начале приема информации. Этот сигнал формируется лишь в случае окончания предыдущего цикла приема информации, В случае, если предыдущий обмен не окончен, устройство будет находиться в ожидании его окончания.1551 4 Формула из о бр етения 55 динен с одноименным входом блока задания рабочего цикла, четвертый вход второй группы входов условий которого соединен с третьим входом группы входов условий устройства, выходы приэ 3 136При отсутствии признаков ИК и ККФ в микромашине обмен в блоке 5 не происходит, а содержимое счетчиков 2 увеличивается на единицу подачей сигнала +1 на его счетный вход (вершина 27). Анализируется наличие в микрокоманде признака ЖС необходимости приема информации в регистр 3 (вершина 28). При наличии этого признака формируется сигнал, поступающий на второй вход блока 4 (вершина 29), после чего анализируется сигнал на первом выходе блока 4 (вершина 30), Как и в блоке 5 этот сигнал формируется лишь при завершении предыдущего обмена. При наличии этого сигнала, а также при отсутствии в микрокоманде признака ЖС формируется сигнал М, вызывающий регенерацию блока 7 памяти микрокоманд (вершина 31), Регенерация блоков необходима при динамическом хранении информации в них (например, в матрицах, реализованных по технологии КМОП-схем, информация хранится во время считывания на внутренних паразитных емкостях). По окончании регенерации (о чем свидетельствует сигнал на выходе признака регенерации Р), а также анализа сброса сигналови 1. (вершина 32) прекращается выдача сигналов М и Ч, Сигнал М вызывает считывание микрокоманды (вершина 33). Об окончании считыва - ния свидетельствует срез сигнала Р (вершина 34). После считывания новой микрокоманды анализируется наличие в ней признака П безусловного перехода (вершина 35). При наличии этого признака блок 9 формирует сигнал, йоступающий на второй синхровход (С 2) записи в счетчик 2 (вершина 36), вызывающий запись кода через коммутатор 1 в счетчик 2. После этого снова формируется сигнал М, вызывающий регенерацию блока 7 (вершина 37). Пс окончании регенерации (вершина 38) сигнал М снимается (вершина 39), вызывая считывание микрокоманды. По окончании считывания (вершина 40) анализируется наличие в считанной микрокоманде признака ЗВ, максирующего (запрещаю - щего) выдачу микрокоманды на выход 10 устройства (вершина 44), В отсутствие этого признака формируются сигналы, поступающие на выход 10 устройства (вершина 43), в том случае, если на выход 13 разрешения счи. тывания поступает разрешающий сигнал (вершина 42). 5 10 15 20 25 30 35 40 45 50 Микропрограммное устройство управления, содержащее регистр адреса, формирователь адреса, блок памяти микрокоманд, группу элементов И, первый и второй блоки управления асинхронным приемом информации, коммутатор и блок задания рабочего цикла, причем группа выходов кода микроопераций блока памяти микрокоманд соединена с первыми входами элементов И группы, выходы которых соединены с выходами кода микроопераций устройства, вторые входы элементов И соединены с первым выходом блока задания рабочего цикла, выходы кода условий блока памяти микрокоманд соединены с первой группой входов условий блока задания рабочего цикла, первый вход второй группы входов условий которого соединен с выходом признака регенерации блока памяти микрокоманд, первый и второй адресные входы которого соединены соответственно с первым и вторым информационными выходами формироватсля адреса, первый информационный вход и управляющий вход которого соединены соответственно с выходом регистра адреса и вторым выходом блока задания рабочего цикла, информационный вход регистра адреса соединен с входом первой группы разрядов кода операции устройства, синхровход регистра адреса соединен с первым выходом первого блока управления асинхронньм приемом информации и вторым входом второй группы входов условий блока задания рабочего цикла, третий и четвертый выходы которого соединены соответственно с первыми входами первого и второго блоков управления асинхронно приемом информации, вторые входы которых соединены с входами запрета приема соответствен- но первой и второй группы разрядов операции устройства, первый выход второго блока управления асинхронным приемом информации соединен с третьим входом второй группы входов условий блока задания рабочего цикла, пятый выход которого соединен с выходом признака запрета выдачи микрокоманд устройства, вход пуска которого соебЛ 11 иг.3 5 136 иаков приема первой и второй групп разрядов кода операции которого соединены с вторыми выходами соответственно первого и второго блоков управления асинхронным приемом информации, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит счетчик адреса, причем выход счетчика адреса соединен с вторым информационным входом Формирователя адреса, информационный вход счетчика адреса соединен с выходом коммутатора, первый инфор- . мационный вход которого соединен с 551 бвходом второй группы разрядов кодаоперации устройства, второй информационный вход коммутатора соединен сгруппой выходов кода микрооперацийблока памяти микрокоманд, счетныйвход записи счета и первый синхровход счетчика адреса соединены соответственно с шестым, седьмым и восьмым выходами блока задания рабочего 1 р цикла, второй синхровход счетчикаадреса и управляющий вход коммутатора соединены с первым выходом второ. го блока управления асинхронным приемом индюрмации.о о Оо 00 7 Х Х ХХХХХХХХ ОХ Х 1 ХХХХХХХ О Х Х ОХХ ХХХХХ ХХ Х Х ХХ 7 ХХХХХХ 7 ХХ О ХХХХХХ 7 ХХ 00, ОХ ОО 70 Х 00 ОХ ХХ Х Х ХХХХХ ХЯ ХХХХХХХ оотг 00 ХО ХХ ХХ ХХХОХ ХХ ХХ ХХХ 7 Х 00 1 ХХХХ ХХХ/0 ХХХХ ХХХХХ 077 0 ХХ 07 7 ОХХ Ог 7 01 0 71 07 71 07.7 7 Х Х Х Х Х Х Х Х Х Х 7 1 ХХ ХХХ ООХ Х Х ХХХХ ХОХХХ ХХХХХ 7 ХХХ а07 1717 7 7 70 ХХ 7 ОХХОХХ 7 ОХХ 0 7 7 ХХ 7 00 ХХ ХХ ХХ ХХ ХХ ХХ ХХХ ХХ ХХХ х аок ХХХ хХХх Фаа 7 Составитель В. КриворучкоТехред А.Кравчук Корректор Л. Патай Редактор В. Бугренкова 629/48 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Заказ Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4 0 0 0 0 оа О О 0 0 0 0 0 7 00 ХХХ Х ХХ ОХХ ХХХХХХ 7 ХХ ХХХХ ХХ 7 ХХ Х ХХ 7 ХХХ ОХ ОХ ООХХХ ХХ 7 ХХОХХХ ОХ ОХ ОХАХ 7 ХОХХОХХХ ХХХХ Х 7 ХХХ ОХХХ ООХХХ ОХ ХХ 7 ОХХХ 1 ХХХ ХОХХХ 7 777717

СмотретьЗаявка

4101137, 29.07.1986

ДАГЕСТАНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

АЙДЕМИРОВ ИГОРЬ АЙДЕМИРОВИЧ, ОМАРОВ ОМАР МАГАДОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.12.1987

Код ссылки

<a href="https://patents.su/6-1361551-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммный автомат

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Головкл пресса для наложения металлической оболочки на кабелбнб1е изделия