Кодек блочных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

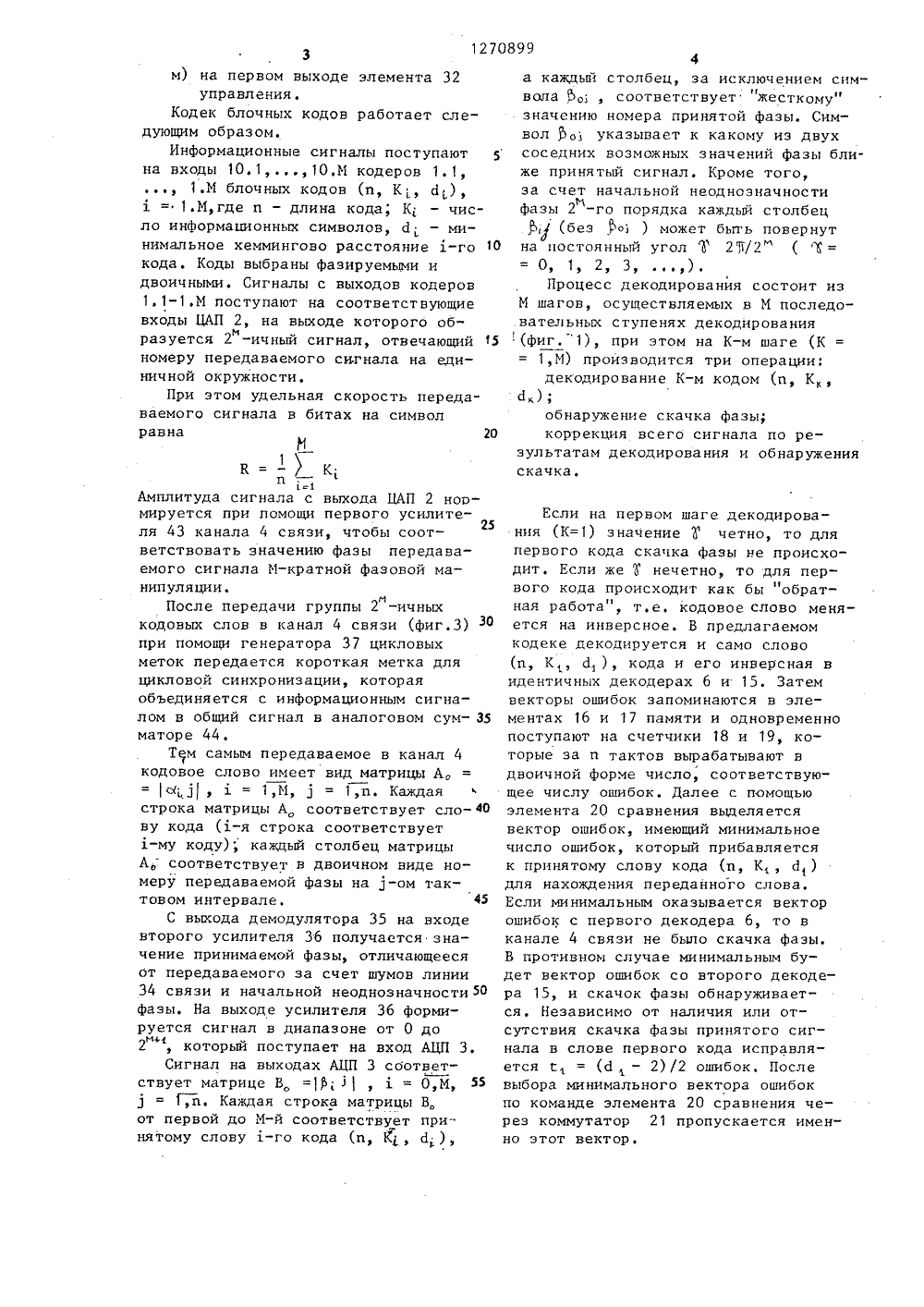

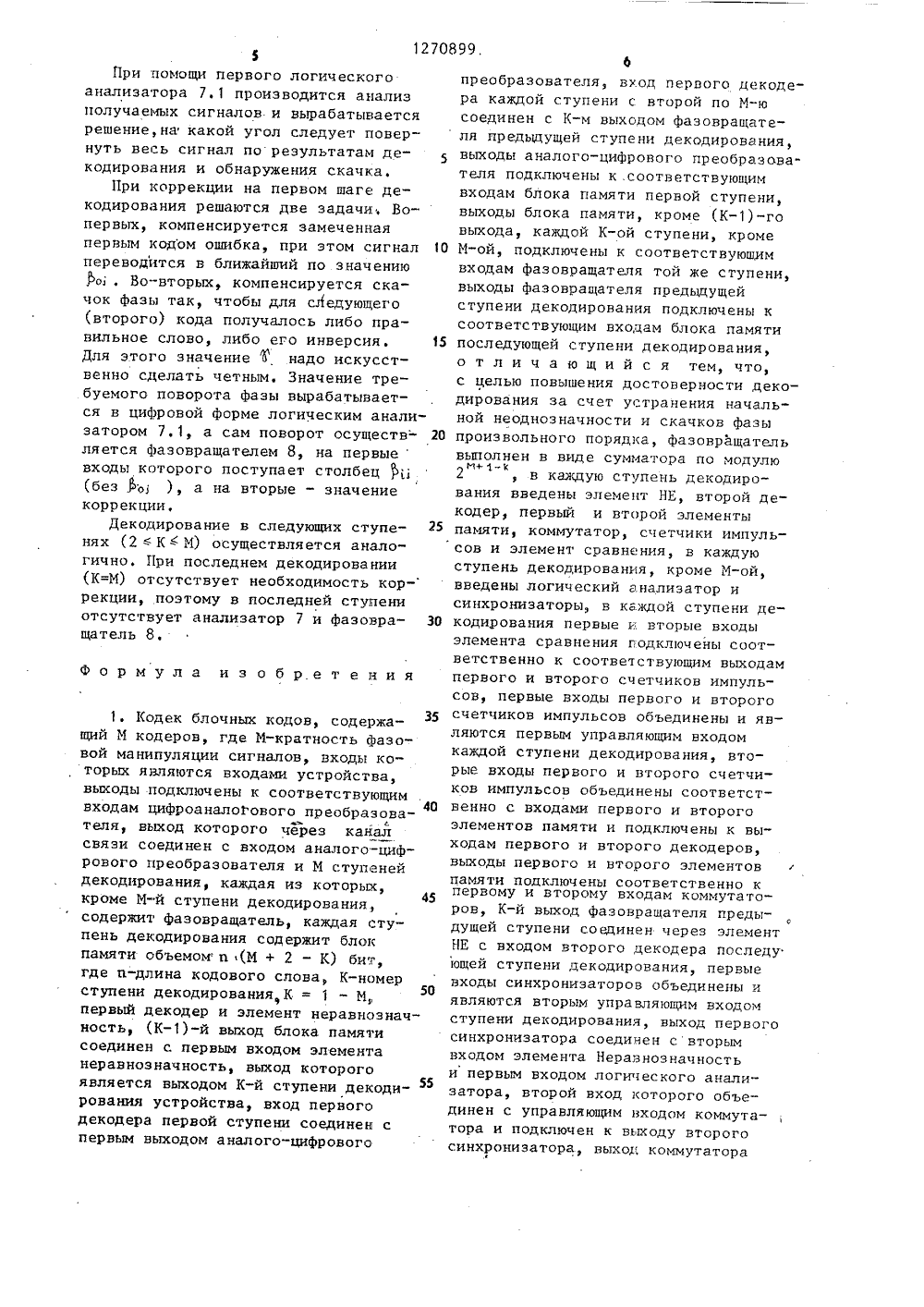

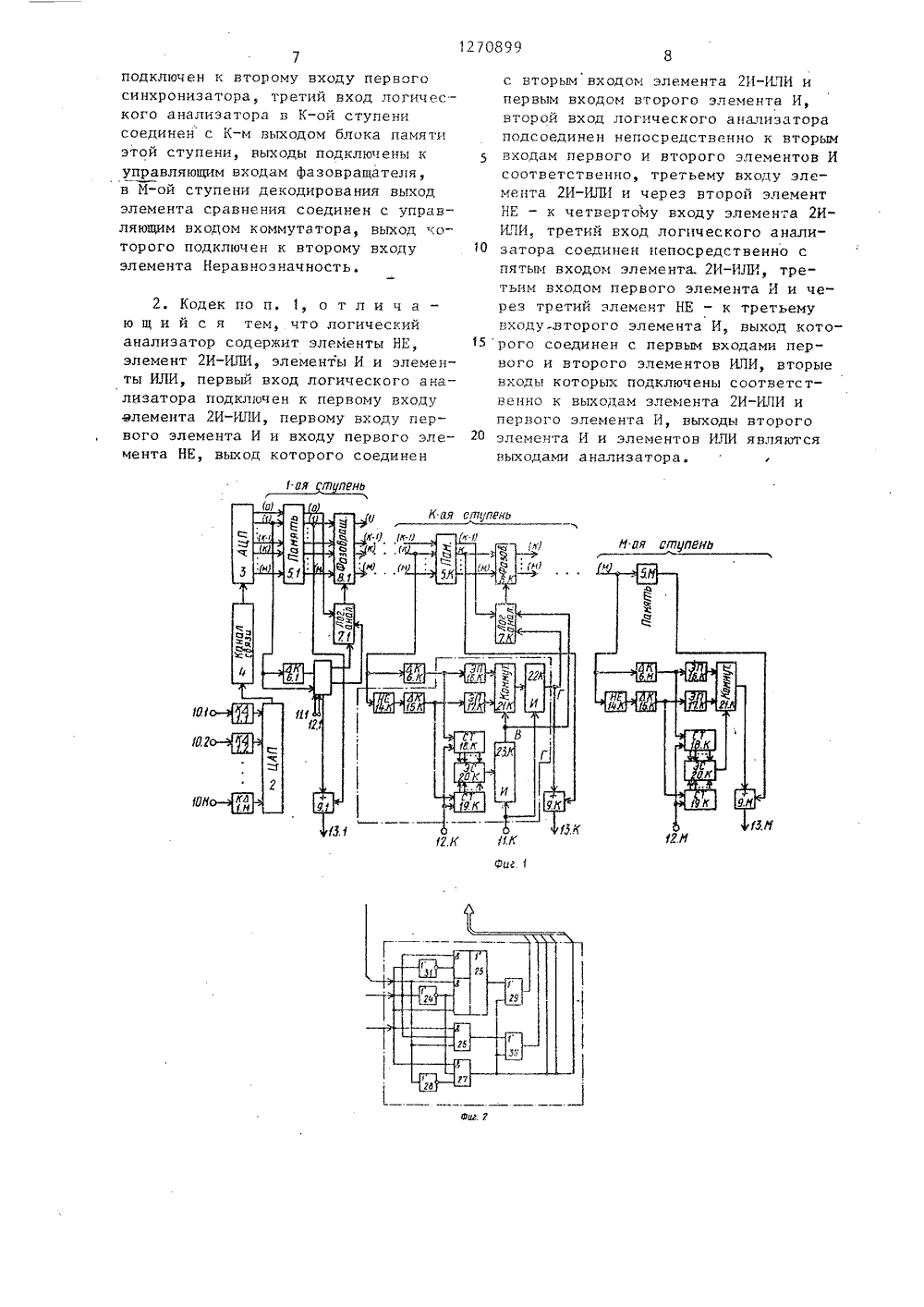

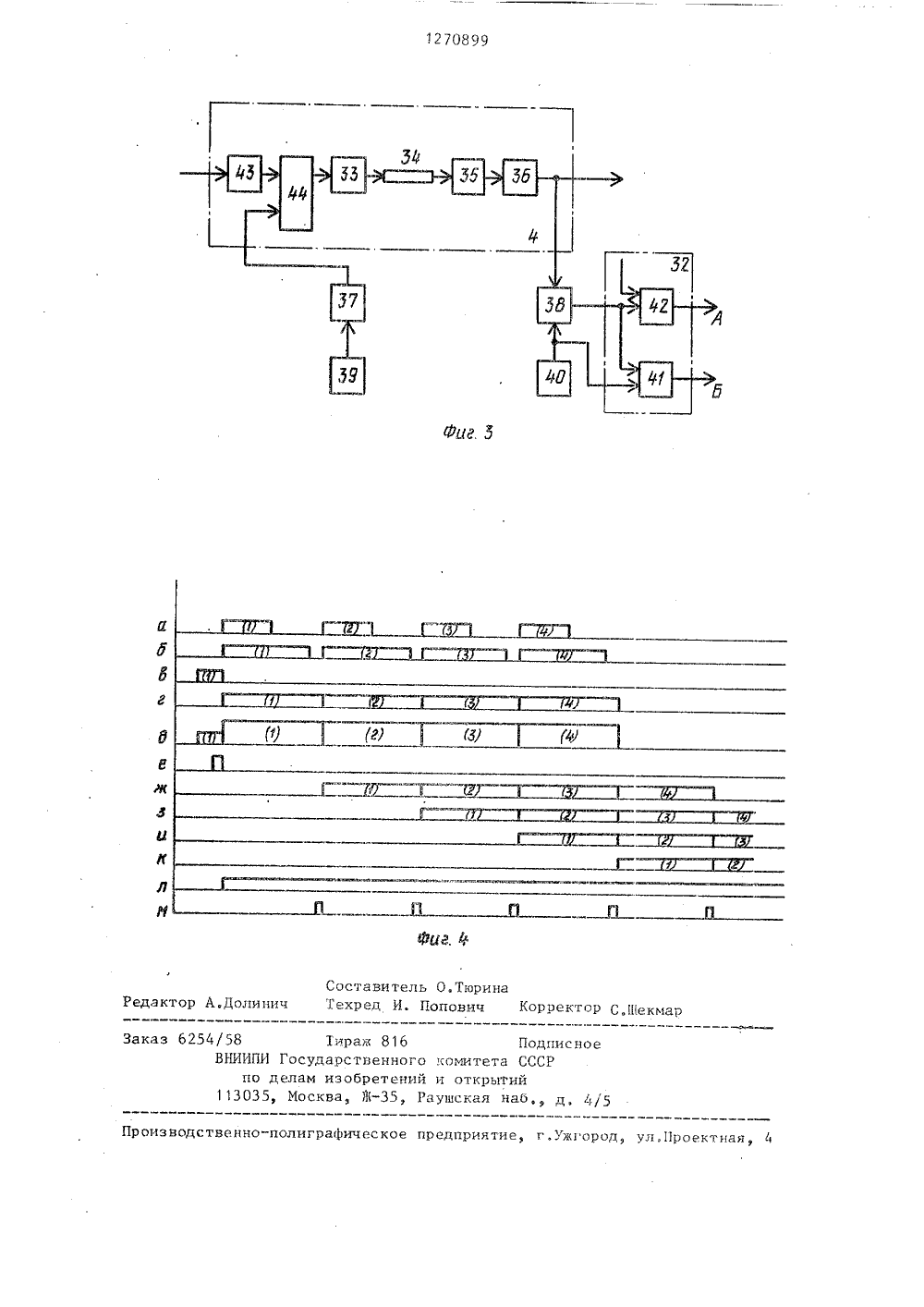

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) ЯОп А НОЗМ 13 001В О НИЕ ИЗОБРЕТЕН ПЬС 7 42С.Данили справление опи при мажоритарПроблемы пере, т. 2, Ф 3,егральным микод ред. Б,В.Та -1980, с. 146. Рончиков Е Теских кодов. М.:рис. 4,1,гия В.Д.,е икл оп 1 пйохпах 1 оп1 Т, Р 3,(54) КОДЕК БЛ (57) Изобрете лительной тех лемеханике, к и декодирова НЫХ КО О вычис ние относится ике, автомати устройствам к те -ованияможет я информаци ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Штарьков Ю.М.бок кратности сдном декодировании,дачи информации, 19с. Зо 47Справочник по инросхемам. Изд. 2-ерабрина, М.: ЭнерКолесник Ми Декодировани цСвязь, 1968, с, 1с, 118, рис. 4.2,1 ЕЕЕ Тхапзасс 1 оТ 1 еоху, 1977, Маур. 371-377. быть использовано в цифровых система обработки и передачи дискретной ин - формации. Изобретение позволяет повы сить достоверность декодирования за счет устранения начальной неоднозначности и скачков фазы произвольного порядка. Кодек блочных кодов содержит М в кодер, цифро в аналоговый преобразователь, канал связи, аналого-цифровой преобразователь и М ступеней декодирования. Каждая К-ая ступень декодирования, где К1-М, содержит блок памяти объемом и ) (М + 2 - К) бит, где п - длина кодового слова, фазовращатель, выполненный в виде сумматора по модулю 2 " , элемент НЕ, первый и второй декодеры, элемент неравнозначность, два элемента памяти,два счетчика, элемент сравнения и коммутатор. Каждая ступень, кроме М-ой, содержит логический анализатор и два элемента И. Логический анализатор состоит из трех элементов НЕ, эле - мента 2 И-ИЛИ, двух элементов И и двух элементов ИЛИ. 1 з.пф-лы, 4 ил.Изобретение относится к вычислительной технике, автоматике и тепе- механике, к устройствам кодирования и декодирования информации и может быть использовано в цифровых системах обработки и.передачи дискретной информации.Целью изобретения является повыдостоверности декодирования за счет устранения начальной неоднозначности и скачков фазы произвольного порядка.На фиг. 1 изображена функциональная схема устройства; на фиг. 2схема логического анализатора; нафиг. 3 - схема канала связи, включающего систему цикловой синхронизации,на фиг. 4 - временные диаграммы работы устройства.Кодек блочных кодов содержит М кодеров 11-1.М, цифроаналоговый преобразователь 2 (ЦАП), аналого-цифровойпреобразователь 3 (АЦП), канал 4 связи. Каждая ступень декодирования содержит блок 5 памяти, объемом и (М ++ 2 - К) бит (где п - длина кодовогослова, К - номер ступени 1 - М), первый декодер 6, выполненный в виде декодера фазируемых кодов, логическийанализатор 7 (кроме М-й ступени),фазовращатель 8, выполненный в виде+-ксумматора по модулю 2, элемент9 неравнозначность, входы 10,1 - 10,Мявляются входами устройства, вход11 является первым управляющим входом устройства, вход 12 - вторымуправляющим входом устройства, выходы 13.1-13.М - входом устройстваэлемент 14 НЕ, второй декодер 15идентичный первому декодеру 6, дваэлемента 16 и 1 памяти, два счетчи -ка 18 и 19 импульсов, элемент 20сравнения и коммутатор 21, Каждаяступень декодирования, кроме М-й,содержит также два синхронизатора 22и 23,Логический анализатор 7 (фиг. 2) представляет собой комбинационную логическую схему и содержит первый элемент 24 НЕ, элемент 25 2 И-ИЛИ элементы 26 и 27 И, второй элемент 28 НЕ, два. элемента 29 и 30 ИЛИ, третий элемент 31 НЕ.Канал 4 связи, включающий систему цикловой синхронизации, изображен на фиг, 3, Синхронизация осуществляется с помощью коротких цикловых меток, размещенных во времени между,группами кодовых слов в информационном сигнале, поступающем на входканала 4 связи.Канал 4 связи состоит из элемента 32 управления, фазового модулятора 33, линии 34 связи, фазового демодулятора 35, второго усилителя 36,генератора 37 цикловых меток, приемника 38 цикловых меток, двух генера торов 39 и 40 тактовых импульсов,делителя 41 ча.стоты, триггера 42,первого усилителя 43, аналоговогосумматора 44Триггер 42 и делитель 41 частоты 15 входят в состав элемента 32 управления. Аналоговый сумматор 44 включенв состав канала 4 связи для введенияв информационный сигнал цикловых меток, для чего один из его входов 2 О соединен с выходом генератора 37 цикловых меток. Первый усилитель 43 имеет коэффициент усиления 2 Г/2 длятого, чтобы сигнал на входе фазового модулятора 33 менялся в пределах 25 от 0 до 2. На выходе фазового модулятора 33 в этом случае получаетсясигнал, необходимый для передачи полинии 34 связи. На выходе фазового3демодулятора 35 получается сигнал, ЗО меняющийся от О до 2 Г. Второй усилитель 36 имеет коэффициент усиленияИ.12 /(2 н) и необходим для того, чтобы сигнал на его выходе менялся виф 1пределах от 0 до 235Работа кодека блочных кодов поясняется временными диаграммами сигналов в характерных точках схемы (фиг, 4), где указаны следующие сиг О налы:а) на входе 1 - го кодера 11", б) на входе М-го кодера 1.М;в) на выходе генератора 37 цикловых меток;г) на выходе К-го кодера 1.К,К = 1,М;д) на выход аналогового сумматора 44;е) на вьгход приемника 38 цикло 5 Овых меток,ж) на выходах декодеров 1-й ступени;з) на выхэдах 1-й ступени,и) на выходах декодеров 2-й сту 55 пени,к) на выходах 2-й ступени,л) на втором выходе элемента 32управления,;899 1270 О равна 3м) на первом выходе элемента 32управления,Кодек блочных кодов работает следующим образом.Информационные сигналы поступаютна входы 10. 1 10,М кодеров 1. 1,1.М блочных кодов (и, К , Й ),1.М,где п - длина кода, К; - число информационных символов, с 1 - минимальное хеммингово расстояние 1-го 10кода. Коды выбраны фазируемыми идвоичными. Сигналы с выходов кодеров1.1-1 М поступают на соответствующиевходы ЦАП 2, на выходе которого обМразуется 2 -ичный сигнал, отвечающий 15номеру передаваемого сигнала на единичной окружности,При этом удельная скорость передаваемого сигнала в битах на символ к=-) к;иАмплитуда сигнала с выхода ЦАП 2 нормируется при помощи первого усилите 25 ля 43 канала 4 связи, чтобы соответствовать значению фазы передаваемого сигнала Г 1 в кратн фазовой манипуляции.мПосле передачи группы 2 -ичных кодовых слов в канал 4 связи (фиг.З) при помощи генератора 37 цикловых меток передается короткая метка для цикловой синхронизации, которая объединяется с информационным сигналом в общий сигнал в аналоговом сум маторе 44.Тм самым передаваемое в канал 4 кодовое слово имеет вид матрицы А,Ы 1(,= 1,М, 1 = 1,и. Каждая строка матрицы А, соответствует сло ву кода (1-я строка соответствует 1-му коду); каждый столбец матрицы А соответствует в двоичном виде номеру передаваемой фазы на 1-ом тактовом интервале. 45С выхода демодулятора 35 на входе второго усилителя 36 получается значение принимаемой фазы, отличающееся от передаваемого за счет шумов линии 34 связи и начальной неоднозначности 5 О фазы. На выходе усилителя 36 формируется сигнал в диапазоне от 0 до м+2, который поступает на вход АЦП 3.Сигнал на выходах АЦП 3 соответствует матрице В, =; ) ,= О,М, 55Г,и. Каждая строка матрицы В. от первой до М-й соответствует при-. нятому слову -го кода (и, 1, Й,),а каждый столбец, за исключением символа Ьо, соответствует "жесткому" значению номера принятой фазы. Символ 50; указывает к какому из двух соседних возможных значений фазы ближе принятый сигнал. Кроме того, за счет начальной неоднозначности фазы 2 -го порядка каждый столбец ,/ (без Ро ) может быть повернут на постоянный угол Т 21/2 ( Т = = О, 1, 2, 3, ,) .Процесс декодирования состоит из М шагов, осуществляемых в М последо,вательных ступенях декодирования (фиг."1), при этом на К-м шаге (К1,М) производится три операции:декодирование К-м кодом (и, К, 1,);обнаружение скачка фазы;коррекция всего сигнала по результатам декодирования и обнаружения скачка. Если на первом шаге декодирования (К=1) значение У четно, то дляпервого кода скачка фазы не происходит. Если же 7 нечетно, то для первого кода происходит как бы "обратная работа", т.е, кодовое слово меняется на инверсное. В предлагаемом кодеке декодируется и само слово (и, К 1, Й, ), кода и его инверсная в идентичных декодерах 6 и 15. Затем векторы ошибок запоминаются в элементах 16 и 17 памяти и одновременно поступают на счетчики 18 и 19, которые за и тактов вырабатывают в двоичной форме число, соответствующее числу ошибокДалее с помощью элемента 20 сравнения вьщеляется вектор ошибок, имеющий минимальное число ошибок, который прибавляется к принятому слову кода (и, К Й) для нахождения переданного слова. Если минимальным оказывается вектор ошибок с первого декодера 6, то в канале 4 связи не было скачка фазы. В противном случае минимальным будет вектор ошибок со второго декодера 15, и скачок фазы обнаруживается, Независимо от наличия или отсутствия скачка фазы принятого сигнала в слове первого кода исправляется с 1 = (й- 2) /2 ошибок, После выбора минимального вектора ошибок по команде элемента 20 сравнения через коммутатор 21 пропускается именно этот вектор1270899.При помощи первого логическогопр анализатора 7,1 производится анализ ра получаемых сигналов и вырабатывается со решение,на какой угол следует павер- ля нуть весь сигнал порезультатам де вь кодирования и обнаружения скачка. тПри коррекции на первом шаге де- вх кодирования решаются две задачи, Во- вь первых, компенсируется замеченная вь первым кодом ошибка, при этом сигнал 1 О М- переводится в ближайший по значению вх о, Во-вторых, компенсируется ска- вы чак фазы так, чтобы для сзедующегост (второго) кода получалось либо пра- со вильное слово, либо его инверсия. 15 по Для этого значение Т надо искусст- о венно сделать четным. Значение тре- с буемого поворота фазы вырабатывает- ди ся в цифровой форме логическим анали- но затором 7. 1, а сам поворот осуществ пр ляется фазовращателем 8, на первыевь входы которого поступает столбец , 2 (без 1 о, ), а на вторые - значение ва коррекции, коДекодирование в следующих ступе па нях (2КМ) осуществляется анало-со гично. При последнем декодировании ст (К=М) отсутствует необходимость кор- вв рекции, поэтому в последней ступени си отсутствует анализатор 7 и фазовра- ЗО ко щатель 8.э Формула изобретения Кодек блочных кодов, содержа 35 щий М кодеров, где М-кратность фазовой манипуляции сигналов, входы которых являются входами устройства, выходы подключены к соответствующим входам цифроаналогового преобразава 40 теля, выход которого через канал связи соединен с входом аналого-цифрового преобразователя и М ступеней декодирования, каждая из которьп, кроме М-й ступени декодирования,45 содержит фазовращатель, каждая ступень декодирования содержит блок памяти объемоми (М + 2 - К) бит, где и-длина кодового слова, К-номер ступени декодирования, К = 1 - М первый декодер и элемент неравнозначность, (К)-й выход блока памяти соединен с первым входом элемента неравнозначность, выход которого является выходом К-й ступени декодирования устройства, вход первого декодера первой ступени соединен с первым выходом аналого"цифровога еабразователя, вход первого декаде"каждой ступени с второй по М-юединен с К-м выходом фазовращатепредыдущей ступени декодирования, иоды аналого-цифрового преабразоваеля подключены к,соответствующимодам блока памяти первой ступени, ходы блока памяти, кроме (К)-го хода, каждой К-ой ступени, кромеой, подключены к соответствующимодам фазовращателя той же ступени,ходы фазовращателя предыдущейупени декодирования подключены кответствующим входам блока памятиследующей ступени декодирования,т л и ч а ю щ и й с я тем, что,целью повышения достоверности декарования за счет устранения начальй неоднозначности и скачков фазыоизвольного порядка, фазовращательпталнен в виде сумматора па модулю м+-кв каждую ступень декадирания введены элемент НЕ, второй дедер, первый и второй элементымяти, коммутатор, счетчики импульв и элемент сравнения, в каждуюупень декодирования, кроме М-ой,едены логический анализатор инхронизаторы, в каждой ступени дедирования первые н вторые входы лемента сравнения годключены соответственно к соответствующим выходам первого и второго счетчиков импульсов, первые входы первого и второго счетчиков импульсов объединены и являются первым управляющим входом каждой ступени декодирования, вторые входы первого и второго счетчиков импульсов объединены соответственно с входами первого и второго элементов памяти и подключены к выходам первого и второго декодеров, выходы первого и второго элементов памяти подключены соответственно к первому и второму входам коммутаторов, К-й выхац фазавращателя предыдущей ступени соединен через элемент НЕ с входом второго декодера последу ющей ступени декодирования, первые входы синхронизаторов объединены и являются вторым управляющим входом ступени декодирования, выход первого синхронизатора соединен с вторым входом элемента Неравнозначность и первым входом логического анализатора, второй вход которого объединен с управляющим входом коммутатора и подключен к выходу второго синхронизатора, выход коммутатораподключен к второму входу первогосинхронизатора, третий вход логического анализатора в К-ой ступенисоединен с К-м выходом блока памятиэтой ступени, выходы подключены куправляющим входам фазовращателя,в М-ой ступени декодирования выходэлемента сравнения соединен с управляющим входом коммутатора, выход оторого подключен к второму входуэлемента Неравнозначность,2. Кодек по п. 1, о т л и ч а ю щ и й с я тем, что логический анализатор содержит элементы НЕ, элемент 2 И-ИЛИ, элементы И и элементы ИЛИ, первый вход логического анализатора подключен к первому входу элемента 2 И-ИЛИ, первому входу первого элемента И и входу первого элемента НЕ, выход которого соединен с вторым входом элемента 2 И-ИЛИ ипервым входом второго элемента И,второй вход логического анализатораподсоединен непосредственно к вторымвходам первого и второго элементов Исоответственно, третьему входу элемента 2 И-ИЛИ и через второй элементНЕ - к четвертому входу элемента 2 ИИЛИ, третий вход логического анали затора соединен непосредственно спятым входом элемента 2 И-ИЛИ, третьим входом первого элемента И и через третий элемент НЕ - к третьемувходу-,второго элемента И, выход кото рого соединен с первым входами первого и второго элементов ИЛИ, вторыевходы которых подключены соответственна к выходам элемента 2 И-ИЛИ ипервого элемента И, выходы второгоэлемента И и элементов ИЛИ являютсявыходами анализатора.писноеР Производственно-полиграфическое предприятие, г,ужгород, ул,Проектная, 4 Заказ б 254/58 Тираж 81 б ВНИИПИ Государственного коми по делам изобретений и от 113035, Москва, 3-35, Рауиск

СмотретьЗаявка

3832985, 29.12.1984

ПРЕДПРИЯТИЕ ПЯ А-7306, ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

ГИНЗБУРГ ВИКТОР ВУЛЬФОВИЧ, ДАНИЛИН АЛЕКСАНДР СЕРГЕЕВИЧ, ПОРТНОЙ СЕРГЕЙ ЛЬВОВИЧ

МПК / Метки

МПК: H03M 13/05

Опубликовано: 15.11.1986

Код ссылки

<a href="https://patents.su/6-1270899-kodek-blochnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Кодек блочных кодов</a>

Предыдущий патент: Обнаружитель комбинации двоичных сигналов

Следующий патент: Устройство для преобразования последовательного кода в код

Случайный патент: Экран