Генератор функций уолша

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

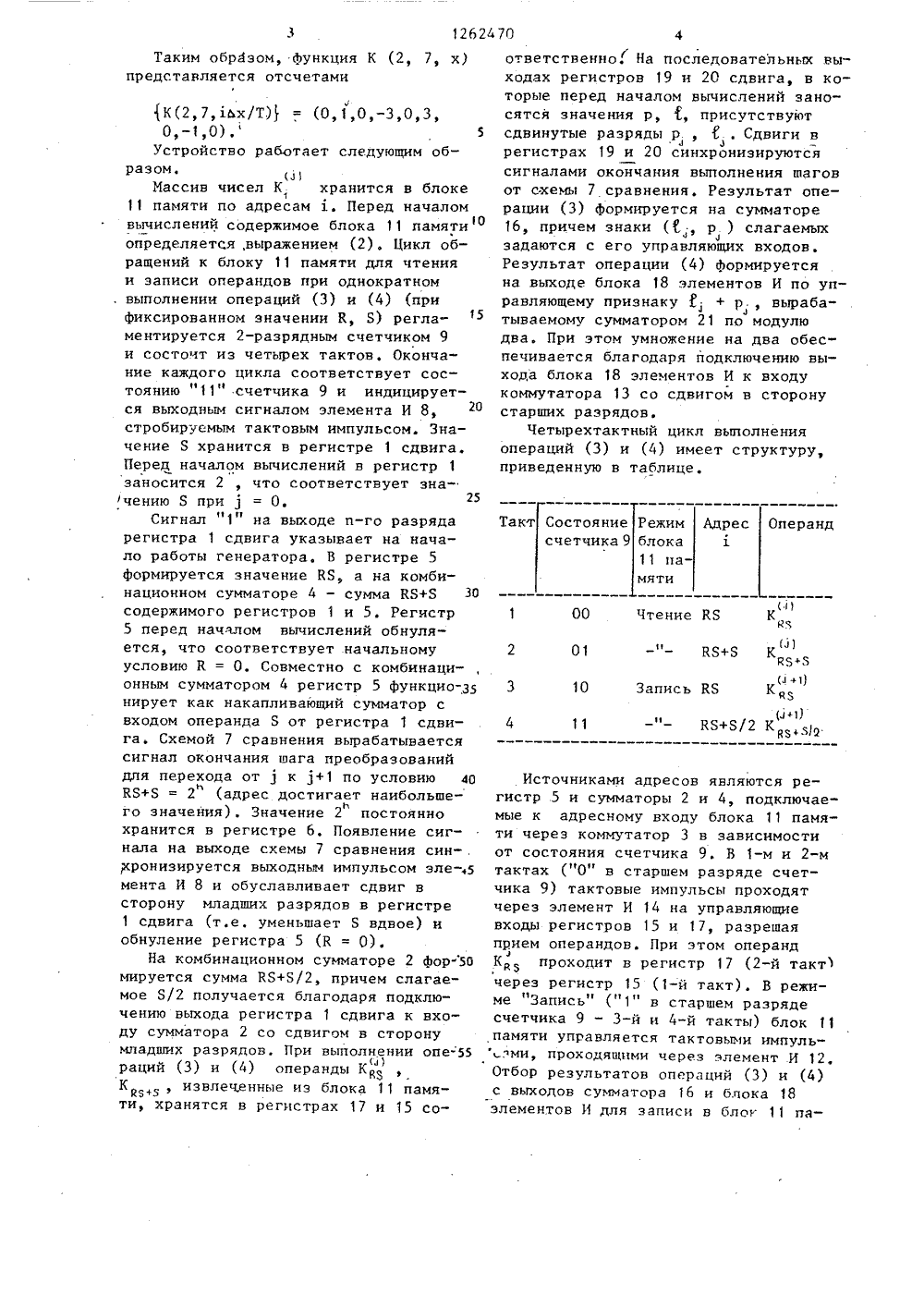

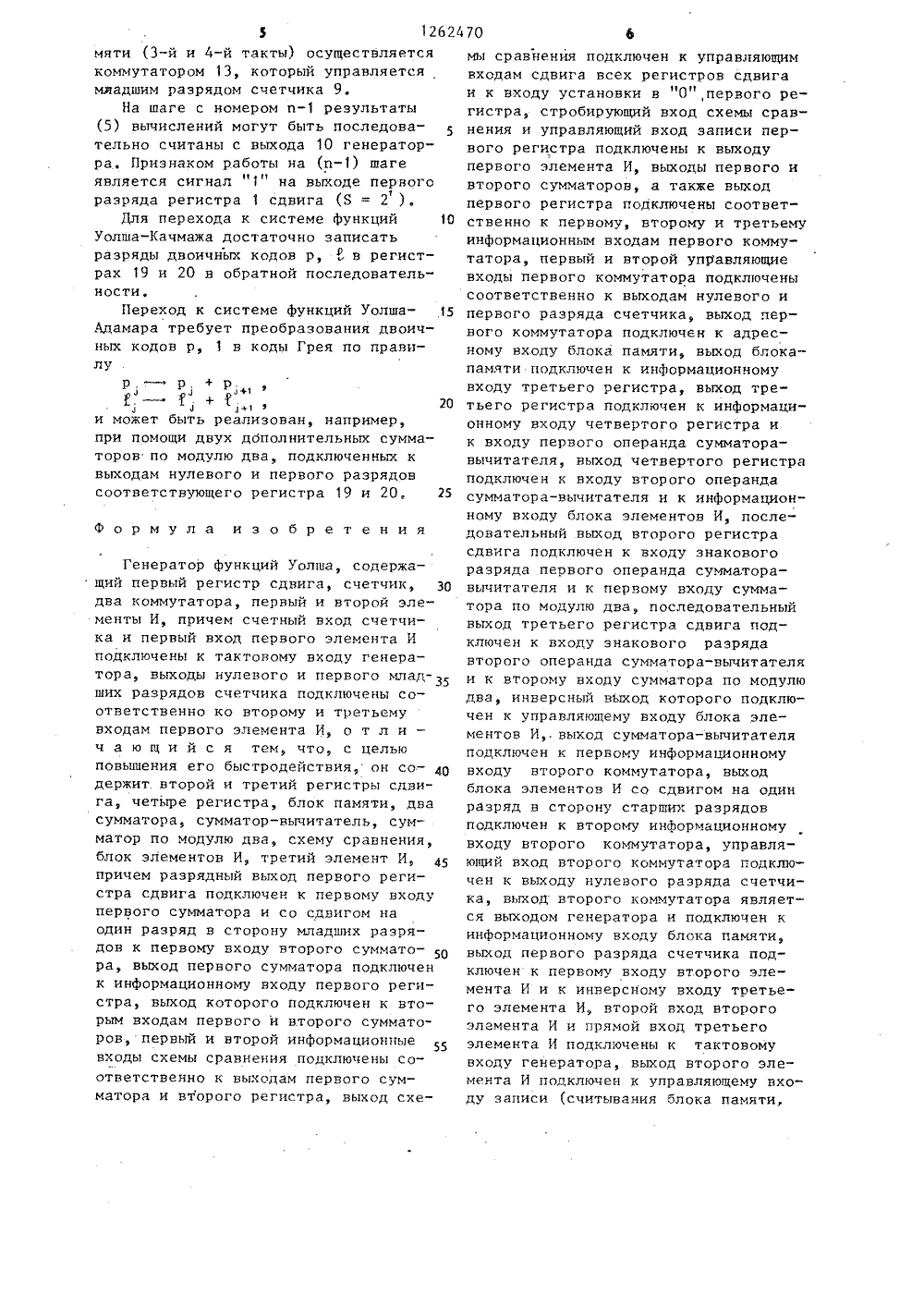

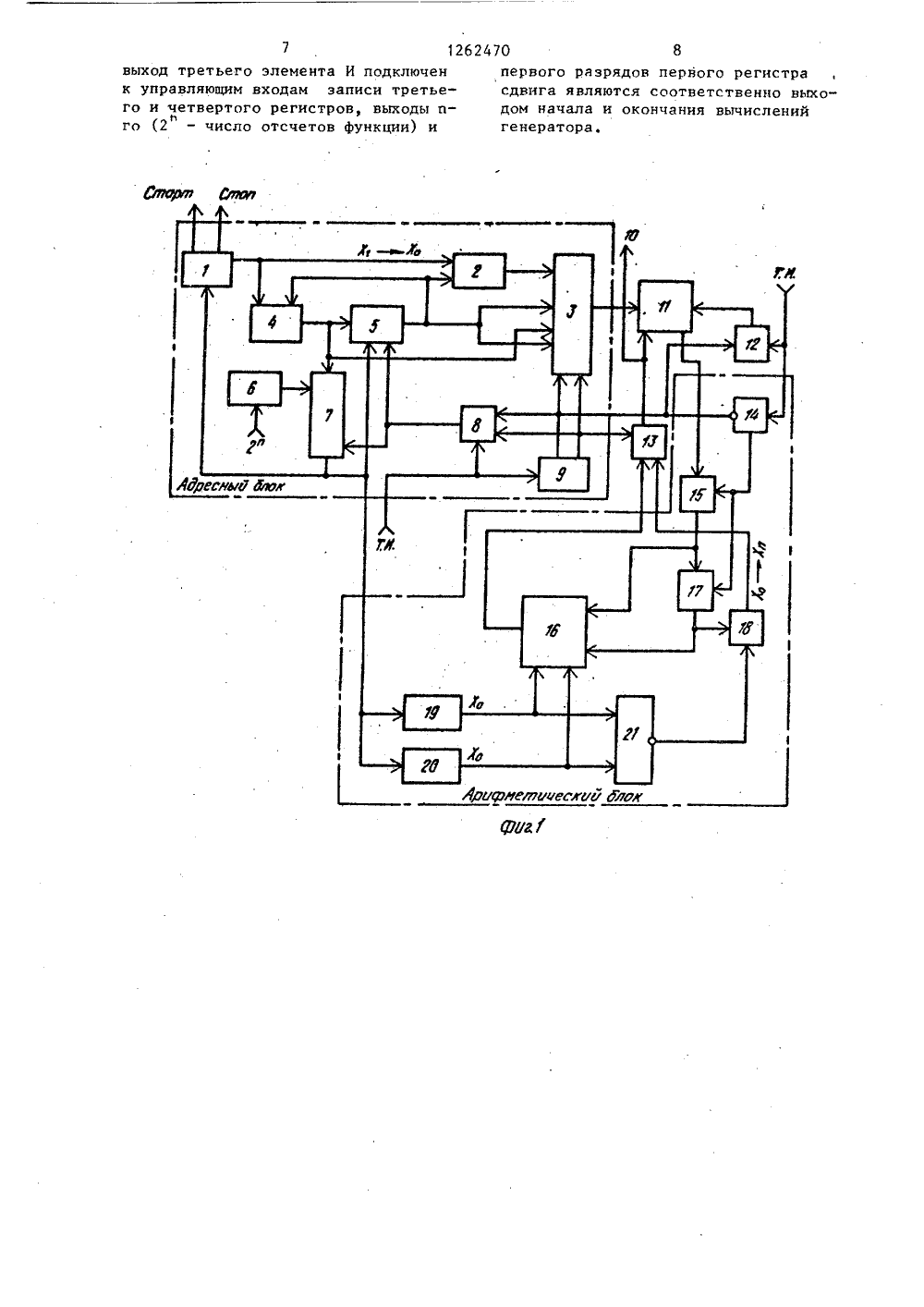

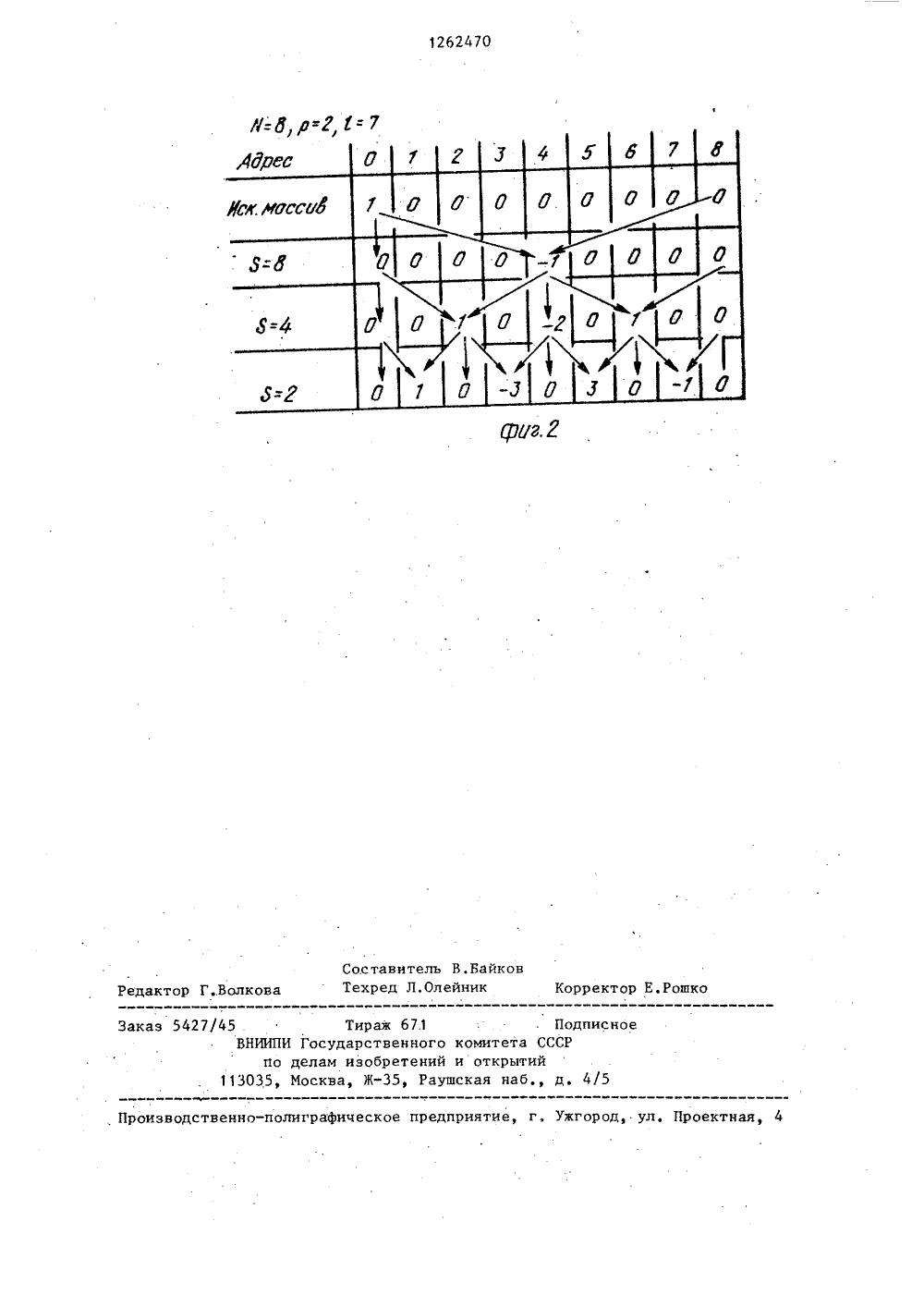

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 126 6 Р 102 ИЭОБРЕТ ТЕЛЬС В 37еской ибернетики Х.Садыхов,олотой оро СССР1979.СССР1983; ельс 1/02 льств Г 1/О ИИ УО бситсяельной области техник аппрок ова ГОСУДАРСТВЕННЫЙ НОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОПИСАНИЕ К АВТОРСКОМУ СВ(71) Институт техниАН БССР(57) Изобретение отавтоматики и вычислии может быть исполь мирующих устройствах кусочно-линейного типа, для спектрального анализаслучайных процессов,в устройствахсжатия информации. Цель изобретения -повышение быстродействия генератора.В состав блока генератора входят трирегистра сдвига, четыре регистра,блок памяти, два сумматора, сумматвычитатель, сумматор по модулю два,два коммутатора, схема сравнения,блок элементов И, три элемента И.Предлагаемая конструкция позволяетреализовать алгоритм вычислений обощенных интегральных функций Уолша счислом шагов, существенно меньшим,чем в известном генераторе, 2 ил,(о)К о- О.1Преобразования на 1-м шаге описы 5 ваются рекурентными соотношениями 10Опри 1. +р, "1(5) В качестве примера рассмотрим вычисления при И = 8, р = 2, 1 = 7.Для наглядности на фиг.2.показанграф вычислений функции К(2, 7, х), З 0 .стрелками отмечены операнды выражений(3) и (4) на каждом шаге преобразований:1-й шаг= 0): 35 ътаЙ(Й, х + Т) с 4 х,где ыа 1(г, х) - функция Уолша с номером г.В зависимости от упорядочения сис темы функций Уолша возможны различные способы упорядочения обобщенных интегральных функций; по Адамару, по Пэли и по Качмажу. При переходе из одной системы в другую номера р, 1 па ры функций Уолша, используемых в выражении (1), изменяются,В системе Уолша-Пэли значения 2-й шаг Ц = 1); 50:Р2 Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано в аппроксимирующих устройствах кусочно-линейного типа, дляспектрального анализа случайных процессов, в устройствах сжатия информации,Целью изобретения является повышение быстродействия генератора,На фиг,1 представлена функциональная схема генератора функций Уолша,на фиг,2 - граф алгоритма вычисленийфукций К (2, 7, х),Генератор функций Уолша содержитрегистр 1 сдвига, сумматор 2, коммутатор 3, сумматор 4, регистр 5, ре"гистр 6 сдвига, схему 7 сравнения,элемент И 8, двухразрядный счетчик 9,выходную шину 10, блок 11 памяти,элемент И 12, коммутатор 13, элементИ 14, регистр 15, сумматор-вычитатель 16, регистр 17, блок 18 элементов И, регистры 19 и 20 сдвига, сумматор 21 по модулю два, Группа блоков1-9 образует адресную часть схемы генератора, группа блокев 14-21 - арифметическую часть,Система обобщенных интегральных,функций Уолша определяется следующимобразом К(р, Й, г) =ыа 1(р, х).о К(р1 дх/Т) 1 = 01 дискретной обобщенной интегральнойлфункции Уолша К(р, х), где И2число отсчетов за период Т, могутбыть получены в результате и шаговпреобразования массива чисел(, Р(,)К =(-1) К +(-1) К 1ез зН а 3аз 5(3) р . - значения 1-го разряда в двоичных л - разрядных кодах 6, р (нумерация со стороны младших разрядов),После выполнения шага с номером иполучаем(Массив чисел К хранится в блоке 1 памяти по адресам . Перед началом вычислений содержимое блока 11 памяти определяется, выражением (2), Цикл обращений к блоку 11 памяти для чтения и записи операндов при однократном . выполнении операций (3) и (4) (при фиксированном значении К, Б) регламентируется 2-разрядным счетчиком 9 и состочт из четырех тактов, Окончание каждого цикла соответствует состоянию "11" счетчика 9 и индицируется выходным сигналом элемента И 8, стробируемым тактовым импульсом. Значение Б хранится в регистре 1 сдвига. Перед началом вычислений в регистр 1 заносится 2 , что соответствует зна 1 чению Б при 3 = О.Сигнал и 1 и на выходе п-го разряда регистра 1 сдвига указывает на начало работы генератора, В регистре 5 формируется значение КЯ, а на комбинационном сумматоре 4 - сумма КБ+Б З 0 содержимого регистров 1 и 5. Регистр 5 перед началом вычислений обнуляется, что соответствует начальному условию К = О. Совместно с комбинационным сумматором 4 регистр 5 функцио-З 5 нирует как накапливающий сумматор с входом операнда Б от регистра 1 сдвига. Схемой 7 сравнения вырабатывается сигнал окончания шага преобразований для перехода от 3 к 3+ по условию 40 КЯ+Б = 2 (адрес достигает наибольшего значения), Значение 2 постоянно хранится в регистре б. Появление сигнала на выходе схемы 7 сравнения син- . хронизируется выходным импульсом эле-,5 мента И 8 и обуславливает сдвиг в сторону младших разрядов в регистре1 сдвига (т,е. уменьшает Б вдвое) иобнуление регистра 5 (К = О).На комбинационном сумматоре 2 формируется сумма КБ+Б/2, причем слагаемое Б/2 получается благодаря подключению выхода регистра 1 сдвига к входу сумматора 2 со сдвигом в сторону младших разрядов. При выполнении операций (3) и (4) операнды КК, , извлеченные из блока 11 памятй, хранятся в регистрах 17 и 15 со Адрес Операнд Такт Состояние Режим счетчика 9 блока 11 па яти(,11 )КБ+Б/2 К Запись 10 Источниками адресов являются регистр .5 и сумматоры 2 и 4, подключаемые к адресному входу блока 11 памяти через коммутатор 3 в зависимости от состояния счетчика 9. В 1-м и 2-м тактах ("0" в старшем разряде счетчика 9) тактовые импульсы проходят через элемент И 14 на управляющие входы регистров 15 и 17, разрешая прием операндов. При этом операндЭКдз проходит в регистр 17 (2-й такт через регистр 15 (1-и тахт). В режиме "Запись" ("1" в старшем разряде счетчика 9 - 3-й и 4-й такты) блок 11 памяти управляется тактовыми импульэми, проходящими через элемент И 12, Отбор результатов операций (3) и (4) с выходов сумматора 16 и блока 18 элементов И для записи в бла 1 11 паответственно На последовательных выходах регистров 19 и 20 сдвига, в которые перед началом вычислений заносятся значения р, 1, присутствуют сдвинутые разряды р., 1 , Сдвиги в регистрах 19 и 20 синхронизируются сигналами окончания выполнения шагов от схемы 7 сравнения, Результат операции (3) формируется на сумматоре 16, причем знаки (, р ) слагаемых,1 Ьзадаются с его управляющих входов. Результат операции (4) формируется на выходе блока 18 элементов И по управляющему признаку+ р., вырабатываемому сумматором 21 по модулю два. При этом умножение на два обеспечивается благодаря подключению выхода блока 18 элементов И к входу коммутатора 13 со сдвигом в сторону старших разрядов.Четырехтактный цикл выполнения операций (3) и (4) имеет структуру, приведенную в таблице.12624 20 формулаизобретения Генератор функций Уолша, содержащий первый регистр сдвига, счетчик, два коммутатора, первый и второй элементы И, причем счетный вход счетчика и первый вход первого элемента И подключены к тактовому входу генератора, выходы нулевого и первого млад-З ших разрядов счетчика подключены соответственно ко второму и третьему входам первого элемента И, о т л и - ч а ю щ и й с я тем, что, с целью повышения его быстродействия, он со- о держит второй и третий регистры сдвига, четыре регистра, блок памяти, два сумматора, сумматор-вычитатель, сумматор по модулю два, схему сравнения, блок элементов И, третий элемент И, причем разрядный выход первого регистра сдвига подключен к первому входу первого сумматора и со сдвигом на один разряд в сторону младших разрядов к первому входу второго сумматора, выход первого сумматора подключен к информационному входу первого регистра, выход которого подключен к вторым входам первого и второго сумматоровпервый и второй информационные входы схемы сравнения подключены соответственно к выходам первого сумматора и второго регистра, выход схе 3мяти (3-й и 4-й такты) осуществляетсякоммутатором 13, который управляетсямладшим разрядом счетчика 9.На шаге с номером презультаты(5) вычислений могут быть последовательно считаны с выхода 10 генераторра, Признаком работы на (и) шагеявляется сигнал "1" на выходе первого1разряда регистра 1 сдвига (Б = 2 ),Для перехода к системе функций 1 ОУолша-Качмажа достаточно записатьразряды двоичных кодов р, ф в регистрах 19 и 20 в обратной последовательности,Переход к системе функций УолшаАдамара требует преобразования двоичных кодов р, 1 в коды Грея по правилуР. Р + Р+,1 - 1+ 1и может быть реализован, например,при помощи двух дополнительных сумматоров по модулю два, подключенных квыходам нулевого и первого разрядовсоответствующего регистра 19 и 20, 25 мы сравнения подключен к управляющимвходам сдвига всех регистров сдвигаи к входу установки в 0",первого регистра, стробирующий вход схемы сравнения и управляющий вход записи первого регистра подключены к выходупервого элемента И, выходы первого ивторого сумматоров, а также выходпервого регистра подключены соответственно к первому, второму и третьемуинформационным входам первого коммутатора, первый и второй упРавляющиевходы первого коммутатора подключенысоответственно к выходам нулевого ипервого разряда счетчика, выход первого коммутатора подключен к адресному входу блока памяти, выход блокапамяти подключен к информационномувходу третьего регистра, выход третьего регистра подключен к информационному входу четвертого регистра ик входу первого операнда сумматоравычитателя, выход четвертого регистраподключен к входу второго операндасумматора-вычитателя и к информационному входу блока элементов И, последовательный выход второго регистрасдвига подключен к входу знаковогоразряда первого операнда сумматоравычитателя и к первому входу сумматора по модулю два, последовательныйвыход третьего регистра сдвига подключен к входу знакового разрядавторого операнда сумматора-вычитателяи к второму входу сумматора по модулюдва, инверсный выход которого подключен к управляющему входу блока элементов И,. выход сумматора-вычитателяподключен к первому информационномувходу второго коммутатора, выходблока элементов И со сдвигом на одинразряд в сторону старших разрядовподключен к второму информационномувходу второго коммутатора, управляющий вход второго коммутатора подключен к выходу нулевого разряда счетчика, выход второго коммутатора является выходом генератора и подключен кинформационному входу блока памяти,выход первого разряда счетчика подключен к первому входу второго элемента И и к инверсному входу третьего элемента И, второй вход второгоэлемента И и прямой вход третьегоэлемента И подключены к тактовомувходу генератора, выход второго элемента И подключен к управляющему входу записи (считывания блока памяти, 1262470выход третьего элемента И подключен к управляющим входам записи третьего и четвертого регистров выходы и 1го (2 - число отсчетов функции) и первого разрядов первого регистрасдвига являются соответственно выходом начала и окончания вычисленийгенератора..Рошк 45 . Тираж 67.1 . , Подп ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4

СмотретьЗаявка

3868933, 19.03.1985

ИНСТИТУТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ АН БССР

ЧЕГОЛИН ПЕТР МИХАЙЛОВИЧ, САДЫХОВ РАУФ ХОСРОВОВИЧ, ШАРЕНКОВ АЛЕКСЕЙ ВАЛЕНТИНОВИЧ, ЗОЛОТОЙ СЕРГЕЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генератор, уолша, функций

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/6-1262470-generator-funkcijj-uolsha.html" target="_blank" rel="follow" title="База патентов СССР">Генератор функций уолша</a>

Предыдущий патент: Многоканальное пневматическое устройство управления

Следующий патент: Устройство для синхронизации каналов

Случайный патент: Способ изготовления резинотехнических рукавов с ответвлениями