Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

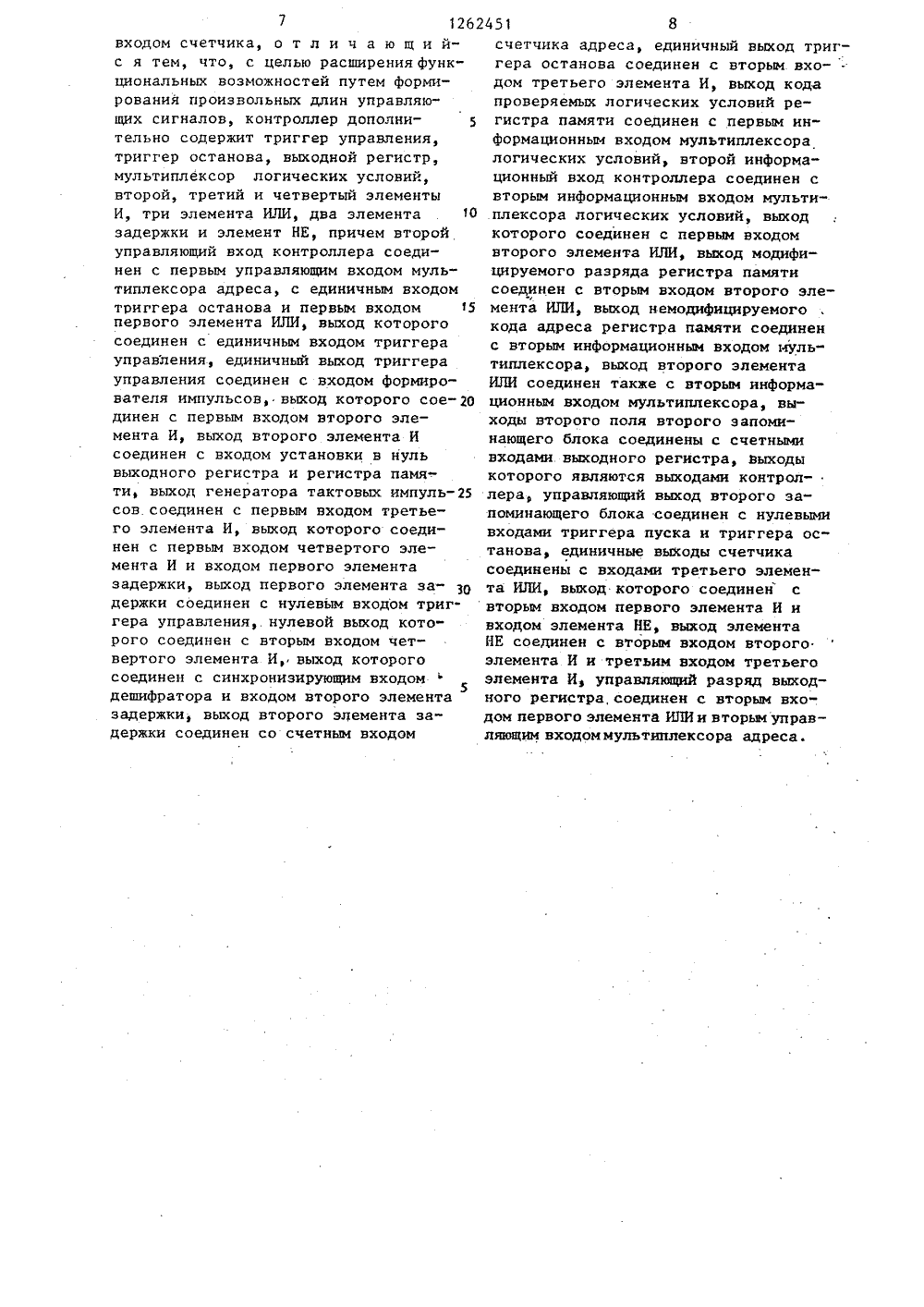

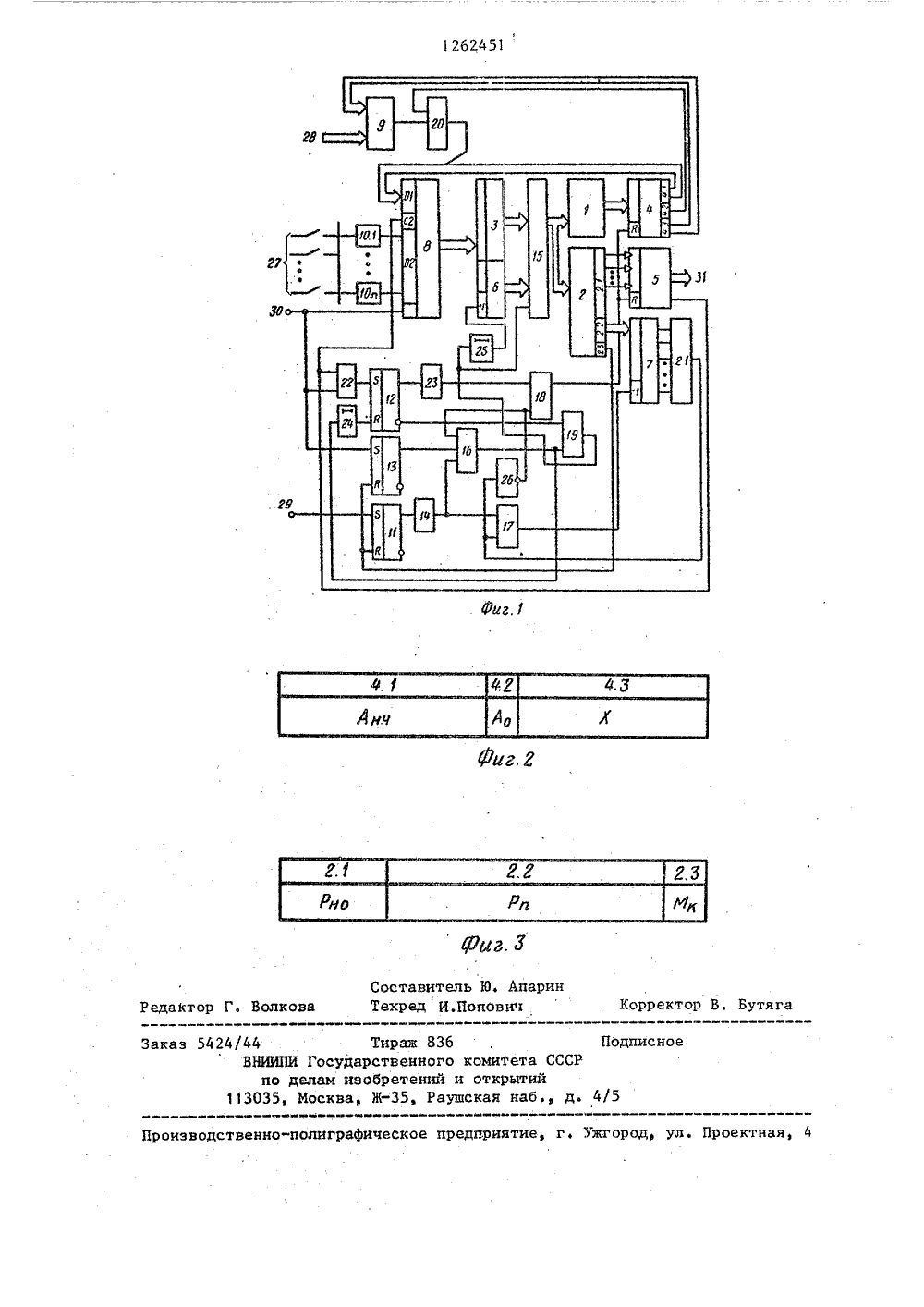

(19 4 С 05 В 19/18 ИЗОБРЕТЕН ИСАНИЕ ЕЛЬ н СССР 976.0753 тельств 19/18,ании РСР1981,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(56) Авторское свиде9 647655, кл. С 05 ВПатент Великобриткл, С 3 И, 1978.Авторское свидетельство9 1001012, кл. С 05 В 19/18 РОГРАММИРУЕМЫИ КОНТ 7 Изобретение относится к автоматике и вычислительнаи технике и может найти применение при построениисистем программной коммутации и дляуправления технологическими процессами. Решается задача расширенияфункциональных возможностей программируемого контроллера путем совмещения процесса выборки информации изпамяти с временем выдачи управляющихсигналов, а также путем формирования сигналов произвольной длительности. С первых информационных входов контроллера через элементы согласования на информационные входы мультиплексора адреса поступает код адреса первой подпрограммы. Одновременно .на управляющий вход мультиплексораадреса поступает сигнал "Начало работы". Импульс с выхода генераторатактовых импульсов, пройдя черезтретий и"четвертый элементы И, поступает на синхронизирующий вход дешифратора адреса и производит выборку информации из первого и второго запоминающих блоков. Операционная часть команды из второго запоминающего блока поступает в выходной регистр, Одновременна сигнал свыхода четвертого элемента И череэвторой элемент задержки поступает насчетный вход счетчика адреса и увеличивает его содержимое, Код "простояконтроллера поступает на входысчетчика и через третий элемент ИЛИразрешает прохождение импульсов так.тавого генератора на вычитающий входсчетчика через первый элемент И. После выдержки времени "простоя" и обнуления счетчика разрешается прохождение тактовых импульсов через третий элемент И. При поступлении навторой информационный вход контроллера када логического условия на выходе мультиплексора логических условий появляется либо сигнал логического нуля, либо логической единицы.При этом постоянная часть адреса дополняется либо нулем, либо единицей.Метка - признак окончания программыс выхода выходного регистра поступает на второй управляющий вход мультиплексора адреса и записывает сформированный адрес очередной подпрограммы управления в регистр адреса.При поступлении метки-признака концаработы из второго запоминающего блокатриггеры пуска и останова переводятсяв нулевое состояние и запрещает про.хождение тактовых импульсов, 3 ил, 126245120 Изобретение относится к автоматике и вычислительной технике и может найти применение при построении систем программной коммутации и для управления технологическими процес сами.Цель изобретения - расширение функ. циональных возможностей контроллера путем формирования произвольных длин управляющих сигналов. 10Сущность изобретения состоит в хранении в запоминающем блоке признаков начала и конца выдачи импульсов на управление технологическими процессами. Реализация выходного реги стра на основе Т-триггеров позволяет организовать независимую асинхронную выдачу управляющих сигналов в пределах программы функционирования контроллера.На Фиг. 1 представлена Функциональная схема программируемого контроллера; на 4 иг, 2 - формат слова первого запоминающего блока на фиг. 3 - Формат слова второго запоминающего блока.Программируемый контроллер (фиг.1) содержит первый 1 и второй 2 запоминающие блоки, регистр 3 адреса, регистр 4 памяти, выходной регистр 5, 30 счетчик 6 адреса, счетчик 7, мультиплексор 8 адреса, мультиплексор 9 логических условий, элементы 10.1- 10.п согласования, триггер 11 пуска, триггер 12 управления, триггер 13 останова, генератор 14 тактовых импульсов, дешифратор 15 адреса, третий элемент И 16, первый элемент И 17, второй элемент И 18, четвертый элемент И 19, второй элемент ИЛИ 20, третий элемент ИЛИ 21, первый элемент ИЛИ 22, формирователь 23 импульса, первый элемент 24 задержки, второй элемент 25. задержки, элемент НЕ 26.На фиг. 1 обозначены: первые информационные входы 27 контроллера, второй информационный вход (вход логических условий) 28 контроллера, первый 29 и второй 30 управляющие входы контроллера и выход 3 1 контроллера.Формат слова первого запоминающего блока 1 (фиг.2) содержит код немоди"., фицируемой части адреса (А, модифицируемый разряд адреса (А,) икод проверяемых логических условий (Х).формат слова второго запоминающего блока 2 (фиг.3) содержит поле признаков начала и окончания выдачи импульсов (Рц ), поле (код) простоя контроллера (Р ) и метку (М) окончания выполнения программы.Назначение основных Функциональных элементов программируемого контроллера состоит в следующем.Запоминающий блок 1 предназначендля хранения адресной информации,Запоминающий блок 2 предназначендля хранения, во-первых, признаковначала выдачи управляющих сигналовв подпрограмме, во-вторых, признаков окончания выдачи импульсов,в-третьих, кодов длин промежутковвремени, когда не происходит изме-.нения состояний выходов программируемого контроллера, и, в-четвертых,метки окончания выполнения программы.Регистр 4 памяти предназначен дляхранения адреса очередной подпрограммы, адрес которой будет окончательносформулирован в зависимости от логи-ческого условия,.Модификация адреса осуществляетсяс помощью мультиплексора 9 логических условий и элемента ИЛИ 20,Счетчик 6 адреса осуществляет последовательную выборку адресов подпрограммы. Счетчик 7 предназначендля хранения кода промежутка времени,на которое запрещено изменение состояния выходов 31 контроллера.Элементы 10.1-10.п согласования,например оптроны, обеспечивают развязку входных цепей контроллера ипреобразование сигналов с параметрами входных цепей в сигналы с параметрами элементной базы контроллера.Триггер 11 пуска, триггер 12 управления, триггер 13 останова, генератор 14 тактовых импульсов, элементы И 16-19, Формирователь 23 импуль"са и элементы 24 и 25 задержки организуют работу программируемого контроллера.Программируемый контроллер работает следующим образом.,В исходном состоянии элементы памяти контроллера находятся в нулевомсостоянии Начало работы контроллера осуществляется подачей с управляющего входа 29 импульсов на единичный вход триггера 11 пуска. Этим осуществляется подготовительный этап функционирования контроллера.С первых информационных входов (входных цепей) 27 контроллера через элементы 10.1-10 л согласования на информационные входы мультиплексора 8 адреса поступает код, определяющий 5 адрес первой подпрограммы. Одновременно с этим с входа 30 на управляющий вход мультиплексора 8 поступает сигнал "Начало работы". По этому сигналу код адреса подпрограммы че рез мультиплексор 8 адреса поступает в регистр 3 адреса, определяя номер подпрограммы, Кроме того, сигнал с входа 30 поступает через элемент ИЛИ 22 на единичный вход триггера 12 уп-. 15 равления, а также на единичный вход триггера 13 останова. После этого все триггеры находятся в единичном состоянии. По перепаду потенциала на единичном выходе триггера 12 уп равления на выходе формирователя 23 импульса появляется импульс, который производит установку в нуль регистра 4 памяти и выходного регистра 5 (счет чик 7 находится в нулевом состоянии 25 и на выходе элемента ИЛИ 21 имеется сигнал логического нуля, который через элемент НЕ 26 разрешает обнуление регистра 4 памяти и выходного регистра 5)30 Триггер 13 останова находится в единичном состоянии и разрешает прохождение импульсов с выхода генератора 14 через элемент И 16. Первый тактовый импульс с выхода элемента И 16 через элемент 24 задержки производит обнуление триггера 12 управления. Второй импульс с выхода генератора 14 через элементы И 16 и 19 по ступает на синхронизирующий вход дешифратора 15 и производит выборку информации из первого 1 и второго 2 запоминающих блоков.Из запоминающего блока 1 в регистр 4 памяти будет считан адрес очередной подпрограммы управления. Подпрограмма управления представляет собой линейную последовательность команд программы управления. Операционная часть команды из запоминающего блока 2 поступает в выходной регистр 5 на счетные входы Т-триггеров, устанавливая соответствующие из них в единичное состояние, Одновременно с выборкой информации из первого 1 ,и второго 2 запоминающих блоков сигнал с выхода элемента И 19 через элемент 25 задержки поступает на счет ный вход. счетчика 6 адреса и увеличивает его содержимое на единицу.Очередной тактовый импульс разрешает выборку из запоминающего блока 2 второй команды управления, содержащей только операционную часть. Выбранная команда, поступая на счетные входы триггеров выходного регистра 5, переводит соответствующие из них в противоположное состояние, чем заканчивает выдачу импульсов управления, Состояние других выходов может остаться без изменения. Далее контроллер функционирует аналогичным образом.В том случае, если на некоторое множество тактов нет необходимости изменять состояние выходов контроллера, то в соответствующей команде с выхода поля 2,2 запоминающего блока 2 задается код (Р ) "простоя". Такая организация работы и кбдирования блоков памяти применены для исключения "пустых" команд управления и оптимизации тем самым запоминающих блоков.Код "простоя" контроллера поступает на входы счетчика 7 и через элемент ИЛИ 21 и элемент НЕ 26 запрещает прохождение тактового импульса с выхода генератора 14 через элемент И 16. Сигнал логической единицыс выхода элемента ИЛИ 21 разрешаетпрохождение тактовых импульсов с ге-,нератора 14 через элемент И 17 на вычитающий вход счетчика 7. После выдержки времени "простоя" и обнулениясчетчика 7 на выходе элемента ИЛИ 21будет сигнал логического нуля, Этотсигнал поступает на вход элементаНЕ 26 и разрешает тем самым прохождение тактовых импульсов через элемент И 16. Далее контроллер функционирует аналогично рассмотренномуранееСовместно с признаком последнегоимпульса подпрограммы управленияв запоминающем блоке 2 хранится признак перехода к выполнению очередной подпрограммы. Переход к выполнению очередной подпрограммы (линейной последовательности команд управления) осуществляется в зависимостиот логических условий (условий объекта управления), поступающих на вход28 контроллера. Модификация адресаочередной подпрограммы осуществля 126245ется следующим образом. В поле 4.1регистра 4 памяти хранится код (А)немодифицируемой части адреса - некоторая его постоянная часть, в поле4.2 хранится модифицируемый разряд(или группа разрядов при проверкенескольких логических условий), вполе 4.3 - код проверяемого условия(или условий) в зависимости от выполнения (или невыполнерия) которого возможен переход к той или инойподпрограмме управления, При поступлении на вход 28 контроллера кода логического условия на выходе мультиплексора 9 логических условий будет 15либо сигнал логического нуля (еслипроверяемое уеловие не выполнено),либо сигнал логической единицы (еслиусловие выполнено). При этом постоянная часть адреса дополняется либо 2 Онулем, либо единицей в зависимостиот выполнения логического условия.Метка-признак окончания подпрограммыс выхода регистра 5 поступает на управляющий вход мультиплексора 8 адреса и производит запись сформированного адреса очередной подпрограммыуправления в регистр 3 адреса. Выполнение очередной подпрограммы осуществляется описанным ранее способом. ЗОС выдачей последнего импульса программы управления с выхода поля 23запоминающего блока 2 выдается меткапризнак (М ) конца работы. Эта меткапоступает на нулевые входы триггера11 пуска и триггера 13 останова, ко"торые после перехода к нулевое состояние запрещают выдачу и прохождениетактовых импульсов. Устройство готово к выполнению очередной программыуправления,Таким образом, предложенный программируемый контроллер позволяетрасширить область его использованияследующим образом, так как позволяет вццавать программу управления взависимости от внешних условий (условий объекта управления), что повышает гибкость управления (на основеадаптации к внешним условиям и переходу в зависимости от них к выполнению той или иной подпрограммы). Вовремя выдачи одного "длинного" управляющего сигнала, выдаваемого с одноговыхода контроллер позволяет производить вццачу нескольких "коротких"управляющих сигналов с другого выхода или выходов. Это значительно повьшает быстродействие как самого контроллера, так и системы в целом, Быстродействие контроллера повышается благодаря .тому, что расширение Функциональных возможностей приводит к совмещению времени выборки из памяти очередной команды управления со временем выполнения предыдущей команды, а также тем обстоятельством, что моменты окончания одних сигналов управления могут задаваться началом выполнения других сигналов: При этом выдача третьих управляющих сигналов может сохраняться. Возможность в момент окончания одних сигналов начинать выполнение других сигналов в каждом такте дает выигрыш во времени, равный времени выборки информации из памяти. Поэтому повышение быстродействия объекта управления, например станка с числовым программным управлением, достигается широкими Функциональными возможностями программируемого контроллера.Ф о р м у л а и з о б р е т енияПрограммируемый контроллер, содержащий первый и второй запоминающие блоки, триггер пуска, генератор тактовых импульсов, элементы согласования, мультиплексор адреса, реглстр адреса, счетчик адреса, дешифратор, регистр памяти, формирователь импульса, счетчик, элемент И, причем информационные входы контроллера соединены с входами элементов согласования,. выходы которых соединены с первыми информационными входами мультиплексора адреса, выход мультиплексора адреса соединен с входом реги-е стра адреса,:выход регистра адреса и выход счетчика адреса соединейы с входами дешифратора, выходы кото рого соединены с входами первого и второго запоминающих блоков, выход первого запоминающего блока соединен с входом регистра памяти, выход первого поля второго запоминающего блока соединен с информационным входом счетчика, первый управляющий вход контроллера соединен с единичным входом триггера пуска, единичный выход которого соединен с управляющим входом генератора тактовых импульсов выход генератора тактовых импульсов соединен с первым входом элемента И, выход которого соединен с вычитающим7 12 б 2 входом счетчика, о т л и ч а ю щ и йс я тем, что, с целью расширения функ" циональных возможностей путем формирования произвольных длин управляющих сигналов, контроллер дополнительно содержит триггер управления, триггер останова, выходной регистр, мультиплексор логических условий, второй, третий и четвертый элементы И, три элемента ИЛИ, два элемента . 10 задержки и элемент НЕ, причем второй управляющий вход контроллера соединен с первым управляющим входом мультиплексора адреса, с единичным входом триггера останова и первым входом 15 первого элемента ИЛИ, выход которого соединен с единичным входом триггера управления, единичный выход триггера управления соединен с входом формирователя импульсов, выход которого сое динен с первым входом второго элемента И, выход второго элемента И соединен с входом установки в нуль выходного регистра и регистра памя-. ти, выход генератора тактовых импульсов соединен с первым входом третьего элемента И, выход которого соединен с первым входом четвертого элемента И и входом первого элемента задержки, выход первого элемента за- щ держки соединен с нулевым входом триггера управления,.нулевой выход кото" рого соединен с вторым входом четвертого элемента И, выход которого соединен с синхронизирующим входом дешифратора и входом второго элемента задержки, выход второго элемента за" держки соединен со счетным входом 451 8счетчика адреса, единичный выход триггера останова соединен с вторым вхо дом третьего элемента И, выход кода проверяемых логических условий регистра памяти соединен с первым информационным входом мультиплексора логических условий, второй информационный вход контроллера соединен с вторым информационным входом мульти.плексора логических условий, выход которого соединен с первым входом второго элемента ИЛИ, выход модифицируемого разряда регистра памяти соединен с вторым входом второго элемента ИЛИ, выход немодифицируемого кода адреса регистра памяти соединен с вторым информационным входом мультиплексора, выход второго элемента ИЛИ соединен также с вторым информационным входом мультиплексора, выходы второго поля второго запоминающего блока соединены с счетными входами выходного регистра, выходы которого являются выходами контроллера, управляющий выход второго за" поминающего блока соединен с нулевыми входами триггера пуска и триггера останова, единичные выходы счетчика соединены с входами третьего элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и входом элемента НЕ, выход элемента НЕ соединен с вторым входом второго элемента И и третьим входом третьего элемента И управлякюций разряд выходного регистра, соединен с вторым входом первого элемента ИЛИ и вторьщ управляющим входом мультиплексора адреса.12 б 2451 РЫБ. Сост Техр ель В. Апарин Попович рректор В. Бутяга тор Г. Волк каэ 5424/44 Тираж 836 ПоВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Иосква, Ж, Раушская наб д. 4/5 сное графическое предприятие, г. Ужгоро Проектная Производственно

СмотретьЗаявка

3801641, 10.10.1984

ВОЙСКОВАЯ ЧАСТЬ 11284

МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ЯМНОВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: G05B 19/18

Метки: контроллер, программируемый

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/6-1262451-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Устройство для управления манипулятором

Следующий патент: Устройство для программного управления

Случайный патент: Механическое вычислительное устройство