Устройство для испытания электронных логических схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1262430

Автор: Семенычев

Текст

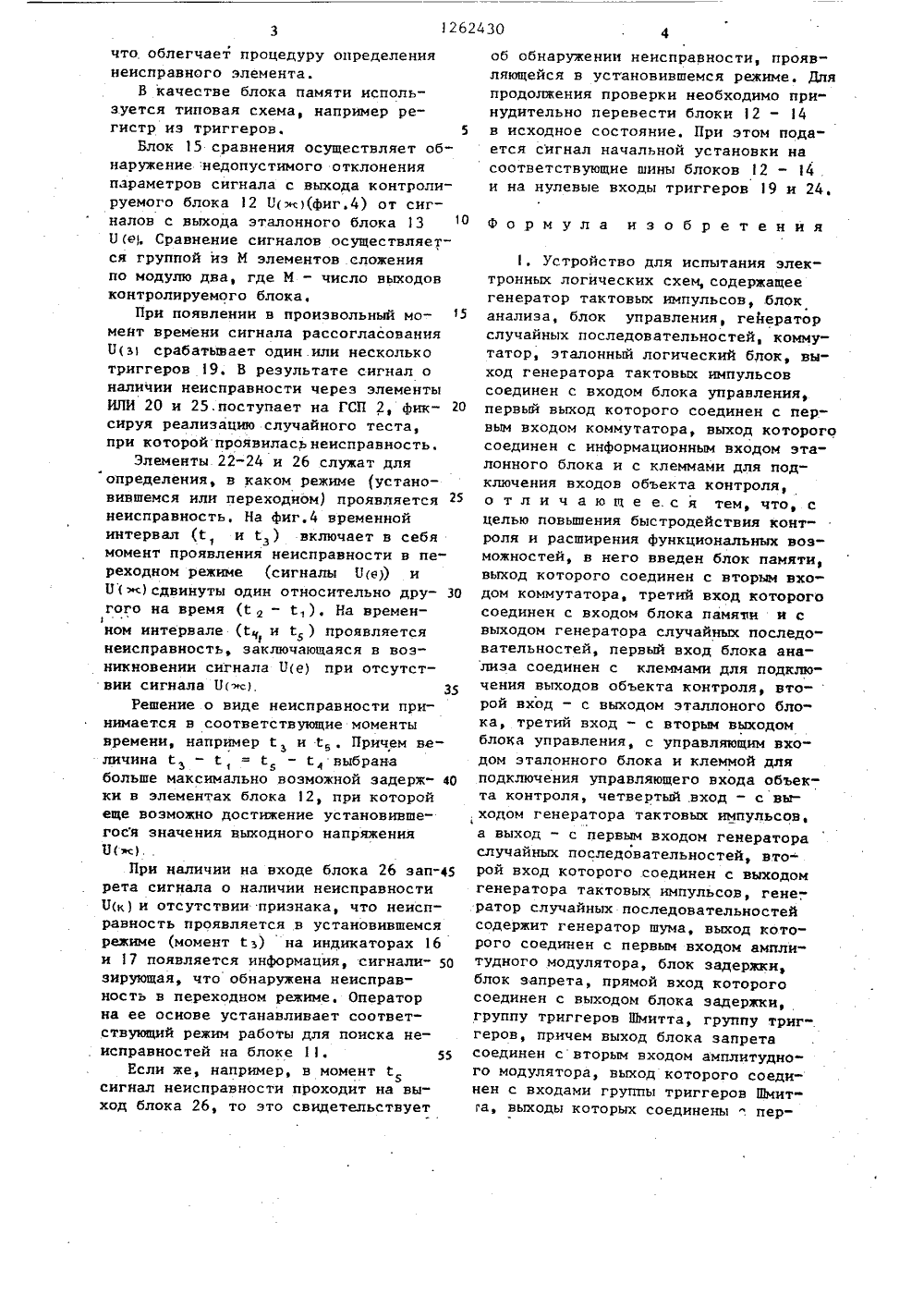

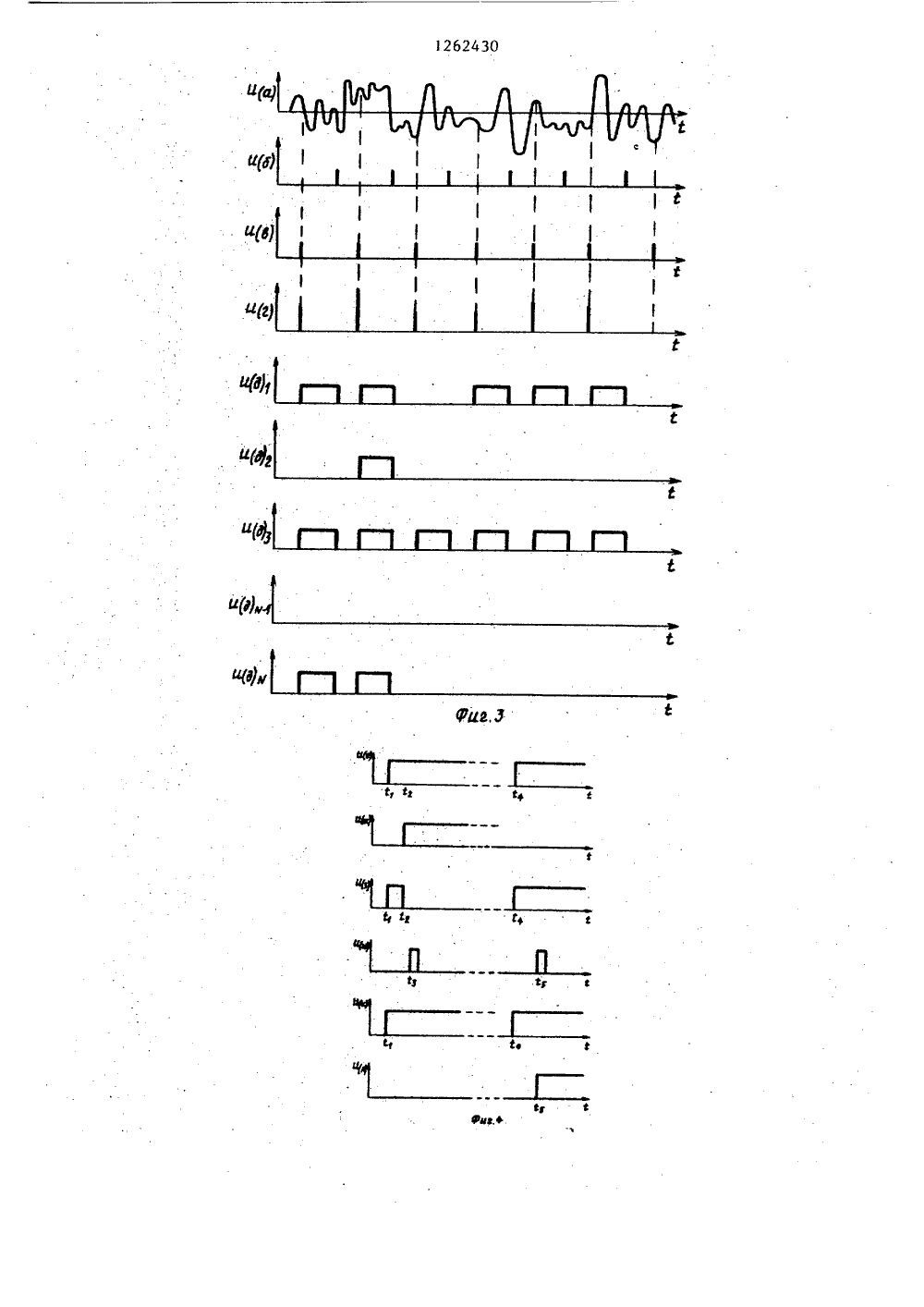

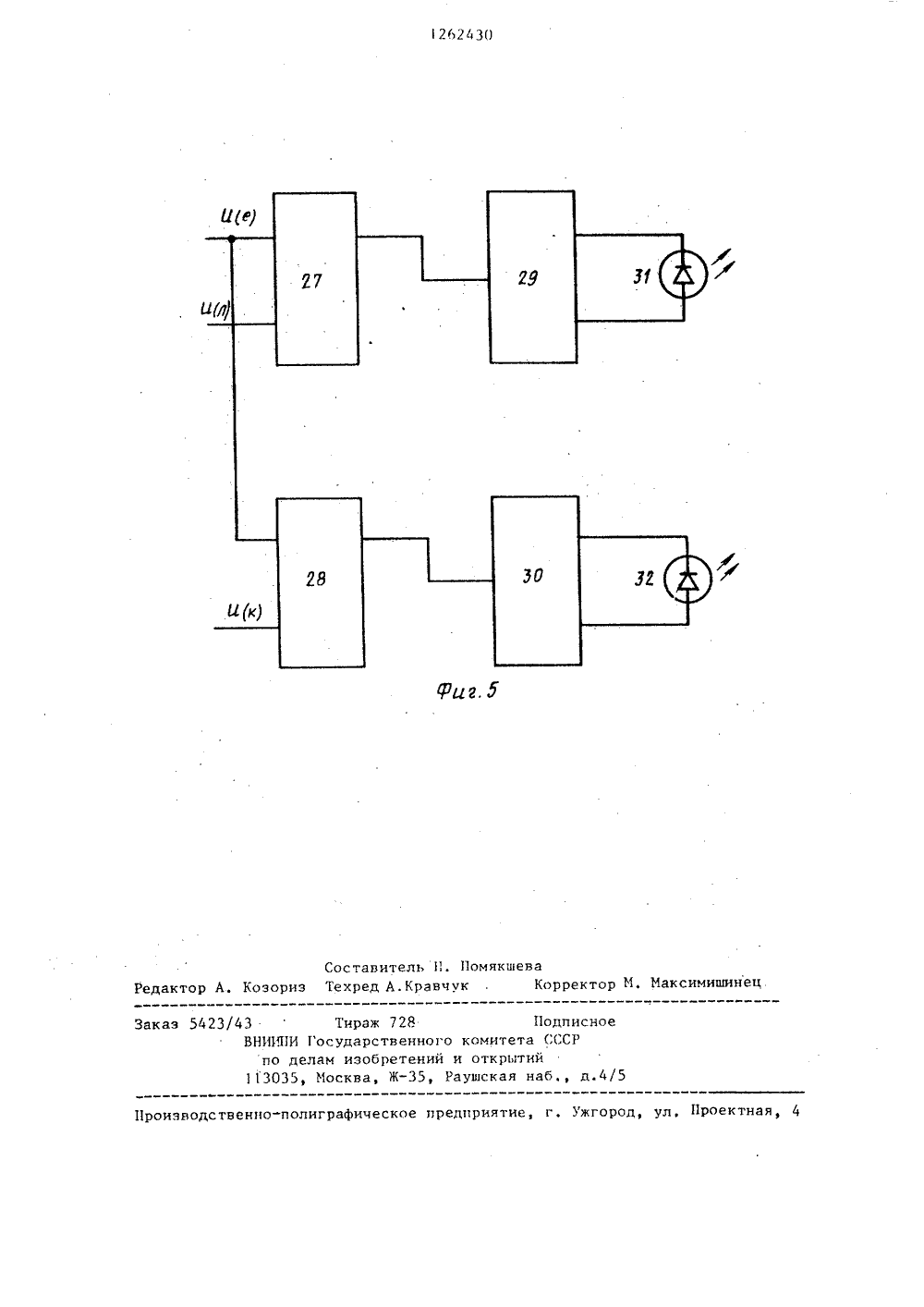

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ 62430 19) (11) СПУБЛИ 3128 ОМИТЕТ СССР ЕНИЙ И ОТНРЫТИЙГОСУДАРСТВЕННЬИ ПО ДЕЛАМ ИЗОБРЕ ИСАНИЕ ИЗОБРЕТЕНИ г,3 . ап4 Фс о ЕЛЬСТВУ ОРСКОМУ С 10, блокй блок 13, б ключающий блок 15 сравнения и индикаторы 16 и 17. Введение в устройство блока 9 памяти, выполнение генератора 2 случайных последовательностей в виде блока 3 задержки, блока 4 запрета, амплитудного модулятора 5, генератора 6 шума, триггеров 7.1 - 7.М Шмитта и триггеров 8.1 - 8.И, а также конкрет- ное выполнение блока 15 сравнения позволяет реализовать контроль логических блоков не только в установившемся, но и в переходном режимах при неограниченной длительности слу- СФ чайного теста. При этом упрощается схема генератора 2 случайных последовательностей за счет использования одноканальной схемы генератора случайного сигнала для формирования набора двоичных сигналов необходимой размерности. 1 з.п.ф-лы, 5 ил, Ьаи о СССР976. ронные М.; Ма(54) УСТРОЙСТВО ДЛЯ ИСПЫТАРОННЫХ ЛОГРЧЕСКИХ СХЕМ(57) Изобретение относитсятике и вычислительной технизобретения - повышение бывия контроля и расширениенальныхвозможностей устроройство содержит генераторвых импульсов, генератор 2ных последовательностей, к 11 управления, эталлоньлок 14 анализа в25 45 Индикаторы 16 и 17 содержат триггеры 27 и 28, усилители 29 и 30 мощности и элементы 32 и 32 индикации.Устройство работает следующим образом, 50Вырабатываемое ГШ 6 случайное напряжение поступает на АИ 5, где используется для модуляции задержанных тактовых импульсов ПЖ), снимаемых с блока 3 задержки и проходящих через 55 блок 4. Управление работой блока 4 осуществляется сигналом 0(к), снимаемьм с выхода элемента ИЛИ 25Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля логических схем (блоков), имеющих большое число входов, и определения не" исправностей в них.Цель изобретения " повышение быстродействия контроля и расширение функциональных возможностей за счет тоГо, что в каждом цикле работы уст ройства (с тактовой частотой устанавливается новая случайная последовательность на всех выходах генератора случайных последовательностей и дополнительной индикации неисправ ности, проявляющейся в переходном режиме.На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема блока сравнения; на фиг. 3 - идеализированные эпюры напряжений в обозначенных точках схемы по фиг,1; на фиг.4 - эпюры напряжений в обозначенных точках схемы по фиг.2; иа фиг,5 - функциональная схема блока индикацииеУстройство содержит генератор 1 тактовых импульсов (ГТИ), генератор .2 случайных последовательностей (ГСП), содержащий блок 3 задержки, блок 4 запрета, амплитудный модулятор 5 (АМ), генератор 6 шума 7.1 7.В. Шмитта, триггеры 8.1-8.И, блок 9 памяти, коммутатор 10, блок 11 управления (БУ), контролируемый блок 35 .12, эталонный блок 13, блок 14 анализа (БА), содержащий блок 15 сравнения и индикаторы 16 и 17.Блок 15 сравнения содержит, группу элементов 18 сложения по модулю 40 два, группу триггеров 19, элемент ИПИ 20, блок 21 задержки, элемент ИЛИ 22, элемент И 23, триггер 24, элемент ИЛИ 25 и блок 26 запрета. Средняя амплитуда импульсов 0(г)равна(П макс + Пмин ) 2 фгде П - напряжение срабатыванияэлемента из группы 7.17.И с максимальньщ пороговым напряжением;- напряжение срабатыванияэлемента из группы 7.17,Н с минимальным пороговым напряжением.При этом обеспечивается в случаеравномерного закона распределениянапряжения шума на входе АИ равнаявероятность всех возможных реализаций теста.Выходное напряжение АИ 5 представляет собой периодическую поспедовательность амплитудно-модулированныхимпульсов 11(г), которые поступаютодновременно на все М входов группытриггеров 7 Шмитта, имеющих различные пороги срабатывания, равномернораспределенные в интервале (П). На фиг.3 изображен случай,1когда минимальным напряжением срабатывания обладает третий триггер 7.3Шмитта, а наибольшим - (М)-й триггер. Соответствующие напряжения обозначены как 1)(д) и Щд),В зависимости от величины амплитуды импульса П(г) срабатываеттоили иное число триггеров Шмитта.В каждом такте реализация тестасуществует на выходе группы триггеров.8.1-8.М в течение времениТ а Та, Т Т, (2)где Т - период следования тактовыхимпульсовзадержка тактовых импульсов в блоке 3;- длительность тактовых.импульсов.Импульсы П(8) используются дляустановки триггеров 8 в исходное (нулевое) состояние. Длительность задержки в блоке 3 должна быть гДля обеспечения высокого быстродействия необходимо выбиратьа минимально возможной величины.Коммутатор 10 осуществляет подачу на входы блоков 12 и 13 одинаковых случайных реализаций теста с выхода генератора 2 или блока 9 памяти. Причем с выхода ГСП .2 сигнал снимается в режиме контроля. В режиме поиска неисправностей запомненная реализация теста поступает с выхода блока 9, 1262430что облегчает процедуру определениянеисправного элементаВ качестве блока памяти используется типовая схема, например регистр из триггеров. 5Блок 15 сравнения осуществляет обнаружение:недопустимого отклоненияпараметров сигнала с выхода контролируемого блока 12 Ц хс)(фиг,4) от сигналов с выхода эталонного блока 13П е), Сравнение сигналов осуществляется группой из М элементов сложенияпо модулю два, где М - число выходовконтролируемого блока,При появлении в произвольный момент времени сигнала рассогласованияП(з срабатывает один.или несколькотриггеров 19, В результате сигнал оналичии неисправности через элементыИЛИ 20 и 25,поступает на ГСП 2, фиксируя реализацию случайного теста,при которой проявиласьнеисправность.Элементы 22-24 и 26 служат дляопределения, в каком режиме установившемся или переходном) проявляетсянеисправность, На фиг.4 временнойинтервал (й, и Тз) включает в себямомент проявления неисправности в переходном режиме (сигналы 11 е иП(ж) сдвинуты один относительно другого на время ( д - й, ) . На временном интервале (С( и 1 ) проявляетсянеисправность, заключающаяся в возникновении сигнала П(е) при отсутствии сигнала Ц( с), 35Решение о виде неисправности принимается в соответствующие моментывремени, например й и 1 , Причем величина ъ1 5 14выбранабольше максимально возможной задерж" 40ки в элементах блока 12, при которойеще возможно достижение установившегося значения выходного напряженияП(При наличии на входе блока 26 зап рета сигнала о наличии неисправностиУк) и отсутствии признака, что неисправность проявляется в установившемсярежиме (момент йз) на индикаторах 16и 17 появляется информация, сигнализирующая, что обнаружена неисправность в переходном режиме. Операторна ее основе устанавливает соответствующий режим работы для поиска неисправностей на блоке 11, 55Если же, например, в моментсигнал неисправности проходит на выход блока 26, то это свидетельствует об обнаружении неисправности, прояв" ляющейся в установившемся режиме. Для продолжения проверки необходимо принудительно перевести блоки 12 - 14 в исходное состояние. При этом подается сигнал начальной установки на соответствующие шины блоков 12 - 4 и на нулевые входы триггеров 9 и 24,Формула изобретения1, Устройство для испытания электронных логических схем, содержащее генератор тактовых импульсов, блок анализа, блок управления, генератор случайных последовательностей, коммутатор, эталонный логический блок, выход генератора тактовых импульсов соединен с входом блока управления, первый выход которого соединен с первым входом коммутатора, выход которого соединен с информационным входом эталонного блока и с клеммами для подключения входов объекта контроля, о т л и ч а ю щ е е. с я тем, что, с целью повышения быстродействия контроля и расширения функциональных возможностей, в него введен блок памяти, выход которого соединен с вторым входом коммутатора, третий вход которого соединен с входом блока памяти и с выходом генератора случайных последовательностей, первый вход блока анализа соединен с клеммами для подключения выходов объекта контроля, второй вход - с выходом эталлоного блока, третий вход - с вторым выходом блока управления, с управляющим входом эталонного блока и клеммой для подключения управляющего входа объекта контроля, четвертый .вход - с вы,ходом генератора тактовых импульсов, а выход - с первым входом генератора случайных последовательностей, второй вход которого соединен с выходом генератора тактовых импульсов, гене-, ратор случайных последовательностей содержит генератор шума, выход которого соединен с первым входом амплитудного модулятора, блок задержки, блок запрета, прямой вход которогосоединен с выходом блока задержки, группу триггеров Шмитта, группу триг-.геров, причем выход блока запрета соединен свторым входом амплитудного модулятора, выход которого соединен с входами группы триггеров 111 мита, выходы которых соединены ". пер 3 12624выми входами группы триггеров, вторые входы которых соединены с вторымвходом генератора случайных последовательностей, а выходы - с выходомгенератора случайных последовательностей, инверсный вход блока запретаи вход блока задержки соединены соответственно с первым и вторым входамигенератора случайных последовательностей, блок анализа содержит блок 10сравнения и два индикатора, входыуправления которых соединены с входомуправления блока сравнения, с третьим входом блока анализа, первый ивторой входы блока сравнения соединены соответственно с первым и вторым входами блока анализа, третийвход - с четвертым входом блока анализа, а первый и второй выходы - синформационными входами первого и 20второго индикаторов соответственно,второй выход блока сравнения соединен с выходом блока анализа,1 2. Устройство по п.1, о т л и ч аю щ е е с я ,тем, что блок сравнения содержит группу из М элементов сложения по модулю два, группу из М триггеров, два элемента ИЛИ на М входов,третий элемент ИЛИ, элемент И, блок ЗО запрета, (М+1)-й триггер, блок задержки, причем выход каждого элемента сложения по модулю два соединен 30 Ьсоответственно с первыми входамитриггеров из группы М триггеров и ссоответствующими входами первого элемента ИЛИ на М входов, выход которогосоединен с первым входом элемента И,второй вход которого соединен с выходом блока задержки, а выход - спервым входом (М+1)-го триггера, второй вход которого соединен параллель-.но с вторыми входами триггеров изгруппы М триггеров, выход каждого изкоторых соединен с соответствующимивходами второго элемента ИЛИ на Мвходов, выход которого соединен спервым входом третьего элемента ИЛИи прямым входом блока запрета, выход(М+1)-го триггера соединен с вторымвходом третьего элементаИЛИ и инверсным входом блока запрета, входблока задержки соединен с третьимвходом блока сравнения, вторые входытриггеров группы из М триггеров и(М+1)-го триггера соединены с входомуправления блока сравнения, первыевходы М элементов сложения по модулюдва соединены с первым входом блокасравнения, а вторые входы М элементов сложения по модулю два - с вторым входом блока сравнения, выходтретьего элемента ИЛИ является первымвходом блока сравнения, а выход блоказапрета - вторым выходом блока сравнения.126243 Составитель П. Помякшеваз Техред А.Кравчук . Корректор М, Максимишин К Редак аказ 542 д, ул, Проектная, 4 оизводственцо-полиграфическое предприят ж 3 ТираВНИИПИ Государпо делам изо113035, Москва 728 Подписноевенного комитета СССРетений и открытийЖ, Раушская наб д.4/5

СмотретьЗаявка

3807016, 31.10.1984

ВОЙСКОВАЯ ЧАСТЬ 75360

СЕМЕНЫЧЕВ АНАТОЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G01R 31/3177

Метки: испытания, логических, схем, электронных

Опубликовано: 07.10.1986

Код ссылки

<a href="https://patents.su/6-1262430-ustrojjstvo-dlya-ispytaniya-ehlektronnykh-logicheskikh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для испытания электронных логических схем</a>

Предыдущий патент: Способ определения места замыкания жил кабеля

Следующий патент: Устройство для измерения тока среза

Случайный патент: Несимметричная многофазная петлевая обмотка