Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1234974

Автор: Гельтман

Текст

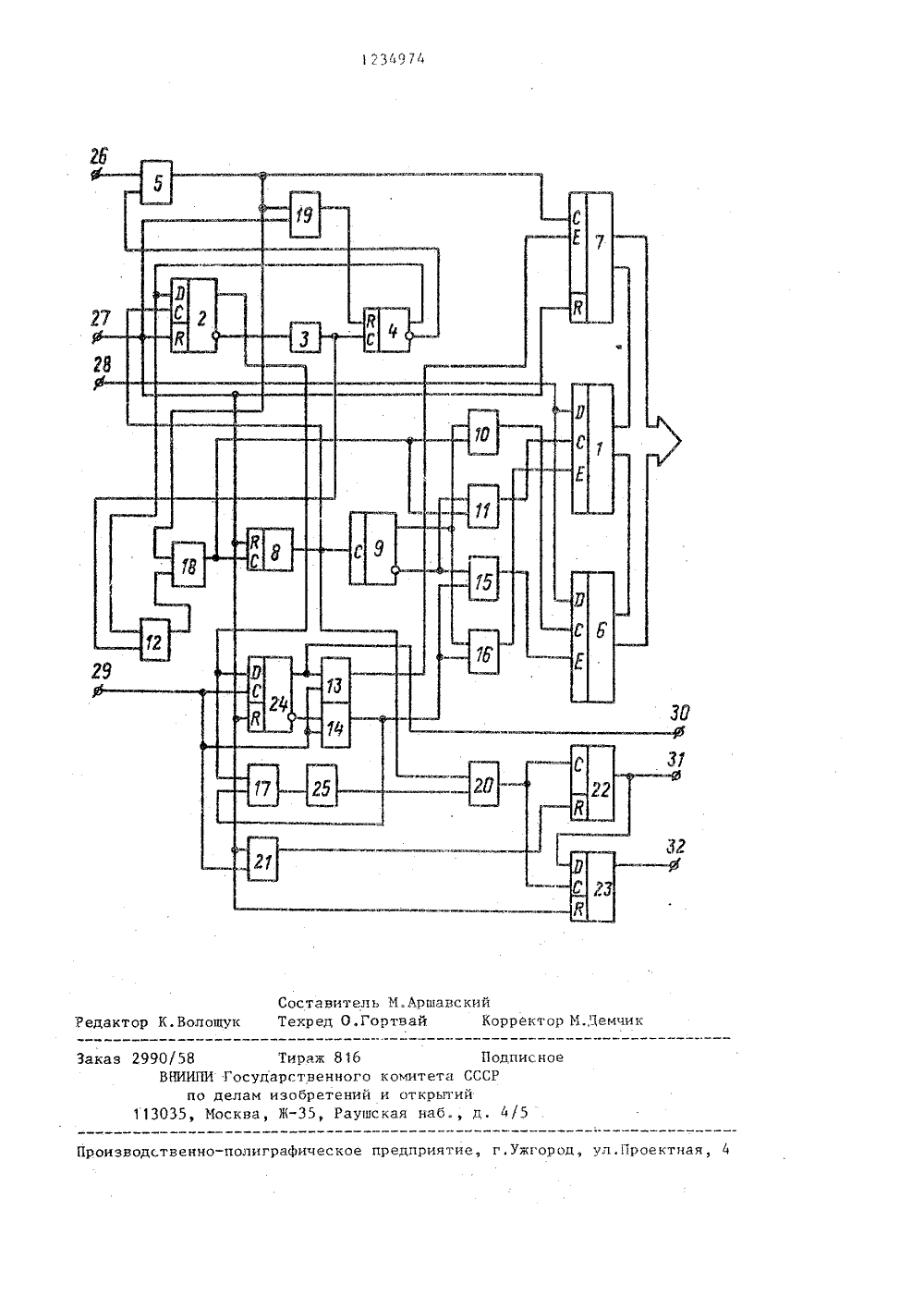

ОЮЗ СОНЕТСНИХ ЦИАЛИСТИЧЕСН ПУБЛИН 09) Л 2 п 4, Н 03 И 7/(54) ПРЕНОГО КОДА (57) Изоцифровой осится к ной техн областики и ретение от вычислител ользоватьс может и и п роениипреобрараллельно-посл ательных ователе елью из и устроиретения я ве сопряжения сциреляетс ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ БРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬ- В ПАРАЛЛЕЛЬНЫИ . ние класса решаемых задач эа счет обеспечения преобразования кодов произвольной разрядности, а также пов., - шение быстродействия преобразователя. Преобразователь содержит два сдвиговых регистра, счетчик числа разрядов, распределитель импульсов, делитель частоты, генератор импульсов, пять триггеров, элементы И, ИЛИ, элемент задержки. Преобразователь обеспечивает прием и преобразование кодов произвольной разрядности и сокращение времени преобразования за счет попеременного приема в первый и второй сдвиговые регистры. Кроме того, преобразователь дает возможность орга- Ж пизадии асинхронно . выдачи полученной информации потребителю. 1 ил .С."Изобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей в устройствах сопряжения и обмена информацией. 5Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования кодов произвольной разрядности, а также повышение быстродействия преобразователя. 1 бНа чертеже приведена блок-схема предлагаемого преобразователя.Преобразователь последовательного кода в параллельный содержит первый сдвиговый регистр 1, триггер 2 управ ления, генератор импульсов 3, счетчик 4, элемент И 5, второй сдвиговый регистр 6, счетчик числа разрядов 7, делитель частоты 8, триггер 9 записи информации, элементы И 10 - 17, элементы ИЛИ 18 - 21, триггер 22 готовности, триггер 23 неисправности, триггер 24 ввода информации, элемент задержки 25, вход синхронизации преобразователя 26, установочный вход пре-образователя 27, информационный вход преобразователя 28, вход съема информации 29, выход конца сообщения 30, выход готовности 31, выход неисправности 32, Выходы одноименных разрядов сдвиговых регистров 1 и 6, а также счетчика числа разрядов 7 объединены и подключены к информационному выходу преобразователя.Преобразователь работает следую- З 5 щимобразом.На установочный вход преобразователя 27 подается запускающий импульс, который обнуляет счетчики 4 и 7, делитель 8, триггеры 2, 22, 23 и 24, подготавливая преобразователь к приему информации. При этом на вход генератора импульсов 3 и вход элемента И 5 поступает потенциал логической единицы с инверсных выходов триггера управления 2 и счетчика 4 соответственно. Это обеспечивает запуск генератора 3 и открытие элемента И 5 для приема синхроимпульсов, сопровождающих .информацию. Поступающие на вход преобразователя 26 синхроимпульсы через элемент И 5 проходят на вход счетчика числа разрядов, который считает количество бит в информационной последовательности, через элемент ИЛИ 18 на вход делителя частоты 8, коэффициент деления которого равен разрядности первого и второго.двиговых регистров 1 и 6, а также а входы элементов И 10 или 11, В зазисимости от состояния счетного триггера записи 9 синхроимпульсы с выхода элементов И 10 или 11 поступают на вход синхронизации первого или второго сдвигового регистра. Информационные входы сдвиговых регистров 1и 6 объединены, но информация записывается в один из регистров. Как только на выходе делителя частоты 8 появляется импульс переноса, по заднему Фронту которого переключается счетный триггер записи информации 9 и устанавливается триггер готовности 22 целитель частоты 8 обнуляется и начинает новый цикл счета, а инФормация будет записываться в другойсдвиговый регистр, Сигнал логическойединицы с триггера готовности 22 поступает на выход преобразователя 31,сообщая потребителю о готовности преобразователя к вьдаче параллельного кода.Потребитель, получив сигнал готовности, подает на вход преобразователя 29 импульс информации, который обнуляет триггер готовности 22 и поступает через элемент И 14 и одич иэ элементов И 15 или 16 в зависимости от состояния триггера записи информации 9 на вход управления выходными ключами заполненного сдвигового регистра. При этом информация,которая запоминается в сдвиговом регистре, вьдается на информационный выход преобразователя . Когда заполнится другой сдвиговый реГистр, по заднему фронту импульса переноса делителя частоты 8 вновь устанавливается триггер готовности 22, вырабатывающий готовность преобразователя к вьдаче параллельного кода, и переключается счетный триггер записи инФормации 9, который управляет поочередной записью информации в сдвиговые регистры 1 и 6. Потребитель, получив сигнал о готовности, посылает на вход преобразователя 29 импульс ввода информации, по которому обнуляется триггер готовности 22 и информация со второго заполненного сдвигового регистра вьдается на информационный выход преобразователя. Информация, поступающая на вход преобразователя, поочередно записывается в сдвиговые регистры 1 и 6, после чего считывается потребителем4974 123 по сигналу готовности преобразователя,Циклы записи и считывания продолжаются до прекращения входных импульсов, конец поступления которых опре - деляет счетчик 4, На вход счетчика 4 поступают импульсы с выхода генератора 3, а с выхода элемента И 5 черезэлемент ИЛИ 19 на вход начальной установки счетчика 4 поступают входныесинхроимпульсы преобразователя. По 10прекращению входных синхроимпульсовсчетчик 4, отсчитав определенное числб периодов импульсов генератора 3, . выдает управляющий сигнал логической единицы на триггер управления 2 и 15элемент И 12, через который импульсыгенератора 3, поступающие на второй вход элемента И 12, пройдя через элемент ИЛИ 18, поступают на вход делителя частоты 8 и через один из элемен о тов И 10 или 11 на вход синхронизации соответствующего сдвигового регистра, а с инверсного выхода счетчика 4 на вход первого элемента И 5 поступает сигнал логического нуля, за 25крывающий элемент И 5 для приема синхроимпульсов. Выходной сигнал со счетчика 4 должен выдаваться через время, превьппающее период следования синхроимпульсов, а количество от-осчитываемых счетчиком 4 периодов импульсов генератора 3 должно превьппатькоэффициент деления делителя частоты 8, По заднему Фронту импульса переноса делителя частоты 8 переключаетсятриггер записи 9, устанавливается триг 35гер готовности 22 и переключается триггер управления 2, так как на управляющем его входе присутствует сигнал логической единицы, поступающий со40счетчика 4. При этом выключается генератор 3 импульсов, а конец информационной последовательности дополняетсянулями до полного слова, запоминаемый сдвиговым регистром, причем стар-.45шие разряды конца информационной последовательности окажутся в старшихоазрядах сдвигового регистра. Получив сигнал готовности, потребитель подает на вход преобразоваб тели 29 импульс ввода, по которому последнее слово сообщения выдается на выходную информационную шину. При этом сбрасывается триггер готовности 22, а по заднему фронту импульса .ввода переключается триггер ввода информации 24, так как на его управляющем входе присутствует сигнал ло 4гической единицы, поступающий с триггера управления 2, Сигнал с выхода триггера ввода информации 24 посту - пает на выход преобразователя 30, по которому потребителю сообщается оконце массива информации. Тот же импульс ввода с выхода элемента И 14 проходит через элемент И 17, так как на управляющем его входе присутствует сигнал логической единицы, поступающий с триггера управления 2, элемент задержки 25, элемент ИЛИ 20 и вновь устанавливает триггер готовности 22. Потребитель, получив сигнал готовности, выдает на вход преобразователя 29 импульс ввода информации, который сбрасывает триггер готовности 22, проходит через элемент И 13, так как на его управляющем входе присутствует сигнал логической единицы, поступающий с триггера ввода информации 24. С выхода элемента И 13 импульс ввода информации поступает на вход управ. ления выходными ключами счетчика числа разрядов 7, при этом информация со счетчика выдается на информационные выходы преобразователя. Содержимое счетчика бит информации 7 указазывает потребителю на значащие разряды последнего принятого слова. Таким образом, сигнал на выходе преобразователя 30 указывает потребителю, что следующая информация будет поступать о количестве значащих разрядов в последнем слове. Для приема следующей информационной посылки необходимо подать на установочный вход преобразователя 27 импульс запуска, при этом преобразователь переходит в исходное состояние, которое позволяет принимать следующее информационное сообщение. Если потребитель, получив сигнал готовности, не подаст сигнал ввода за время записи очередного слова, на управляющий вход триггера неисправности 23 поступает сигнал логической единицы с триггера готовности 22, а после записи очередного слова сигнал с выхода делителя частоты 8, пройдя через элемент ИЛИ 20, поступает на вход синхронизации триггера неисправности 23, который установится по его заднему Фронту, сообщая потребителю о нарушении порядка обмена с преобра- зователем. Если при запуске преобразователя информация и сопровождающие ее синхроимпульсы не поступают навходы преобразователя 26 и 28, счетчик 4, отсчитав определенное количество импульсов генератора 3, закры вает элемент И 5 и подает сигнал логической единицы на входы элемента И 12 и триггера управления 2, после чего импульсы генератора 3 проходят с выхода элемента И 12 и через элемент И 11 И 18 на входы элементов 10 10 и 11 и на вх:;елитегя частоты 8. 1 р этомвыхода элемента И 10 или 11 в зависимости от состояния триггера записи 9 на вход синхрониза. ции первогоили второго 6 сдвигово го регистра поступают импульсы генератора 3, ио которым в соответствующий сдвиговый регистр запишется нулевая информация, По окончании записи делителем частоты 8 вырабатывается 2 О импульс переноса, который задним Фрон том устанавливает триггер управления 2 и триггер готовности 22, При этом выключается генератор 3, а на выходе преобразователя 31 устанавли вается потенциал логической единицы, готовности преобразователя к выдаче информации, Потребитель, получив сигнал готовности. подает на вход преобразователя 29 сигнал ввода инфор,а- зо ции, по которому производится считывание нулевой информации со сдвигового регистра, сбрасывается триггер готовности 22, устанавливается триггер ввода информации 24, так как на управляюшй вход триггера ввода 24 поступает сигнал логической единицы с триггера управления 2. При этом на выходе преобразователя 30 появляется сигнал логической единицы который сообщает потребителю о конце информации и о том, что вслед за этим последует информация о количестве значащих разрядов в последнем слове. Тот же импульс ввода информации проходитвыхода элем та И 14 через эл"- мент И 17, так как на управляющем входе .:пемента И 17 присутствует потенциал логической единицы, поступающий с триггера управления 2, элемент задержки 25, элемент ИЛИ 20 и вновь устанавливает триггер готовности 22, Получив сигнал готовности потребитель посылает па вход преобразователя 29 импульс ввода информации кото 55 рый проходит через элемент И 13, так как триггер ввода информации устаОВ - лен в единицу предыдущим импульсом ввоцйинформации, и поступает на вход управления выходными ключами счетчика 7, Прн этом на информационно выход преобразователя выдается пулевая информация со счетчика 7, что ука.зывает на отсутствие значащих разрядов в предыдущем слове.Изобретение по сравнению с преобразователем 2 отличается более высокой скоростью преобразования непрерывной кодовой последовательности в и-разрядный параллельньгй код, так как при использовании двух сдвиговых регистров импульс ввода информации можно подавать после получения сигнала готовности через время и Т, где и - разрядность сдвиговых регистров , Т - период следования синхроим.ульсов, что повышает в и раз скорость преобразования информапии,Предлагаемое устройство позволяет преобразовывать последовательный код любой разрядности в параллельнй код что повышает универсальность преобразователя. Введение триггера готовности обеспечивает асинхронную передачу параллельного кода потребителю. Введение триггера аварии повыпает достоверность преобразования информации.Формула изобретенияПреобразователь последовательного кода в параллельный согержащий пер-. вый сдвиговый регист, триггер управления, генератор импульсов, первый элемент И, первый вход которого соединен с входом синхронизации преобраздвателя, информационный вход которого соединен с. информационным входом первого сдвигового регистра, а установочный вход преобразователя соединен с нулевым входом триггера управления, инверсный выход которого соединен с входом генератсра импульсов, выход которого соединен с синхровходом счетчика, о т л и ч а ющ и и с я тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности преобразования кодов произвольной разрядности и човыеия быстродействия, в него введены второй сдвиговый регистр, счетчик числа разрядов, делитель частоты, триггер записи информации, девять элементов И, четырс элемента РХИ, элемент задержки, триггер го товности, триггер неисправности,триггер ввода информации, выходытриггеров являются соответственно выходом готовности, выходом неисправности и выходом ввода информации преобразователя, информационные выходыкоторого соединены с выходами второго сдвигового регистра и выходамисчетчика числа разрядов, вход сицхроцизации которого соединен с выходом первого элемента И и первымивходами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с установочнымвходом преобразователя и выходом второго элемента И, первый вход которогосоединен с прямым выходом счетчикаи информационным входом триггерауправления, прямой выход которогос оеди не н с информационным входом три ггера ввода информации и первым входомтретьего элемента И, выход которогочерез элемент задержки соединен спервым входом третьего элемента ИЛИ, 25выход которого соединен с синхровходами триггера готовности и триггеранеисправности, нулевой вход которогосоединен с уста.новочным входом преобразователя, входами сброса делителячастоты и триггера ввода информациии с первым входом четвертого элемен -та ИЛИ, второй вход которого соединен с входом съема информации преобразователя, с синхровходом триггераввода информации и первыми входамичетвертого и пятого элементов И, вторые входы которых соединены соответственно с прямым и инверсным вьгходами триг гера ввода информации, выходы четвертого и пятого элементов И соединены соответственна с вхопом разрешения выдачи счетчика числа разрядови первыми входами шестого и седьмого элементов И, выходы которых соединены соответственно с входами разре 1 пения выдачи первого и второго сдвиговых регистров, синхровходы которых соединены соотве гственно с выходами восьмого и девятого элементов И, первые входы которых соединены с выходом второго элемента ИЛИ и с синхровходом делителя частоты, выход кото.рого соединен с синхровходом триггера управления, вторым входом третьего элемента ИЛИ и синхровходом триггера записи информации, прямой выход которого соединен с вторыми входами шестого и девятого элементов И, а ин. версный выход триггера записи информации соединен с вторыми входами седьмого и восьмого элементов И, выход первого элемента ИЛИ соединен с нулевым входом счетчика, инверсный вход которого соединен с вторым входом первого элемента И, выход генера" тора импульсов соединен с вторым входом второго элемента И, выход четвертого элемента ИЛИ соединен с нулевым входом триггера готовности, выход которого соединен с информационным входом триггера неисправности, информационный вход второго сдвиговаго регистра соединен .; информационным входом преобразова:еля, выход пятого ,элемента И соединен с вторым входом третьего элемента И.ректор М,немчик дписн роизводственно-полиграфическое предприятие, г.ужгород, ул.Проектная,аказ 2990/58 ВНИИПИ Госу по делам 113035, МоскваТираж рстве зобре Ж,81 б По ного комитета СССР ений и открытий Раущская наб., д. 4/5

СмотретьЗаявка

3737123, 07.05.1984

ПРЕДПРИЯТИЕ ПЯ М-5068

ГЕЛЬТМАН МИХАИЛ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 30.05.1986

Код ссылки

<a href="https://patents.su/6-1234974-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для декодирования кода манчестера

Следующий патент: Устройство оценки качества дискретных сигналов

Случайный патент: Подъемные ворота судостроительного эллинга