Преобразователь синусоидальных сигналов перемещения в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

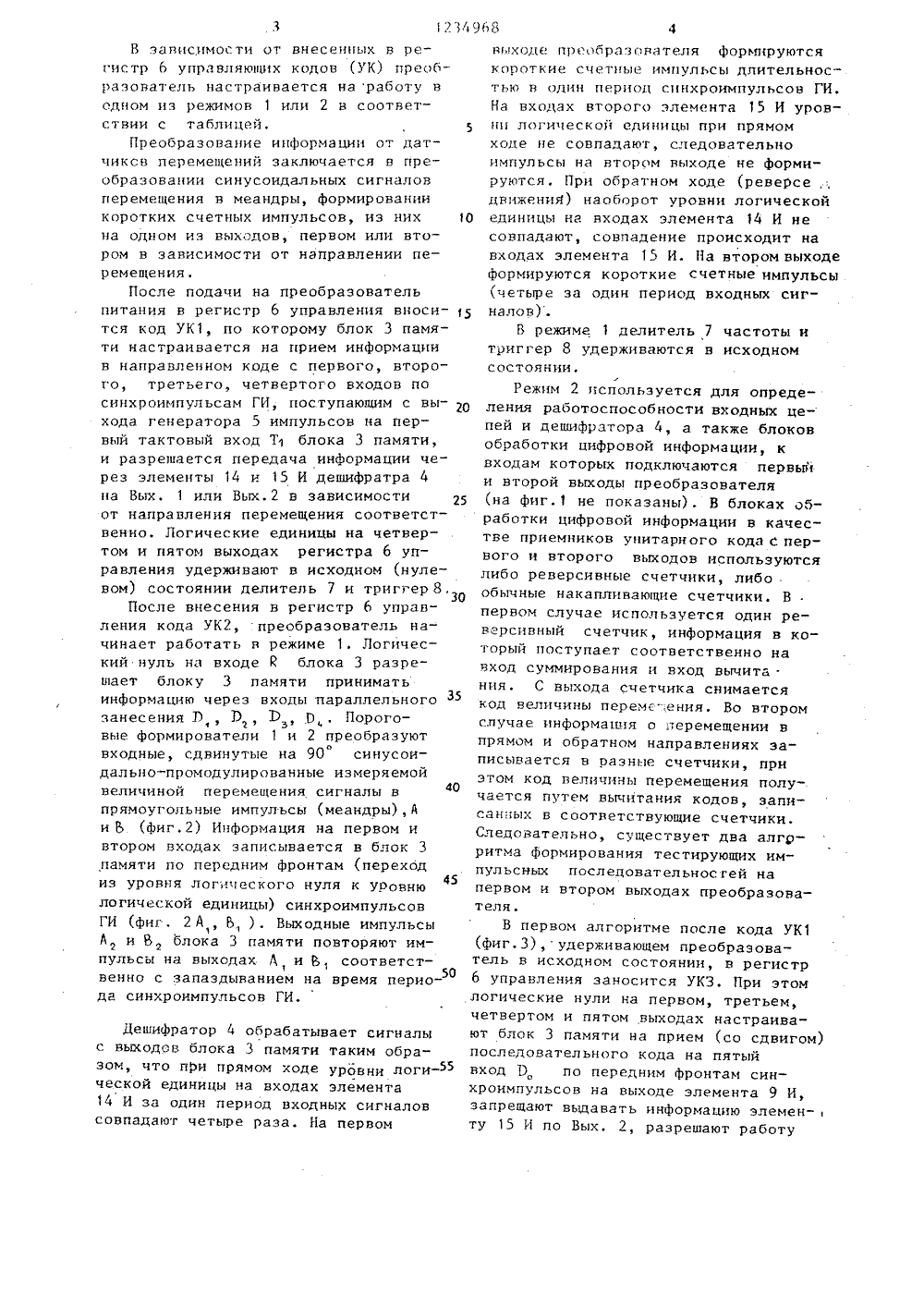

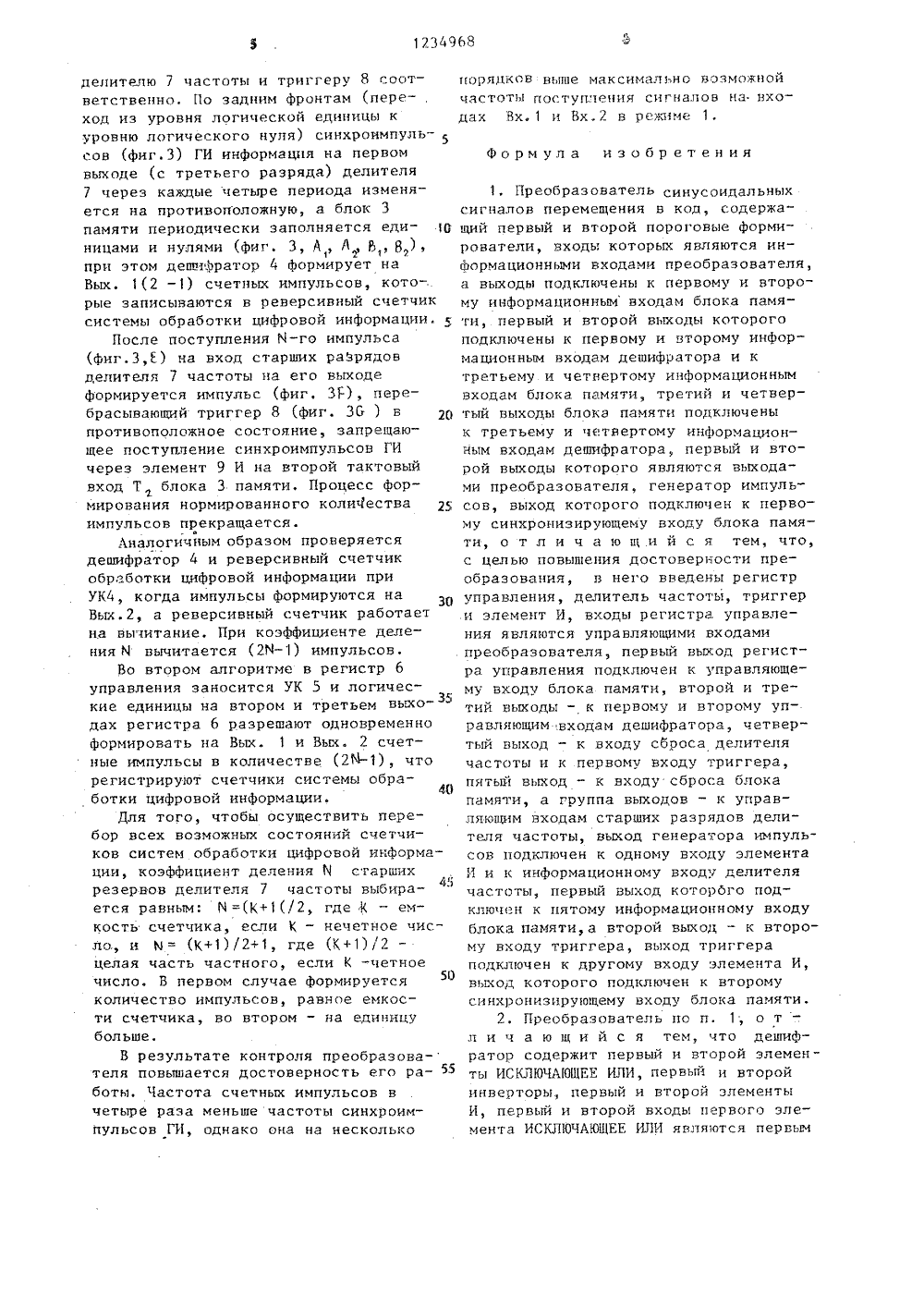

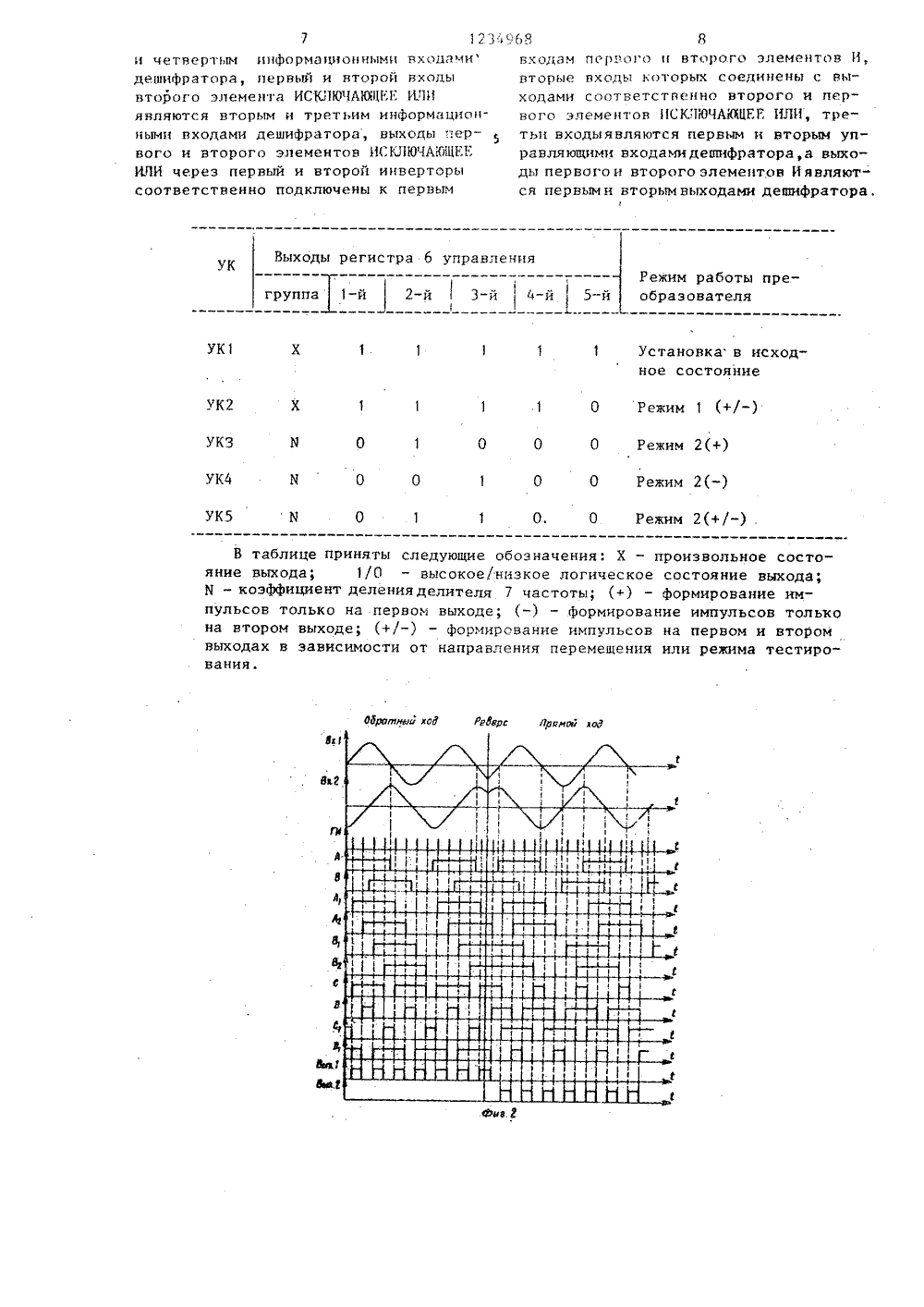

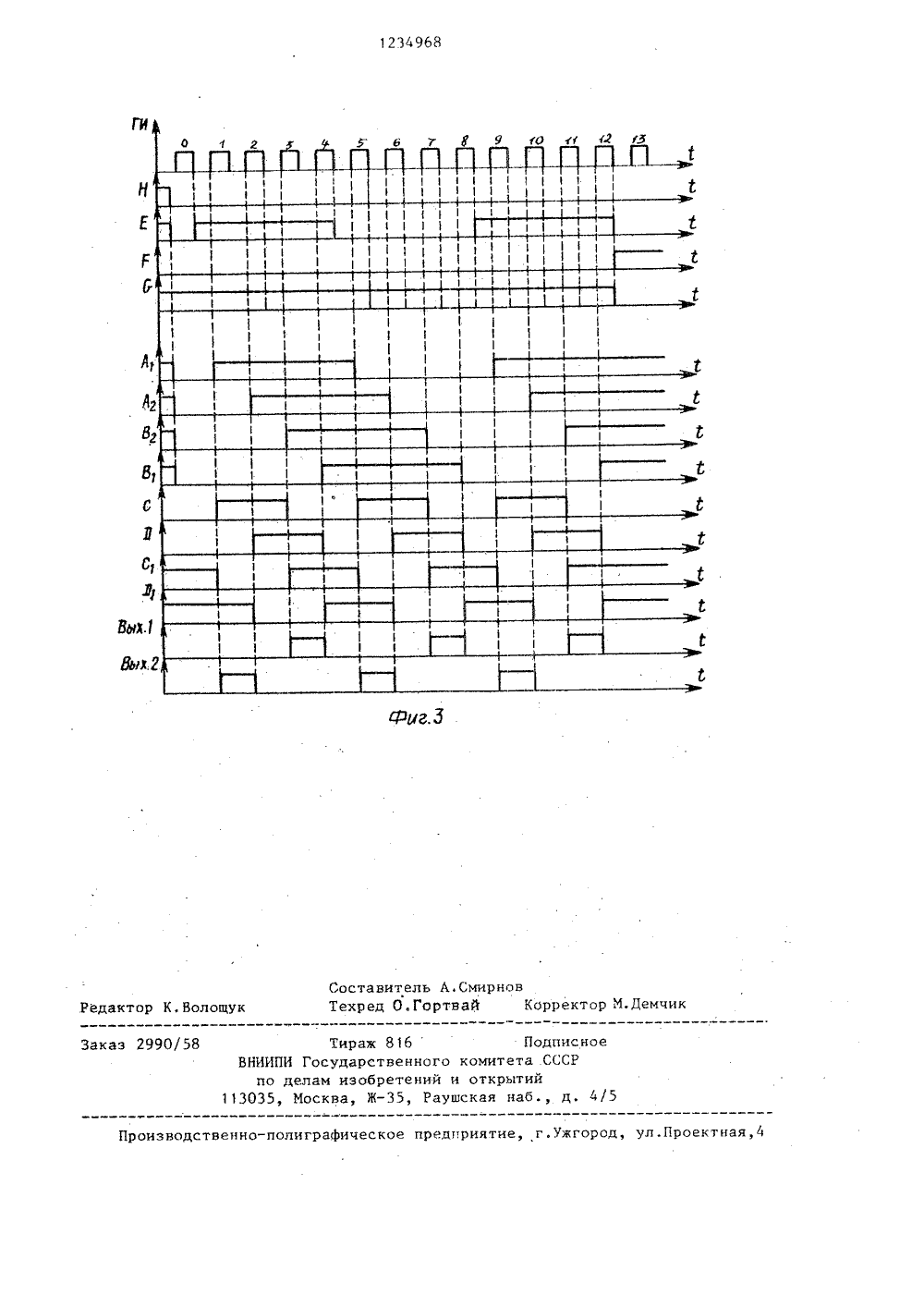

/ НИ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРГО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ.(56) Авторское свидетельство СССР Ф 847333, кл, С 08 С 9/00, 1979.Авторское свидетельство СССР В 591899, кл, С 08 С 9/00, 1975, (54) ПРЕОБРАЗОВАТЕЛЬ СИНУСОИДАЛЬНЫХ СИГНАЛОВ ПЕРЕМЕЩЕНИЯ В КОД (57) Изобретение относится к области автоматики и вычислительной техни ки и может быть использовано для сня зи аналоговых источников информации с цифровым вычислительньм устройством. С целью повышения достоверности преобразователя путем контроля его работоспособности перед началом работы синусный и косинусный сигналыс датчика перемещения через пороговые формирователи 1 и 2, соответственно, поступают на входы блока 3памяти, выполненного в виде сдвигающего регистра, синхронизирующийвход которого соединен с генератором5 импульсов. На выходе блока 3 Формируются четыре последовательностипрямоугольных сигналов, относительноерасположение которых определяетсянаправлением перемещения, т.е. последовательностью изменения входныхсигналов пороговых формирователей 1и 2, Дешифратор 4 в первом реимеработы преобразователя Формирует извыходных сигналов блока 3 последовательности импульсов приращения пер123 мещения на одном из двух входов взависимости от направления перемещения. Для определения работоспособности преобразователя в него введень 1 делитель 7 частоты, триггер 8, элемент9 И и регистр 6 управления которыйопределяет работу преобразователя врежиме контроля или в режиме измерения. В режиме контроля с промежуточного выхода делителя 7 на иыформаци 4968Оинь 1 Й вход блока Э пос тупа ют 15 мпул ьсы, имитирующие приращение перемещения, а через элемент 9 И поступаютсинхронизирующие импульсы. ПО Окончании цикла проверки на выход преобразователя должно поступить определенноеколичество импульсов, которое сравнивается с расчетным ипо результату сравнения определяютработоспособностьпреобразователя.1 з.п.ф-лы,Зилтабл.Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством.Целью изобретения является повышение достоверности преобразователя.На фиг, 1 представлена структурная схема преобразователя; на Фиг. 2 - временная диаграмма работы преобразователя с датчиком перемещения, режим 1; на Фиг. 3 - временная диаграмма контроля преобразователя режим 2. Преобразователь содержит первый и второй 2 пороговые Формирователи, входы которых Ь х,1 и Ьх,1 являются информационными входами преобразователя, а выходы 1( и Ь подключены к первому и второму информационным входам блока 3 памяти, первыйи второй О, выходы которого подключены к первому и второму информационным входам дешифратора 4 и к третьему и четвертому информационным входам блока 3, третий А и четвертый Ь выходы блока Э подключены к тре 1тьему и четвертому информационным входам дешифратора 4, первый Бых.1 и второй Вых. 2 выходы которого являются выходами преобразователя, генератор 5 импульсов, выход которого подключен к первому синхронизирующему входу блока 3, входы регистра 6 управления являются управляющими входами преобразователя, первый выход регистра 6 подключен к управляющему входу блока 3, второй и третий выходы - к первому и второму управляющим входам дешифратора 4, четвертый выход - к входу сброса делителя 7 частоты, к первому входу триггера 8, пятый выход - к входу сброса блока 3,а группа выходов - к. управляющимвходам старших разрядов делитеь,ля 7, выход генератора 5 импульсов подключен к одному входу элемента 9 И и к информационному входуделителя 7 частоты, первый выход которого подключен к пятому информаци 10 Онному входу блока 3, а второй выходк второму входу триггера 8, выходтриггера 8 подключен к другому входуэлемента 9 И, выход которого подключенк другому синхронизирующему входу15 блока 3 памяти.дешифратор 4 содержит первый 10 ивторой 11 элементы ИСКЛКИИОЩЕЕ ИЛИ,первый 12 и второй 13 инверторы, первый 14 и второй 15 элементы И, первый20 и второй входы элемента 10. являютсяпервым и четвертым информационнымивходами дешифратора 4, первый ивторой входы элемента 11 являютсявтопь 5 м и третьим информационными вхо25 дами дешифратора 4, выход элемента 10и выход элемента 11 через первый 12и второй 13 инверторь 1 подключены кпервым входам (, и О, первого 14 и15 элеменгов И вторые входы которыхЗ 0 соединены с выходами элементом 11 и10 соответственно, третьи входы являются первым н вторым управляющимивходами дешифратора 4, а выходы эле -ментов 14 и 15 являются первым ивторым Выходами дешифратора 4. Первый и второй выходы делителя 7 частоты обозначены Е и Г , выход триггера 8 - Ь, четвертый выход регистра6-И,11 реобразоватепь работает следующимобразом, 1234968В зависимости от внесенных в регистр 6 управляющих кодов (УК) преобразователь настраивается на работу в одном из режимов 1 или 2 в соответствии с таблицей. 5Преобразование информации от датчиков перемещений заключается в преобразоваии синусоидальных сигналов перемещения в меандры, формировании коротких счетных импульсов, из них 1 О на одном из выходов, первом или втором в зависимости от направлении пе - ремещения.После подачи на преобразователь питания в регистр 6 управления вноси тся код УК 1, по которому блок 3 памяти настраивается на прием информации в направленном коде с первого, второго, третьего, четвертого входов по синхроимпульсам ГИ, поступающим с вы О хода генератора 5 импульсов на первый тактовый вход Т 1 блока 3 памяти, и разрешается передача информации через элементы 14 и 15 И дешифратра 4 на Вых. 1 или Вых,2 в зависимости от направления перемещения соответственно. Логические единицы на четвертом и пятом выходах регистра 6 управления удерживают в исходном (нулевом) состоянии делитель 7 и триггер 8,После внесения в регистр 6 управления кода УК 2, преобразователь начинает работать в режиме 1. Логический нуль на входе Й блока 3 разрешает блоку 3 памяти принимать информацию через входы параллельного занесения Г, В ,, .1. Пороговые формирователи 1 и 2 преобразуют входные, сдвинутые на 90 синусоидально-промодулированные измеряемой величиной перемещения сигналы в прямоугольные импульсы (меандры),А и Ь (фиг.2) Иформация на первом и втором входах записывается в блок 3 памяти по передним фронтам (переход из уровня логического нуля к уровню45 логической единицы) синхроимпульсов ГИ (фиг, 2 А, Ь) . Выходные импульсыи Ь блока 3 памяти повторяют импульсы на выходах Д и К, соответственно с запаздыванием на время периода синхроимпульсов ГИ. Дешифратор 4 обрабатывает сигналы с выходов блока 3 памяти таким образом, что при прямом ходе уровни логической единицы на входах элемента 14 И за один период входных сигналов совпадают четыре раза. На первом Вьходе п 1 образ она теля форлпЦ)уются короткие счетные импульсы длительностью в один период сцнхроимпульсов ГИ. На входах второго элемента 15 И уров- и логической единицы при прямом ходе не совпадают, следовательно импульсы на втором выходе не формируются. При обратном ходе (реверсе движения) наоборот уровни логической единицы на входах элемента 14 И не совпадают, совпадение происходит на входах элемента 15 И. На втором выходе формируются короткие счетные импульсы (четыре за один период входных сигналов).В режиме 1 делитель 7 частоты и триггер 8 удерживаются в исходном состоянии..хРежим 2 используется для определения работоспособности входных це- пей и дешифратора 4, а также блоков обработки цифровой информации, к входам которых подключаются первый и второй выходы преобразователя (на фиг.1 не показаны). В блоках обработки цифровой информации в качестве приемников унитарного кода С первого и второго выходов используются либо реверсивные счетчики, либо обычные накапливающие счетчики. В первом случае используется один реверсивный счетчик, информация в который поступает соответственно на вход суммирования и вход вычита . ния. С выхода счетчика снимается код величины переме-,ения. Во втором спучае информация о перемещении в прямом и обратном направлениях записывается в разные счетчики, при этом код величины перемещения получается путем вычитания кодов, записаных в соответствующие счетчики, Следовательно, существует два алгрритма формирования тестирующих импульсных последовательностей на первом и втором выходах преобразователя.В первом алгоритме после кода УК 1 (фиг,3), удерживающем преобразователь в исходном состоянии, в регистр 6 управления заносится УКЗ. При этом логические нули на первом, третьем, четвертом и пятом выходах настраивают блок 3 памяти на прием (со сдвигом) последовательного кода на пятый вход О, по передним фронтам синхроимпульсов на выходе элемента 9 И, запрещают выдавать информацию элемен-ту 15 И по Вых. 2, разрешают работуделителю 7 частоты и триггеру 8 соответственно. По задним фронтам (пере-,ход из уровня логической единицы куровню логического нуля) синхроимпуль-сов (фиг,З) ГИ информация на первомвыходе (с третьего разряда) делителя7 через каждые четыре периода изменяется на противоположную, а блок 3памяти периодически заполняется еди пницами и нулями (фиг. 3, А А В, 8,)при этом дешифратор 4 формирует наВых. 1(2 - 1) счетных импульсов, кото-,рые записываются в реверсивный счетчиксистемы обработки цифровой информации.После поступления И-го импульса(фиг.3,1) на вход старших разрядовделителя 7 частоты на его выходеФормируется импульс (Фиг, 31-), перебрасывающий триггер 8 (фиг. 36 ) в 2 Опротивоположное состояние, запрещающее поступление синхраимпульсов ГИчерез элемент 9 И на второй тактовыйвход Тблока 3 памяти, Процесс Формирования нормированного количества 2 с,импульсов прекращается.аАналогичным образом проверяетсядешифратор 4 и реверсивный счетчикобр. ботки цифровой информации приУКЙ, когда импульсы формируются наВых.2, а реверсивный счетчик работаетна вычитание, При коэффициенте деления М вычитается (211-1) импульсов.Во втором алгоритме в регистр 6управления заносится УК 5 и логичесЗс;кие единицы на втором и третьем выходах регистра 6 разрешают одновременноформировать на Вых. 1 и Вьи. 2 счетные импульсы в количестве (2 Й), чторегистрируют счетчики системы обработки цифровой информации.4 ОДля того, чтобы осуществить перебор всех возможных состояний счетчиков систем обработки цифровой информации, коэффициент деления М старших44резервов делителя 7 частоты выбирается равным: Н =(К+1(/2, где М - емкость счетчика, если К - нечетное число, и й = (К+1) /2+1, где (К+1) /2целая часть частного, если К -четноечисло. В первом случае Формируетсяколичество импульсов, равное емкости счетчика, во втором - на единицубольше,В результате контроля преобразова-теля повьшается достоверность его ра-боть 1. Частота счетных импульсов вчетырЕ раза меньше частоты синхраимпульсов ГИ, однако оца ца несколько порядков вьнце максимальна возможной частоты поступлеция сигналов на входах Вх.1 и Вх,2 в режиме 1.Формула изобретения1, Преобразователь синусаидальных сигналов перемещения в код, содержащий первый и второй пороговые формирователи, входы которых являются информационными входами преобразователя, а выходы подключены к первому и второму информационньпч входам блока памя - ти, первый и второй выходы которого подключены к первому и второму информационным входам дешифратара и к третьему и четвертому информационным вхацам блока памяти, третий и четвертый выходы блока памяти подключены к третьему и четвертому информациан - ным входам дешифратора, первый и второй выходы которого являются выходами преобразователя, генератор импульсов, выход которого подключен к первому синхронизирующему входу блока памяти, а т л и ч а ю щ и й с я тем, чта, с целью повышения достоверности преобразования, в него введены регистр управления, делитель частоты, триггер и элемент И, входы регистра управления являются управляющими входами преобразователя, первый выход регистра управления подключен к управляющему входу блока памяти, второй и третий выходы - к первому и второму управляющим входам дешифратара, четвертый выход - к входу сброса делителя частоты и к первому входу триггера, пятый выход - к входу сброса блока памяти, а группа выходов - к управляющим входам старших разрядов делителя частоты, выход генератора импульсов подключен к одному входу элемента И и к информационному входу делителя частоты, первый выход которбга подключен к пятому информационному входу блока памяти, а второй выход - к второму входу триггера, выход триггера подключен к другому входу элемента И, выход которого подключен к второму сицхронизирующему входу блока памяти,2. Преобразователь па и. 1, о т - л и ч а ю щ и й с я тем, что дешифратор содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй инвертары, первый и второй элементы И, первый и второй входы первого элемента ИСКЛЮЧАЮШЕЕ ИЛИ являются первым1234 Выходы регистра 6 управления УК Режим работы преобразователя группа 1-й2-й3-йа-и 1 5-й Установка в исходное состояние УК 1 О Режим 1 (+/-) УК 2 О Режим 2(+) О О О УКЗ О Режим 2(-) УК 4 О О Режим 2(+/-) УК 5 О,В таблице приняты следующие обоэначения: Х - произвольное состояние выхода; 1/О - высокое/низкое логическое состояние выхода; М - коэффициент деленияделителя 7 частоты; (+) - формирование импульсов только на первом выходе; (-) - формирование импульсов только на втором выходе; (+/-) - формирование импульсов на первом и втором выходах в зависимости от направления перемещения или режима тестирования. Обра 2222 айуй кИ Ребврс Пру 2 иой йой и четвертым информационными входак 1 ндещифратора, первьв и второй входывторого элемента ИСКЛЮЧАЮЩЕГ ИЛИявляются вторым н третьим информационными входами дешифраторау выходы первого и второго элементов 1 И;К 11 ЮЧАЮЩЕГИЛИ через первый и второй инверторысоответственно подключены к первым. 2 Я 8входам первого и второго элементов И, вторые входы которых соединены с выходами соответственно второго и первого элементов ИСК 1 ЮЧАПЦЕГ ИЛИ, третьи входыявляются первым и вторым управляющими входамидешифраторайа выходы первагои второго элементов Иявляются первыми вторым выходами дешифратора.

СмотретьЗаявка

3816867, 19.11.1984

ПРЕДПРИЯТИЕ ПЯ Г-4710

ВАСЫЛИВ ЯРОСЛАВ АЛЕКСЕЕВИЧ, КОВБАНЮК ИВАН ИВАНОВИЧ, КОРНИЕНКО ЮРИЙ ПЕТРОВИЧ, ЮРКИВ ИВАН ПРОКОПОВИЧ

МПК / Метки

МПК: H03M 1/30

Метки: код, перемещения, сигналов, синусоидальных

Опубликовано: 30.05.1986

Код ссылки

<a href="https://patents.su/6-1234968-preobrazovatel-sinusoidalnykh-signalov-peremeshheniya-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь синусоидальных сигналов перемещения в код</a>

Предыдущий патент: Преобразователь перемещения в код

Следующий патент: Преобразователь угла поворота вала в код

Случайный патент: Устройство для сообщения вращательного