Матричный вычислитель функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

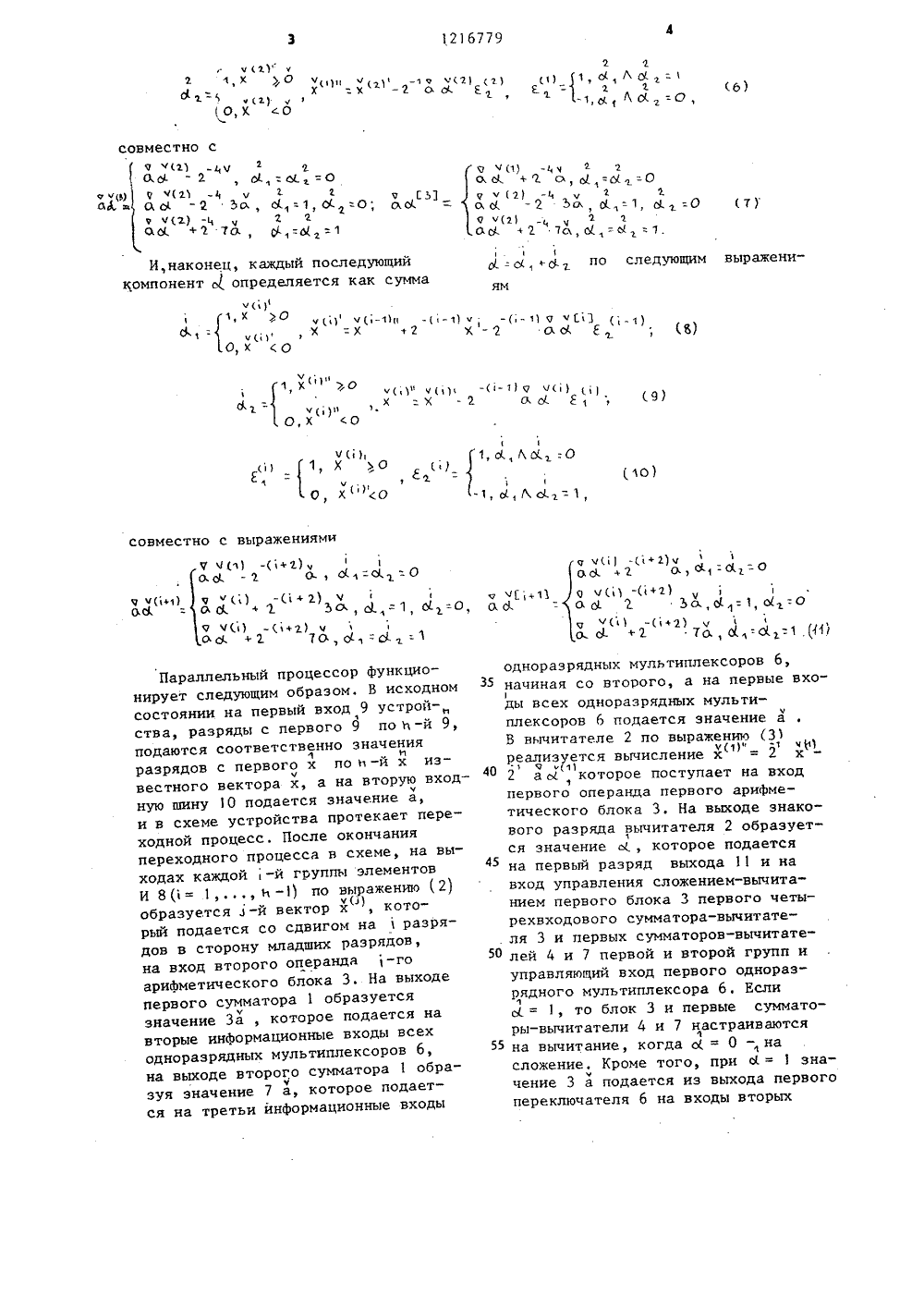

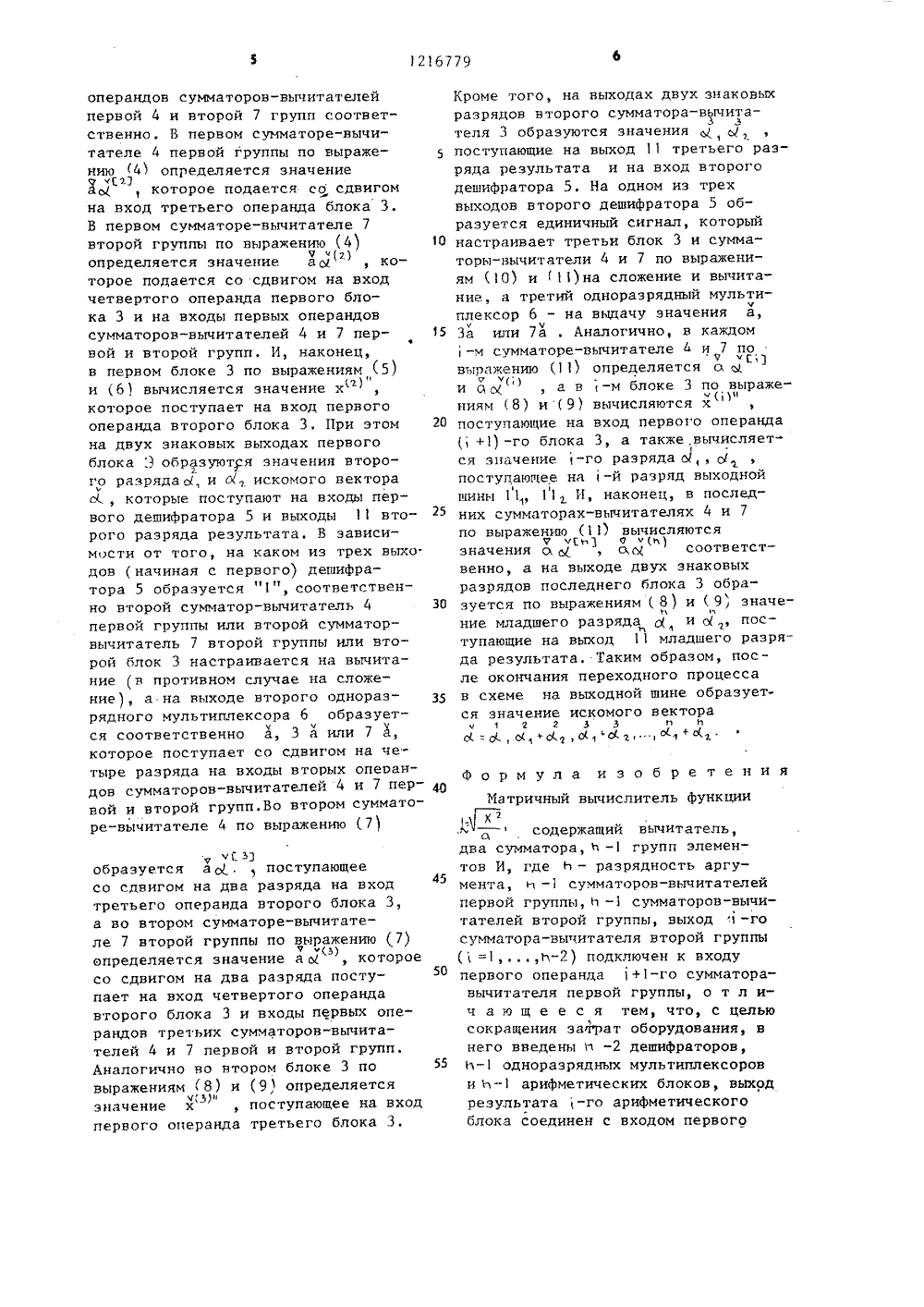

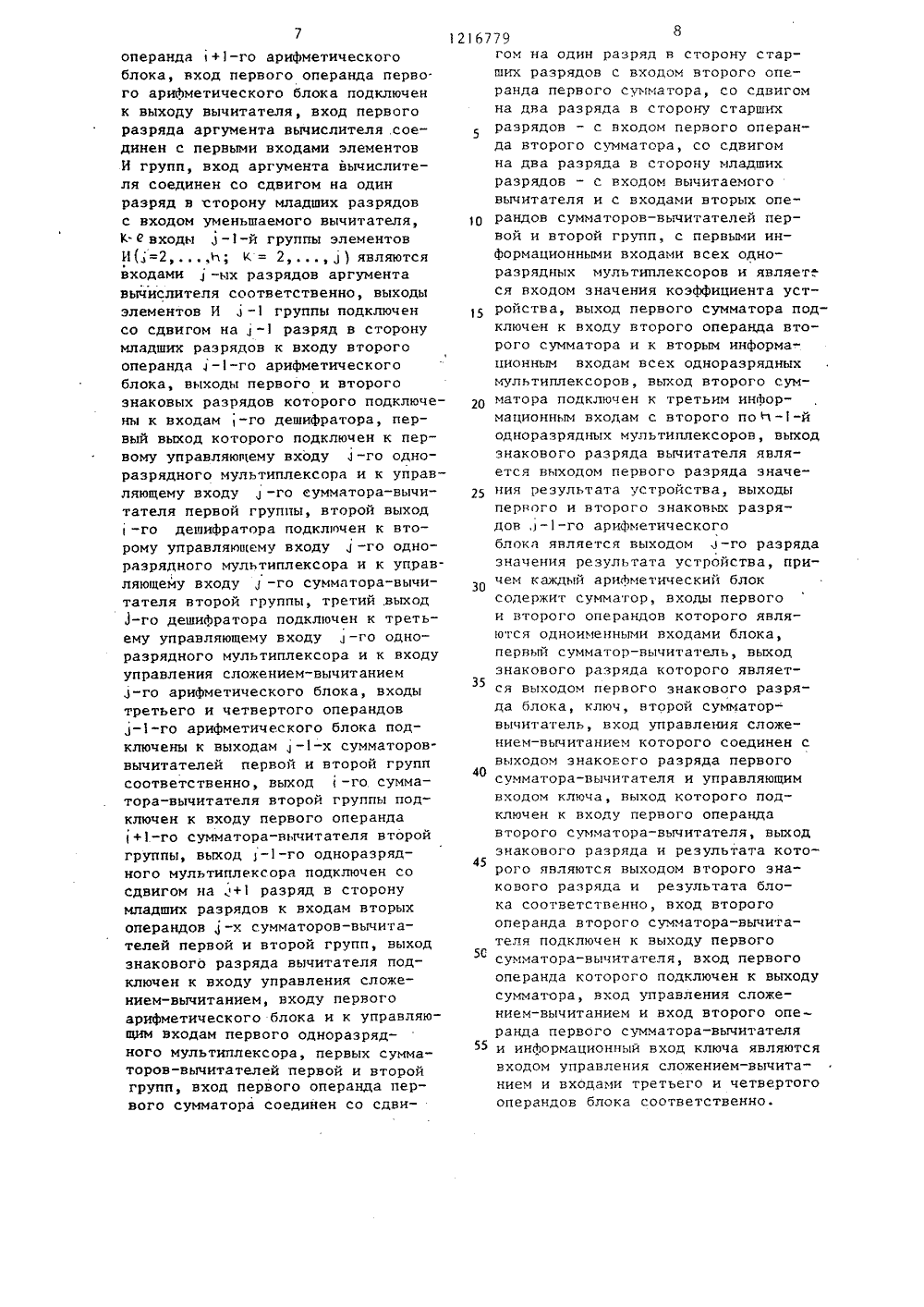

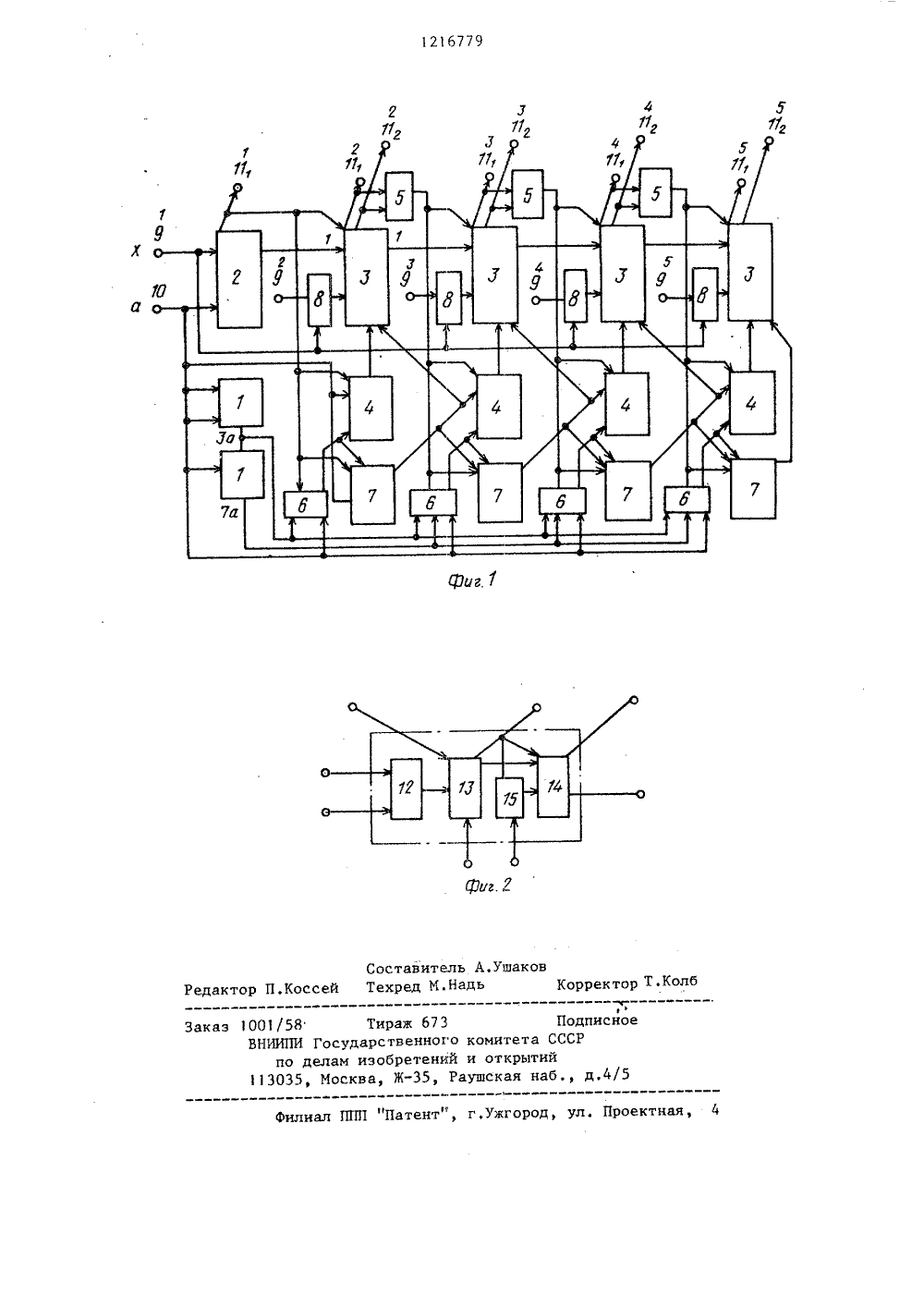

(21) (22) (46) (71) ИЧН 11 И В ю."СЛИТЕЛЬ ФУНК 57) Изо ительно етение отехнике носитс позвол вычт с в эне орден не ми осу- а льш ппаратур ычислени ми затрафункции тви ые оветс ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ОПИСАНИЕ ИЗОБР АВТОРСКОМУ СВИДЕТЕЛЬСТ 763143/24-249.06.847.03,86.Бюл. Р 9нститут проблем моделированигетике АН УССР и КиевскийТрудового Красного Знамениут инженеров гражданской ави(56) Пухов Г.Е., Евдокимов В.ФСиньков М.В. Разрядно-аналоговвычислительные системы. М.: Ское радио, 1978, с.254.Авторское свидетельство СССРУ 885998, кл.С 06 Р 7/552, 1980Стасюк А,И. Однородные многофункциональные матричные процесры. (Препринт АН УССР, Институтэлектродинамики, 9 351). Киев, 19с.13, рис.3. Ы - - Вычислительный процесс ввычислителе организован параллельно на комбинационных элементах, чтопозволяет обеспечить высокое быстродействие вычислителя, Вычислительсодержит вычитатель 2, два сумматора 1, 1 -1 арифметических блоков3, где Н - разрядность представления аргумента,-1 сумматоров-вычитателей первой 4 и второй 7 групп,Идешифраторов 5, п -1 одноразрядныхмультиплексоров 6, И -1 группу элементов И. Значения аргумента Х икоэффициента ц поступают на входы9 и 1 О вычислителя, Результат вычислений М образуется на выходах 11разрядов результата. 2 ил.Изобретение относится к вычислительной технике.и может бытьиспользовано автономно или в качестве специализированного процессора в составе многопроцессорныхвычислительных систем, предназначенных для реализации вычислительногопроцесса в натуральном масштабе времени.Пель изобретения - сокращениезатрат оборудования,На фиг,1 показана Функциональная схема предлагаемого устройства для случая, когда5; наФиг.2 - функциональная схема арифметического блока.Устройство (фиг.1) содержит двасумматора 1, вычитатель 2,(-1 -1)арифметических блоков 3,(1- - 1) сумматоров-вычитателей 4 первой группыУ(1 -2) дешифраторов 5, (-1) одноразрядных мультиплексоров 6, (1 -1)сумматоров-вычитателей 7 второйгруппы 3, -1) группу элементовИ 8, входы 9 и 10 разрядов аргумента и коэффициента устройства соответственно, выходы 11 разрядов результата устройства.Арифметический блок 3 (фиг.2)состоит из сумматора 12, первогои второго сумматоров-вычитателей13 и 14 соответственно и ключа 15,Работа устройства для вычисления зависимости вида)а =ф (1)осуществляется следующим образом.Представим выражениев разч ччч хрядной Форме Г 11 как х х - аао( =о,г 3 ггде. )(:х,х, ХХ; Ы:Ы,о(,о(;ч 1 г Э ьО=а,а, ОО- разрядныевекторы, представляющие собой разрядное иэображение чисел х,о1,соответственно;разрядные матрицы, представляющиесобой разрядное изображение х, ао) соответственно при ( = 4 ( - разрядность представления инФормации).5 Для организации вычислительногопроцесса неизвестного вектора о( запишем выражение (1) в развернутом виде при )1 = 4 как г 1 (1) 1 (2)Х + Х Х - а о(. - о- о(.э г (1) (1) 1 (3)Х х - О. О(. - О. О(. - о. с(.34 1(1) 3 (2) г (э) г(й)Х+ Х Х+Х Х -ас -ао(. - ао(- оо(г (1 й(1) 4 г Э(Ъ) г (4) 1(5)Х Х - с(о(. - а о(. - а с), - а с 4 - а о(,3 34 4(Ъ) 3 (Й) г (5)Х 1 Х Х - а с(. - О, о(. - О. о(.4 (4) 3 (5)(1) (2) (3) (ь)о(.о(., с(. о(.30определяемые как 3132331131 с(, = о(. Ы, сС б-, О,с(., о( = о(, с(, А о(., Ю.о(д. с(, О, с(,О,Представим компоненты Ы в виде разрядных векторов и запишем рекуреитные выражения для вычисления 40 первого разряда искомого вектора какЧ(1) Ч 1,Х ЭО ч(1 . Ч(1 -1 ч Ч(1) сг Ч -1 чХ:2 Х -2 оО(,с(о(: 2 оч(ч Ч ф 45 (з 1чо Ч Г -1 Ч ч(1) -3 ч о 1, Х ) О , ч(21 о (г)2 ас) + 2 )к,о(: 1 о ч1 ф ч1 . д чо -Зч40 45 50 55 операндов сумматоров-вычитателейпервой 4 и второй 7 групп соответственно. В первом сумматоре-вычитателе 4 первой группы по выражению (41 определяется значениер "(гаЫ , которое подается со сдвигомна вход третьего операнда блока 3.В первом сумиаторе-вычитателе 7второй группы по выражению (4)Ч цг)определяется значение ао( 1 , которое подается со сдвигом на входчетвертого операнда первого блока 3 и на входы первых операндовсумматоров-вычитателей 4 и 7 первой и второй групп. И, наконец,в первом блоке 3 по выражениям (5)и (6) вычисляется значение х(которое поступает на вход первогооперанда второго блока 3, При этомна двух знаковых выходах первогоблока Э образуются значения второгго разряда Ы и й искомого векторакоторые поступают на входы первого дешифратора 5 и выходы 11 второго разряда результата. В зависимости от того, на каком из трех выхо.дов (начиная с первого) дешифратора 5 образуется , соответственно второй сумматор-вычитатель 4первой группы или второй сумматорвычитатель 7 второй группы или второй блок 3 настраивается на вычитание (в противном случае на сложение), а на выходе второго одноразрядного мультиплексора 6 образуетч ч ся соответственно а, 3 а или 7 которое поступает со сдвигом на четыре разряда на входы вторых опеоандов сумматоров-вычитателей 4 и 7 первой и второй групп,Во втором сумматоре-вычитателе 4 по выражению (7) образуется ао,поступающее со сдвигом на два разряда на вход третьего операнда второго блока 3, а во втором суиматоре-вычитателе 7 второй группы по выражению (7)Ч м определяется значение а ь( , которое со сдвигом на два разряда поступает на вход четвертого операнда второго блока 3 и входы первых операндов третьих сумматоров-вычитателей 4 и 7 первой и второй групп. Аналогично во втором блоке 3 по выражениям (8) и (9, определяетсяЧ(З)значение х , поступающее на вход первого операнда третьего блока 3. 5 О 5 20 25 30 35 Кроме того, на выходах двух знаковых разрядов второго суиматора-вычитаз з теля 3 образуются значения , ь поступающие на выход 11 третьего разряда результата и на вход второго дешифратора 5, На одном из трех выходов второго дешифратора 5 образуется единичный сигнал, который настраивает третьи блок 3 и сумматоры-вычитатели 4 и 7 по выражениям (1 О) и 11)на сложение и вычитание, а третий одноразрядный мультич плексор 6 - на выдачу значения а, ч чЗа или 7 а . Аналогично, в каждом -и сумматоре-вычитателе 4 и 7 поЧ м; выражению (11) определяется о (о ч(;и о о(, а в -м блоке 3 по выраже (1 1 ц ниям ( 8) и ( 9 ) вычисляются х поступающие на вход первого операнда ( +1) -го блока 3, а также, вычисляется значение 1-го разряда М, о. поступающее на -й разряд выходной шины 11, 11 г И, наконец, в последних сумматорах-вычитателях 4 и 7 по выражению (11) вычисляютсяЧ чС 3 о (п 1значения о,, о с соответственно, а на выходе двух знаковых разрядов последнего блока 3 образуется по выражениям (8) и (9, значе 11 ние младшего разряда о( и с(поступающие на выход 11 младшего разряда результата. Таким образом, после окончания переходного процесса в схеме на выходной шине образуется значение искомого вектора1 г 2 3 3 г И с( = с(., о( + д. г, Ю 1 "О( г "о( (ъ Формула изобретенияМатричный вычислитель функции ,1 Гсодержащий вычитатель, два сумматора, Ь - 1 групп элементов И, где 6 - разрядность аргумента, н -1 сумматоров-вычитателей первой группы, П -1 сумматоров-вычитателей второй группы, выход 1 -го сумматора-вычитателя второй группы ( =1, ,ь) подключен к входу первого операнда +1-го сумматоравычитателя первой группы, о т л ич а ю щ е е с я тем, что, с цельюсокращения затрат оборудования, внего введены 1 и -2 дешифраторов, Иодноразрядных мультиплексорови Иарифметических блоков, выход результата -го арифметическогоблока соединен с входом первого/58 Тираж ИИПИ Государств делам иэобрМосква Ж673 нного комитета Стений и открытий35, Раушская наб акаэ 1 писно по 13035

СмотретьЗаявка

3763143, 29.06.1984

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР, КИЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ГУЛЯЕВ ВАСИЛИЙ АНАТОЛЬЕВИЧ, СТАСЮК АЛЕКСАНДР ИОНОВИЧ, ЛИСНИК ФЕДОР ЕРЕМЕЕВИЧ, ГУЗЕНКО АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычислитель, матричный, функции

Опубликовано: 07.03.1986

Код ссылки

<a href="https://patents.su/6-1216779-matrichnyjj-vychislitel-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Матричный вычислитель функции</a>

Предыдущий патент: Универсальный логический модуль

Следующий патент: Многофункциональный логический модуль с контролем

Случайный патент: Вентиляционное устройство