Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1193655

Автор: Керимов

Текст

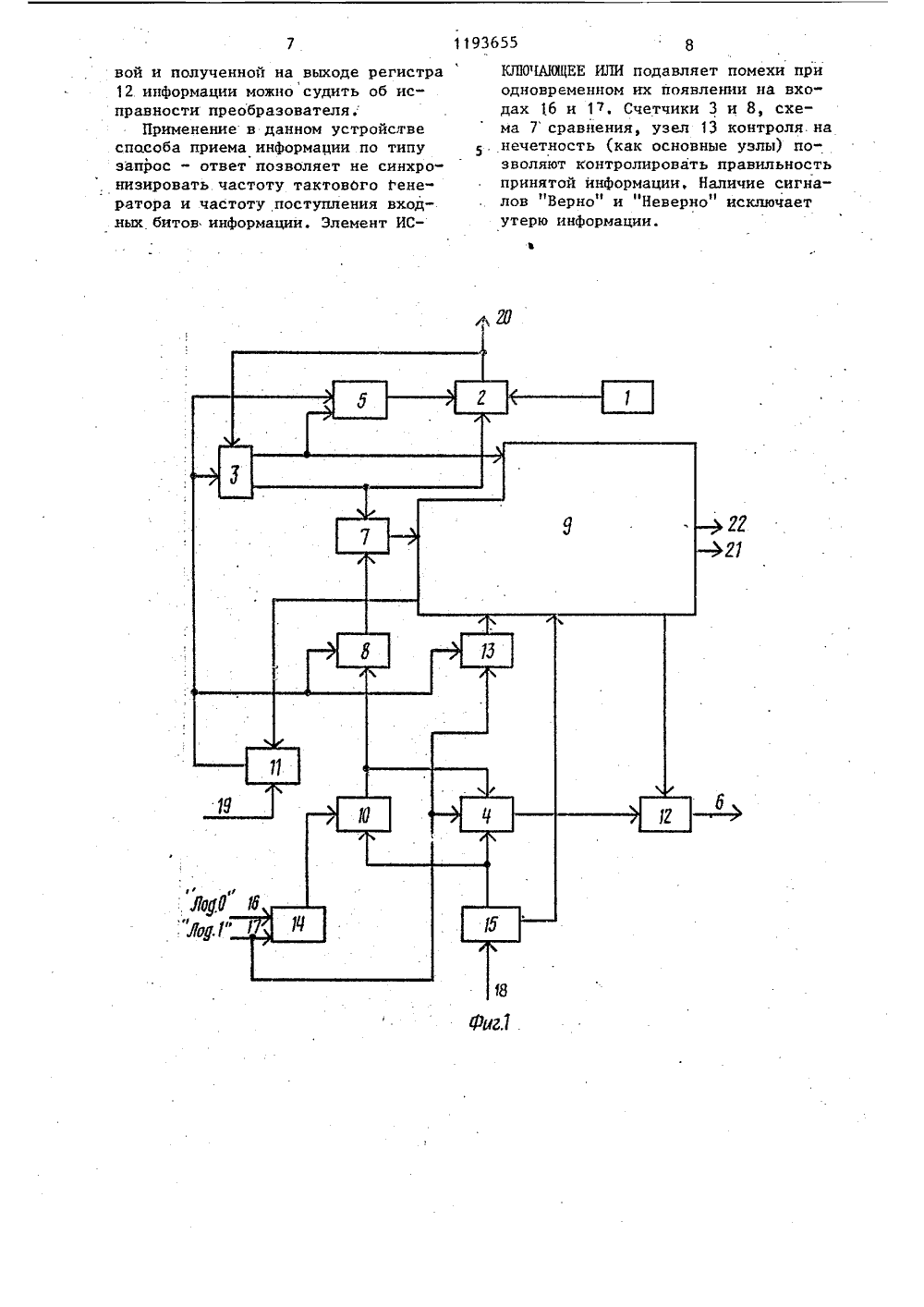

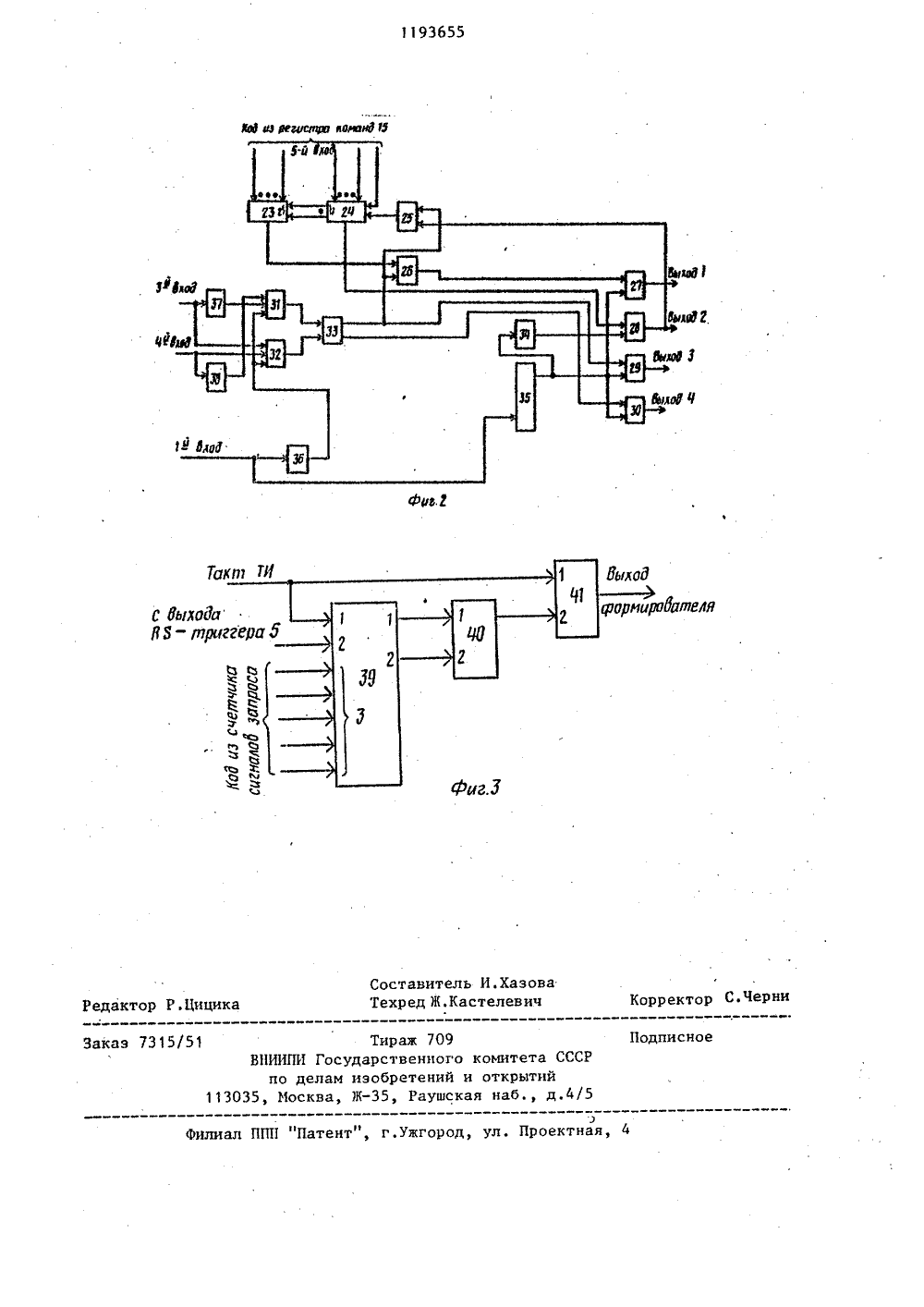

СОЮЗ С 08 ЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 9) 01 СО 0 ЕННЫЙ НОМИТЕТ СССР БРЕТЕНИЙ И ОТНРЫТИЙ ГОСУДАРСТ ПО ДЕЛАМ ОПИСАНИЕ ИЗОБРЕТЕНН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свицетельство СССР 9 822175, кл. С 06 Е 5/04,1979.Авторское свидетельство СССР И 1 760070, кл. С 06 Г 3/00,1978. (54) (57) 1.ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий генератор тактовых импульсов, регистр сдвига, выходной регистр, блок управления, регистр команды, причем информационный вход регистра сдвига соединен с первым информационным входом преобразователя, вход регистра команды является входом задания режима преобразователя, а первый выход соединен с первым входом блока управления, разрешающий выход которого соединен с управляющим входом выходного регистра, выход которого является информационным выходом преобразователя, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности работы, в него введены схема сравнения, первый и второй вычитающие счетчики, узел контроля на нечетность, два элемента ИЛИ, триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и формирователь сигнала запроса, причем первый и второй информационные входы преобразователя через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом регистра команды, а выход - со сдвиговыми входами регистра сдвига и счетным входом первого вычитающегосчетчика, вход сброса которого ивходы сброса триггера второго вычитающего счетчика и узла контроляна нечетность соединены с выходомвторого элемента ИЛИ, первый входкоторого соединен с выходом "Окончание слова" блока управления, а второй вход является входом запускапреобразователя, первый информационный вход которого соединен с информационным входом узла контропя нанечетность, выход которого соединенс вторым входом блока управления,третий вход которого соединен с выходом схемы сравнения, первый и второй входы которой соединены соответственно с выходом первого и первымвыходом второго вычитающих счетчиков, выход регистра команды соединен с управляющим входом регистрасдвига, выход которого соединен синформационным входом выходного регистра, выход генератора тактовыхимпульсов соединен с тактовым входом формирователя сигнала запроса,вход запуска и стробирующий вход которого соединены соответственно свыходом триггера и первым выходомвторого вычитающего счетчика, второй выход которого соединен с вторым входом триггера и четвертым входом блока управления, выход формирователя сигнала запроса соединен сосчетным входом второго вычитающегосчетчика и является выходом запросапреобразователя, третий и четвертыйвыходы блока управления являютсясоответственно выходами "Верно" и"Неверно" преобразователя, причемблок управления содержит коммутатор,1193 б 55 счетчик, восемь элементов И, дваэлемента НЕ, триггер и три элемента задержки, при этом информационные входы коммутатора и счетчика образуют первый вход блока, информационные выходы счетчика соединены суправляющими входами коммутатора,управляющий вход счетчика соединенс выходом первого элемента И, первый вход которого и первый вход второго элемента И соединены с первымвыходом триггера, выход коммутаторасоединен с вторым входом второгоэлемента И, выход которого соединенс первым входом третьего элемента И,выход которого является разрешающимвыходом. блока, выход счетчика соединен с первым входом четвертого элемента И, выход которого соединен свторым входом первого элемента И иявляется выходом "Окончание слова"блока, первые входы пятого и шестого элементов И соединены соответственно с первым и вторым выходамитриггера, первый и второй входы которого соединены соответственно свыходамп седьмого и восьмого элементов П, второй вход четвертого элемента И через первый элемент задержки соедгчен с выходом второго эле"Изобретение относится к вычислительной технике и автоматической передаче и преобразованию данных и может быть использовано в системах ввода ,инФормации в ЭВИ от источника информации, находящегося на расстоянии до 200 и.Целью изобретения является повышение достоверности работы.На фиг,1 показана схема преобразователя; на фиг.2 - схема блока управления; на фиг.3 - схема формирователя сигнала запроса.Преобразователь содержит генератор 1 тактовых импульсов, формирователь 2 си запроса, первый вычитающий счетчик 3, регистр 4 сдви-. га, триггер 5, информационный выход б, схему 7 сравнения, второй вычитающий счетчик 8, блок 9 управления, -элементы ИЛИ 10 и 11, выходной ремента задержки, соединенным с вторыми входами третьего, пятого и шестого элементов И, выходы пятого и шестого элементов И являются соответственно выходами "Верно" и "Неверно"блока, четвертый вход блока соединен с входом второго элемента задержки и через третий элемент задеряки - с первыми входами седьмого ивосьмого элементов И, второй и тре.тий входы восьмого элемента И соединены с вторым и третьим входамиблока, через первый и второй элементы НЕ соединенными с вторым и третьим входами седьмого элемента И,2, Преобразователь по п.1, о т -" л и ч а ю щ и й с я тем, что формирователь сигнала запроса содержит дешифратор, триггер и элемент И, при-. ,чем тактовый, запускающий и строби- рующий входы Формирователя соединенны с группой входов дешифратора, первый и второй выходы которого соединены с К - и Я - входами триггера, выход которого соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с тактовым входом и выходом Формирователя. гистр 12, узел 13 контроля на нечетпость, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14,регистр 15 команды, информационныевходы 1 б и 17, вход 18 команды, вход19 запуска, выход 20 запроса, выходы "Неверно" 21 и "Верно" 22.Блок управления содержит коммутатор 23, счетчик 24, элементы И 2532, триггер 33, элементы 34-36 за"держки, элементы НЕ 37 и 38.Формирователь сигнала запроса содержит дешифратор 39, триггер 40,элемент И 41.Генератор 1 тактовых импульсов .15 предназначен для выработки прямоугольных импульсов, Запуск формирователя 2 осуществляется подачей наего второй вход разрешающего сигнала с триггера 5 и при наличии на 20 третьих входах двоичного кода 10001При этом на первом выходе дешифратора 39 появляется импульс, уста 1навливающий триггер 40 в " 1 . Разрешается прохождение тактовых импульсов через элемент И 41 на выход формирователя 2 сигналов запроса.При появлении кода 00000 на входе дешифратора на его втором выходе появляется импульс, устанавливающий триггер 40 в "0". Прекращается выдача сигналов запроса. Первый, второй, третий выходы формирователя 2 являются первым, вторым, третьим входами дешифратора 39.Выход элемента И 41 является выходом формирователя 2 и.соединен с счетным входом счетчика 3.Счетчик 3 управляет работой Формирователя 2, отсчитывает количество выданных сигналов запроса и при обнулении вырабатывает стробирующий импульс.Перед каждым циклом в счетчике 3 по первому установленному входу записывается число 10001. Счетчик работает на вычитание.Регистр 4 сдвига предназначен для заполнения входной информацией. Выходы регистра 4 соединены с вторыми входами выходного регистра. Триггер :5 предназначен для выдачи разреша" ющего сигнала на формирователь 2 сигналов запроса при поступлении на его первый вход сигнала элемента ИЛИ 11.Схема 7 сравнения сравнивает коды, поступающие со счетчиков 3 и 8, при равенстве на его выходе "1".Счетчик 8 предназначен для подсчитывания количества информационных битов, поступающих на первые входы 17 и .16 устройства, т.е. сигналов "Лог,1" и "Лог.О", соответственно.Счетчик 8 работает на вычитание, предварительно по установочному вхо, ду в него записывается число 10001. Счетные выходы счетчика 8 соединены с вторыми входами схемы 7 сравнения.Блок 9 управления принимает код команды из регистра 15 команд и записывает в счетчик 24. В коде, за. писанном в счетчик, указывается количество информационных слов, которые необходимо принять от источника информации, в коде, поступающем на выходы комглутатора 23, указывается порядок перезаписи информации иэ регистра 12 сдвига, Изменяя свое со.ЗО 35 40 50 Узел 13 контроля на нечеткость проверяет принятый информационный код на нечетность. При правильной передаче и приеме в информационном коде всегда будет количество "1" нечетное, поэтому в данном устройстве в качестве схемы, реализующей функцию проверки на нечетность, может служить триггер со счетным входом и установкой в "0".Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14 предназначен для формирования тактовых сдвигающих импульсов, необходимых для продвижения информации в реги-стре 4 сдвига. Он исключает появление на выходе сигнала при одновременном появлении сигналов, т.е.помех, на двух ее входах.Регистр 15 команд служит для приема команды иэ ЭВМ, хранения ее и выдачи в блок 9 управления, а вавтономном режиме выдает тестовуюпрограмму проверки преобразователя,т.е. служит имитатором источника инФормации.Устройство работает следующим образом.В регистр 15 команд из памяти ЭВМ по входу 18 заносится команда ввода, в которой указывается порядок перестояние, счетчик 24 подключает один иэ входов коммутатора 23 на его выход. При обнулении счетчик 24 выда 1ет на свой второй выход сигнал 0 означающий конец приема информации, После приема 33-х импульсов схема 7 сравнения и узел 13 контроля на не. -1чет но сть выдают сигналы 1 и н а третий и второй входы блока 9 управ 0 ления , а счетчик 3 выдает стробирующий импульс на четв ертый вход . Элемент 3 б задержки увеличивает длите- . ность входного импульса . На входе :лемента И 3 2 появляется сигнал ,1 1 15 устанавливающий триггер 33 в 1При отсутствии сигналов от схемы 7 сравнения и (или) узла 13 контроля на нечеткость появляется сиг-.нал на выходе элемента И 31, уста навливающий триггер 33 в "0". Этосостояние означает неправильность приема информации. Выходы элементов И 27-30 являются выходами блока 9управлеггия,25 Выходной регистр 12 предназначендля приема информационных слов из регистра сдвига и хранения их в течение цикла приема одного информаггионного слова.11935дачи информации из регистра 4 сдвига,количество информационных слов и разрядов в слове и другие признаки. Взависимости от вида принимаемой информации ца первый вход блока 9 изрегистра 15 передаются соответствующие коды, Заполнение регистра 4 сдви. га пРоисходит полностью в каждом цикле. Заполнение выходного регистра 12может происходить не в каждом цик ОлеС небольшой задержкой относитель"цо команды ввода на вход 19 преоб"разователя поступает сигнал, который, проходя через элемент ИЛИ 11, 15записывает в счетчики 3 ц 8 число33, устанавливает в "0" узел 13 контроля, триггер 5 в "1". Получив разрешающий сигнал, формирователь 2 сиг.налов запроса выдает сигналы в цсточнцк цнформаццц. Счетчик 3, отсчитав33 импульса, обнуляется. При появлении нулевого кода на входе формирователя 2 прекращается выдача сигналов запроса, триггер 5 устанавливается в "О" импульсом с выходасчетчика 3. В ответ на каждый сигнал. запроса источник информации выдаетна входы 16 ц 17 преобразователяимпульса информационного кода "Лог. 301" илц "Лог.О" соответственно пер. вый импульс-контрольный бит,"Лог.1" или "Лог.О" информационного кода поступает на вход элемен" 35 та ИСКЛЮЧАЮЩЕЕ ИЛИ 14, который формирует тактовые сдвигающце импульсы. Этц импульсы через элемент ИЛИ10 поступают на вход регистра 4 сдвига ц счетчика 8. С входа 17 сиг нал "Лог,1" поступает на информационный вход ре 7"истра 4 сдвига ц узел 13 контроля на нечетность, происходит заполнение регистра 4, и определяется печетцость принятого кода. 45 Отсутствие сигнала на первом входе регистра 4 и наличие сдвигающего тактового импульса воспринимается как "Лог.О", Счетчик 8, отсчитав 33 импульса, обнуляется. Схема 7 срав ненця сравнивает коды счетчиков 3 и 8 ц прц равенстве на ее выходе "1", которая поступает на вход блока 9, счетчик 8 обнуляется несколько позже , Счетчика 3 за счет задержки распро странения сигналов в линии связи между преобразователем и источником ,информации. 655 ЬЭта задержка компенсируется за счет увеличения длительности импульса, поступающего с первого выхода счетчика 3 в блок 9 управления, Эту функцию выполняет элемент 36 задержкиС некоторой задержкой времени, определяемой элементом 35 задержки в зависимости от кода, пришедшего на первые входы элементов И 27 - 30, на их выходах появляются сигналы. Происходит запись информации в выходной регистр 12, выдается сигнал "Верно", а также в элемент ИЛИ 11, означающий конец цикла и начало нового. Источник информации, получив сигнал Верно подготавливает к передаче новое информационное слово. Цикл повторяется. Таким образом принимается весь массив информации.Если в линии связи появляются помехи, они поступают на входы 17 илц 16, и могут быть восприняты преобразователем как полезные сигналы, при этом счетчик 8 отсчитывает большое количество импульсов, схема 7 сравнения выдает "О" в блок управления, триггер 33 устанавливается в "О". Схема проверки ца нечетность может выдать сигнал "О", если код четный, триггер 33 также устанавливается в "О". Аналогичное произойдет, если в счетчик 8 поступит меньшее количество импульсов. Блок 9 управления выдает сигнал "Неверно" и сигнал об окончании цикла. Записи ниформации при этом не произойдет и поскольку на втором входе элемента И 25 запрещающий сигнал "О", то вычитание "1" из счетчика 24 не произойдет, При получении сигнала "Неверно" источник информации повторяет передачу неправильно принятого информационного слова. Информация в выходном регистре 12 может храниться в течение времени заполнения регистра 4 сдвига. Емкость регистров 4 и 12 4-х байтная, выбрана из условийбыстродействия ЭВМ и времени приФ ема всего массива информации. Из этих же условий выбирается частота генератора 1.В автономном режиме информация с второго входа регистра 15 команд поступает на вход регистра 4 сдвига. Заполнение тестовой информацией регистров 4 и 12 происходит так же, как и от истоника информации. Путем программного сравнения тесто1193655 гг г вой и полученной на выходе регистра 12 информации можно судить об исправности преобразователя;Применение в данном устройстве спасоба приема информации по типу запрос - ответ позволяет не синхронизировать частоту тактового Генератора и частоту поступления входных битов информации. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ подавляет помехи при одновременном их появлении на входах 16 и 17. Счетчики 3 и 8, схема 7 сравйения, узел 13 контроля на . нечетность (как основные узлы) позволяют контролировать правильность принятой информации, Наличие сигналов "Верно" и "Неверно" исключает утерю информации.%тел С йгхода ЯЗ- пж Составитель И.ХазоваТехред Ж.Кастелевич орректор С. Черни актор Р.Цицик Подписное Заказ 73 15/51 Тираж 709ВПИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, )К, Раушская наб., д,4/5 лиал ППП "Патент",ая, 4 ород, ул.

СмотретьЗаявка

3738247, 08.05.1984

ПРЕДПРИЯТИЕ ПЯ А-3462

КЕРИМОВ АДИЛ ЭНВЕРОВИЧ

МПК / Метки

МПК: G06F 3/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.11.1985

Код ссылки

<a href="https://patents.su/6-1193655-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для синхронизации многоканальной измерительной системы

Следующий патент: Устройство для ввода информации

Случайный патент: Ограничитель канатного вращающегося блока