Устройство для логарифмирования отношения сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1112375

Авторы: Болванов, Каргальцев, Купер

Текст

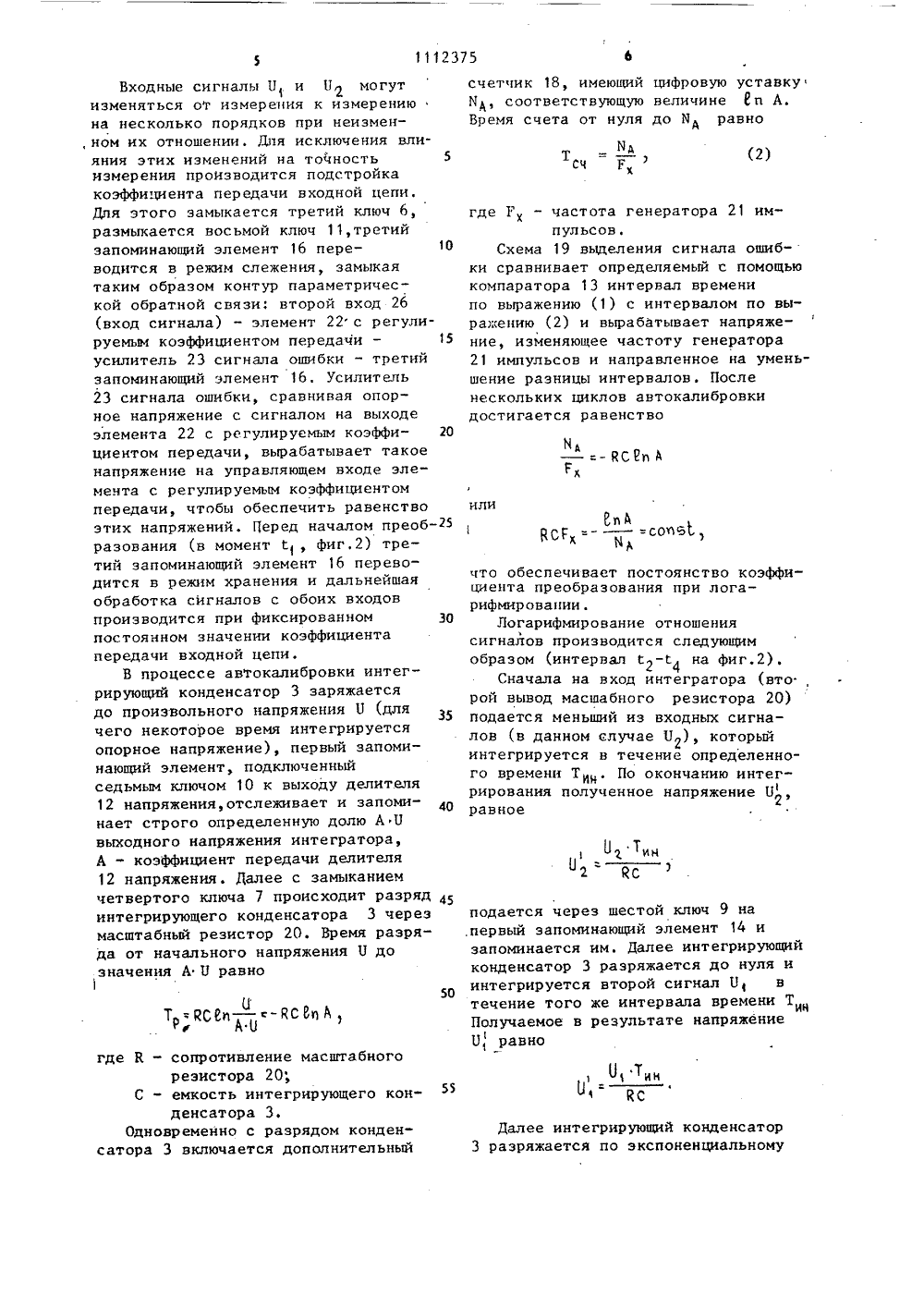

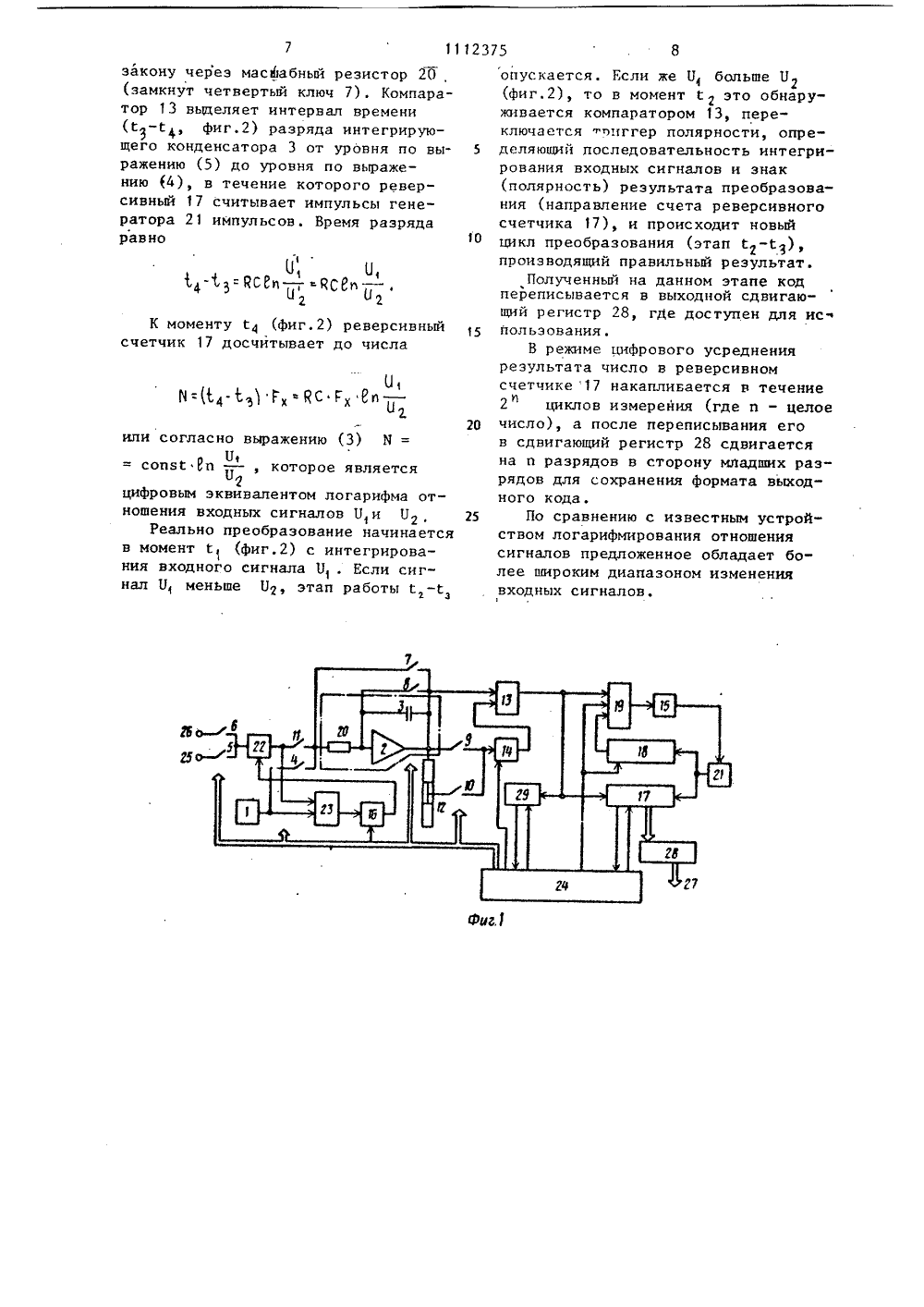

7 А СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 09)ЯОН 1 1 1 3 С 51) С 06 С 7/24 С 06 12 ОПИСАНИЕ ИЗОБРЕТЕНИЯ сА ЪЬ Ъ ТТ ЖМУСЬ а К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(7 1) Специальное конструкторско- технологическое бюро специальной электроники и аналитического приборостроения Сибирского отделения АН СССР и Институт ядерной физики Сибирского отделения АН СССР(54)(57) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ ОТНОШЕНИЯ СИГНАЛОВ, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к чыходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик, блок синхронизации, первый выход которого подключен к управляющему входу первого ключа, о т.л и ч а ю щ ее с я тем, что, с целью расширения динамического диапазона изменения входных сигналов, в него введены второй, третий, четвертый, пятый, шЕстой, седьмой и восьмой ключи,первый, второй и третий запоминающие элементы, дополнительный счетчик, делитель напряжения, схема выделения сигнала ошибки, усилитель сигнала ошибки, сдвигающий регистр, триггер знака и элемент с регулируемым коэффициентом передачи,причем первые выводы второго и третьего ключей подключены к входу элемента с регулируемым коэффициентом передачи, вторые выводы второго и третьего ключей являются соответственно первым и вторым входами устройства, второй вывод масштабного резистора соединен с первым выводом четвертого ключа, второй вывод которого под-ключен к выходу операционного усилителя, между инвертирующим входом и выходом операционного усилителя включен пятый ключ, к выходу опера-. ционного усилителя подключены вход йС делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения подключен первый вывод седьмого ключа, вторые выводы шестого и седьмого ключей подключены к входу первого запоминающего элемента, выход которого соединен с вторым входом компаратора, выход элемента с регулируемым коэффициентом передачи через восьмой ключ соединен с вторым выводом масштабного резистора, выход элемента с регулируемым коэффициентом передачи подключен к ф первому входу усилителя сигнала ошибки, второй вход которого подключен к выходу источника опорного напряжения, выход компаратора соединен с первым входом схемы выделения сигнала ошибки, с первым входом триггера знака и с управляющимвходом реверсивного счетчика, выходсхемы вьщеления сигнала ошибки черевторой запоминающий элемент подключен к управляющему входу генератораимпульсов, выход которого соединенс тактовыми входами реверсивногосчетчика и дополнительного счетчика,выход дополнительного счетчика подключен к второму входу схемы выделения сигнала ошибки, третий вход которой соединен с управляющим входом дополнительного счетчика и с соответствующим выходом блока синхронизации,выход усилителя сигнала ошибки черезтретий запоминающий элемент подключен к управляющему входу элемента 2375с регулируемым коэффициентом передачи, управляющие входы ключей,первого и третьего запоминающих элементов соединены с соответствующими выходами блока синхронизации, второй вход триггера знака и дополнительный управляющий вход реверсивного счетчика подключены к соответствующим выходам блока синхронизации, выход триггера знака и один из выходов реверсивного счетчика подключены к соответствующим входам блока синхронизации, выходы реверсивного счетчика подключены к входам сдвигающего регистра, выходы которого являются цифровым выходом устройства, Изобретение относится к устройствам преобразования отношения сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах. 5Известно устройство для логарифмирования отношения сигналов, содержащее генераторы экспоненциальных напряжений, компаратор, запоми-нающее устройство, счетчик, генератор импульсов и блок управления 1,Однако устройство имеет низкую помехозащищенность, малый диапазон изменения входных сигналов и низкую точность работы. 15 Наиболее близким к предложенному является устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между ин" вертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод первого масштабного резистора, второй вывод которого соединен с выходом ключа, вход которого подключен к выходу источника напряжения, выход операционного усилителя подключен к входу компаратора, выход которого подключен к входу генератора импульсов, выход которого соединен через второй масштабный резистор с инвертирующнм входом операционного усилителя, выход блока синхронизации подключен к управляющему входу ключа ,и к первому входу элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И подключен к входу счетчика, выходы ко. торого являются цифровым выходом устройства, второй вход компаратора подключен к выходу источника опорного напряжения 121.Однако известное устройство характеризуется низкой помехоэащищенностью, имеет малый диапазон отношения сигналов н обладает низкой точностью работы.Целью изобретения является расширение динамического диапазона изменения входных сигналов.Поставленная цель достигается тем, что устройство для логарифмирования отношения сигналов, содержащее операционный усилитель, между инвертирующим входом и выходом которого включен интегрирующий конденсатор, к инвертирующему входу операционного усилителя подключен первый вывод масштабного резистора, второй вывод которого через первый ключ подключен к выходу источника опорного напряжения, выход операционного усилителя подключен к первому входу компаратора, генератор импульсов, реверсивный счетчик блок синхронизации,первый выход которого подключен к управляющему входу первого ключа, введенывторой, третий, четвертый, пятый, шестой, седьмой и восьмой ключи,первый, второй и третий запоминающие эле. менты, дополнительный счетчик, дели.тель напряжения, схема вьделения 5 сигнала ошибки, усилитель сигнала ошибки, сдвигающий регистр, триггер знака и элемент с регулируемым коэффициентом передачи, причем перВые выводы второго и третьего ключей 10 подключены к входу элемента с регули руемым коэффициентом передачи, вторые выводы второго и третьего ключей являются соответственно первым и 1вторым входами устройства, второй 15 вывод масштабного резистора соединен с первым выводом четвертого ключа, второй вывод которого подключен к выходу операционного усилителя, между инвертирующим входом и выхо дом операционного усилителя включен пятый ключ, к выходу операционного усилителя подключены вход делителя напряжения и первый вывод шестого ключа, к выходу делителя напряжения 25 подключен первый вывод седьмогоключа, вторые выводы шестого и седьмого ключей подключены к входу первого запоминающего элемента, выход которого соединен с вторым вхо- З 0 дом компаратора, выход элемента с регулируемым коэффициентом передачи через восьмой ключ соединен с вторым выводом масштабного резистора, выход элемента с регулируемым коэф фициентом передачи подключен к первому входу усилитепя сигнала ошибки, второй вход которого подключен к выходу источника опорного напряжения, выход компаратора соединен с 40 первым входом схемы вьделения сигнала ошибки, с первым входом триггера знака и с управляющим входом реверсивного счетчика, выход схемы вьделения сигнала ошибки через второй за поминающий элемент подключен к управляющему входу генератора импульсов, выход которого соединен с тактовыми входами реверсивного счетчика и дополнительного счетчика, выход 50 дополнительного счетчика подключен к второму входу схемы вьделения сигнала ошибки, третий вход которой соединен с управляющчм входом дополнительного счетчика и с соот ветствующим выходом блока синхронизации, выход усилителя сигнала ошибки через третий запоминающий элемент подключен к управляющему входу элемента с регулируемым коэФФициентом передачи управляющие входы ключей, первого и тр .тьего запоминающих элементов соединены с соответствующими выходами блока синхронизации, второй вход триггера знака и дополнит".льный управляющий вход реверсивного счетчика подключены к соответствующим выходам блока синхронизации, выход триггера знака и один из выходов реверсивного счетчика подключены к соответствующим входам блока синхронизации,выходы реверсивного счетчика подключены к входам сдвигающего регистра, выходы которого являются цифровым выходом устройства.На фиг.1 изображена функциональная схема устройства для логарифмирования отношения сигналов, на фиг. 2 - временные диаграммы сигналов.Устройство содержит источник 1 опорного напряжения, операционный усилитель 2, интегрирующий конденсатор 3, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой ключи 4-11, делитель 12 напряжения, компаратор 13, первый, второй и третий запоминающие элементы 14-16, реверсивный счетчик 17, дополнительный счетчик 18, схему 19 выделения сигнала ошибки, масштабный резистор 20, генератор21 импульсов, элемент 22 с регулируемым коэффициентом передачи,усилитель 23 сигнала ошибки, блок 24 синхронизации, первый и второй входы 25 и 26, выход 27 сдвигающий регистр 28 и триггер 29 знака.На фиг.2 изображены временные диаграммы сигналов: а - на втором выводе масштабного резистора 20, Б - на выходе операционного усилителя 2; Ь - на выходе первого запоминающего элемента 14, 7 - на выходе компаратора 13,- на выходе триггера 29 знака, а также диаграмма 6 состояния реверсивного счетчика 17. Устройство работает следующим образом.До момента(фиг.2) осуществляются одновременно два процесса автокалибровка логарифмирующего преобразователя и автоподстройка коэффициента передачи входной цепи.(2) йд =- ЙСРп Дк ЮпА СГ =- - =соей,хВходные сигналы Ц и 02 могут изменяться от измерения к измерению на несколько порядков при неизмен, ном их отношении, Для исключения влияния этих изменений на точность 5 измерения производится подстройка коэффициента передачи входной цепи.Для этого замыкается третий ключ 6, размыкается восьмой ключ 11,третий запоминающий элемент 16 пере О водится в режим слежения, замыкая таким образом контур параметрической обратной связи: второй вход 26 (вход сигнала) - элемент 22 с регулируемым коэффициентом передачи - 15 усилитель 23 сигнала ошибки - третий запоминающий элемент 16. Усилитель 23 сигнала ошибки, сравнивая опорное напряжение с сигналом на выходе элемента 22 с регулируемым коэффи циентом передачи, вырабатывает такое напряжение на управляющем входе элемента с регулируемым коэффициентом передачи, чтобы обеспечить равенство этих напряжений. Перед началом преобразования (в момент 1, фиг.2) третий запоминающий элемент 16 переводится в режим хранения и дальнейшая обработка сигналов с обоих входов производится при фиксированном ЗО постоянном значении коэффициента передачи входной цепи.В процессе автокалибровки интег- рирующюЯ конденсатор 3 заряжается до произвольного напряжения П (для чего некоторое время интегрируется опорное напряжение), первый запоминающий элемент, подключенныйседьмым ключом 10 к выходу делителя 12 напряжения, отслеживает и запоми нает строго определенную долю А Б выходного напряжения интегратора, А - коэффициент передачи делителя 12 напряжения . Далее с замыканием четвертого ключа 7 происходит разряд 45 интегрирующего конденсатора 3 через масштабный резистор 20. Время разряда от начального напряжения П до значения А П равно50 где К - сопротивление масштабногорезистора 20,С - емкость интегрирующего кон 55денсатора 3,Одновременно с разрядом конденсатора 3 включается дополнительный счетчик 18, имеющий цифровую уставкуМд, соответствующую величине п А,Время счета от нуля до Ид равно где Г - частота генератора 21 имхпульсов.Схема 19 выделения сигнала ошибки сравнивает определяемый с помощью компаратора 13 интервал времени по выражению (1) с интервалом по выражению (2) и вырабатывает напряжение, изменяющее частоту генератора 21 импульсов и направленное на уменьшение разницы интерваловПосле нескольких циклов автокалибровки достигается равенство что обеспечивает постоянство коэффидлента преобразования при логарифмировании.Логарифмирование отношения1сигналов производится следующим образом (интервал 2-4 на фиг.2).Сначала на вход интегратора (вто., рой вывод масшабного резистора 20) подается меньший из входных сигналов (в данном случае 11 ), который интегрируется в течение определенного времени Ти. По окончанию интегрирования полученное напряжение Б равное подается через шестой ключ 9 напервый запоминающий элемент 14 изапоминается им. Далее интегрирующийконденсатор 3 разряжается до нуля иинтегрируется второй сигнал 1) втечение того же интервала времени ТПолучаемое в результате напряжениеП, равно Далее интегрирующий конденсатор3 разряжается по экспоненциальномузакону через масйабный резистор 20, (замкнут четвертый ключ 7). Компаратор 13 выделяет интервал времени (-С, фиг.2) разряда интегрирующего конденсатора 3 от уровня по выражению (5) до уровня по выражению (4), в течение которого реверсивный 17 считывает импульсы генератора 21 импульсов, Время разряда равноК моменту 4 (фиг,2) реверсивныйсчетчик 17 досчитывает до числаО1 =И 4-31 х сГ 16 ОЬили согласно выражению (3) И =Ьсопят п - , которое являетсяП 9цифровым эквивалентом логарифма отношения входных сигналов 01 иРеально преобразование начинается в момент 1 (фиг.2) с интегрирования входного сигнала Б . Если сиг 1нал Б меньше 02, этап работыопускается. Если же 01 больше У 2(фиг,2), то в момент с 2 это обнаруживается компаратором 13, переключается щтгер полярности, опре 5 деляющий последовательность интегрирования входных сигналов и знак(полярность) результата преобразования (направление счета реверсивногосчетчика 17), и происходит новыйцикл преобразования (этап С 2-1),производящий правильный результат.Полученный на данном этапе кодпереписывается в выходной сдвигающий регистр 28, где доступен для ис15 пользования,В режиме цифрового усреднениярезультата число в реверсивномсчетчике 17 накапливается в течение2 " циклов измерения (где и - целое20 число), а после переписывания егов сдвигающий регистр 28 сдвигаетсяна и разрядов в сторону мйадших разрядов для сохранения формата выходного кода.25 По сравнению с известным устройством логарифмирования отношениясигналов предложенное обладает более широким диапазоном изменениявходных сигналов.1112375 Составитель О. ОтрадновО. Юрковецкая Техред А,Ач Корректор В, Бутя аказ 6460 Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 Тираж 698 ВНИИПИ Государственного по делам изобретений 13035, Москва, Ж, Раушс

СмотретьЗаявка

3405042, 03.03.1982

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО СПЕЦИАЛЬНОЙ ЭЛЕКТРОНИКИ И АНАЛИТИЧЕСКОГО ПРИБОРОСТРОЕНИЯ СО АН СССР, ИНСТИТУТ ЯДЕРНОЙ ФИЗИКИ СО АН СССР

БОЛВАНОВ ЮРИЙ АНДРЕЕВИЧ, КАРГАЛЬЦЕВ ВИКТОР ВИКТОРОВИЧ, КУПЕР ЭДУАРД АДОЛЬФОВИЧ

МПК / Метки

МПК: G06G 7/24

Метки: логарифмирования, отношения, сигналов

Опубликовано: 07.09.1984

Код ссылки

<a href="https://patents.su/6-1112375-ustrojjstvo-dlya-logarifmirovaniya-otnosheniya-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логарифмирования отношения сигналов</a>

Предыдущий патент: Устройство для логарифмирования отношения сигналов

Следующий патент: Устройство для определения математического ожидания

Случайный патент: Устройство для индикации