Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

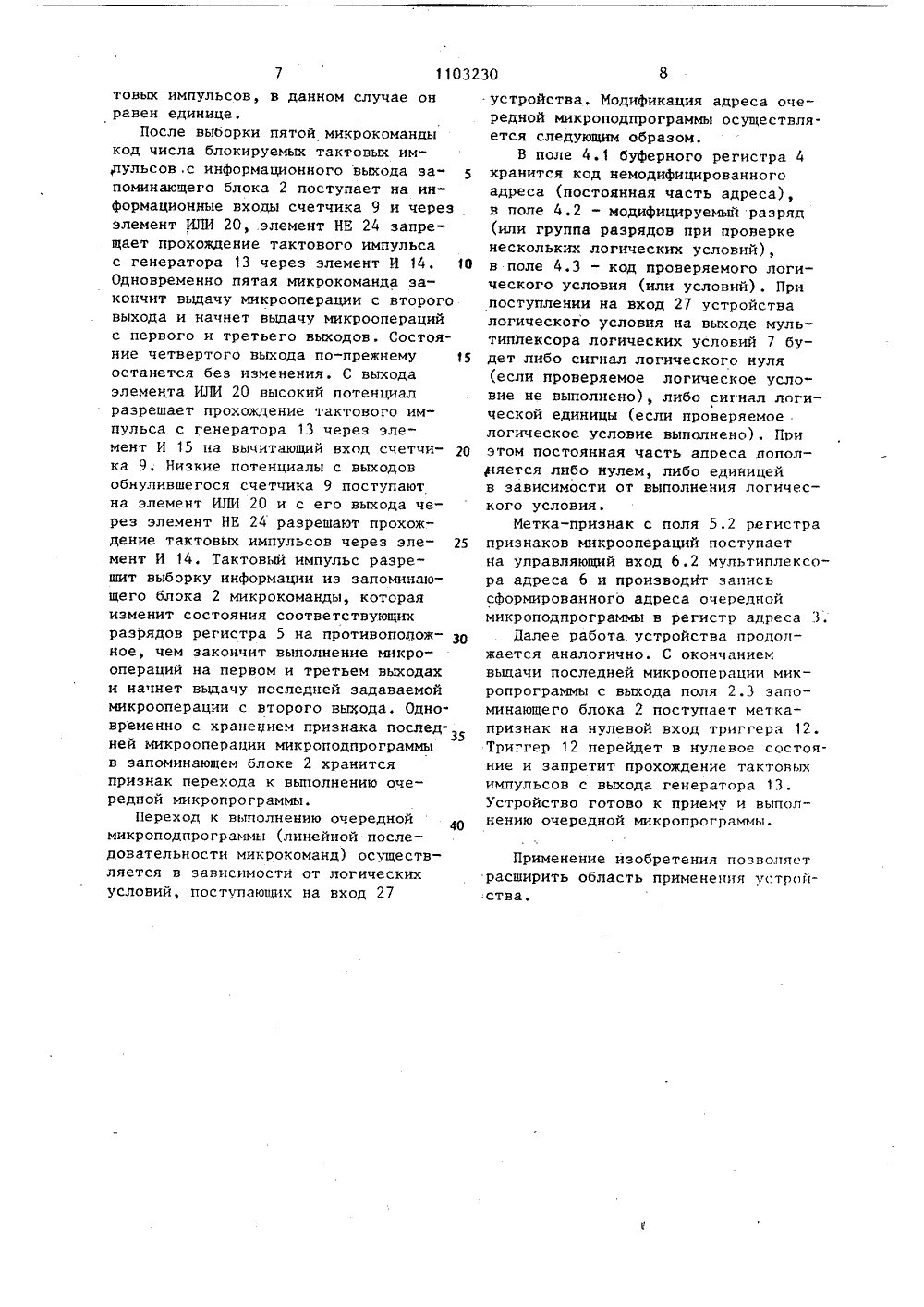

(19) ИИ А 6 Е 922 ГОСУДАРСТВЕ ПЮДЕЛАМ ИЭ АНИЕ ИЗОБРЕТЕНИ 4)(57) МИКРОПРО РАВЛЕНИЯ, содер й запоминающие реса, буферный изнаков микрооп са, счетчик, пе й элементы ИЛИ, пульсов, первый твертый элемент РМЯНОЕ УСТРОЙСТВО ащее первый и втолоки, регистр егистр, регистр раций, счетчик адвый, второй, трегенератор тактовых второй, третий, И, элемент НЕ игг единичныи выхсоединен с вхо тор огоодновибригге и нен с входомержки, выход пе выход которого со первого элемента вого элемента зад левым входом втор вой вход которого входом четвертого четвертого элемен жки соединен с ну го триггера, нуле- соединен с.первым элемента И, выхоц а И соединен с вхота задержки, выход со счетным входом дом второго элеменкоторого соединенсчетчика адреса, вреса соединен с вт ход счетчика ад Орым входом реши ЫЙ КОМИТЕТ СССР ОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1. Авторское свидетельство СССРНф 96464 1, кл.С 06 Р 9/22, 1982.2. Авторское свидетельство СССРР 945866, кл. Е. 06 Р 9/22, 1982(прототип). льтиплексор логических условии причем выход регистра адреса соединенс первым входом дешифратора адреса,выход которого соединен с входомпервого запоминающего блока, выходпервого запоминающего блока соединенс информационным входом буферногорегистра, выход генератора тактовыхимпульсов соединен с первыми входами первого и второго элементов И,единичные выходы счетчика соединеныс входами первого элемента ИЛИ, выходвторого элемента И соединен с вычитающим входом счетчика, выход нуляпроверяемых логических условий буферного регистра соединен с первым информационным входом мультиплексоралогических условий, о т л и ч а ю -щ е е с я тем, что, с целью расширения области применения за счет формирования микроопераций произвольнойдлительности, устройство дополнительно содержит мультиплексор адреса,два триггера, одновибратор, два элемента задержки, причем кодовый входустройства соединен с первым информационным входом мультиплексора адреса, выход которого соединен с информационным входом регистра адреса,вход запуска устройства соединенс первым управляющим входом мультиплексора адреса, с единичным входомпервого триггера и первым входом второго элемента ИЛИ, выход которогосоединен с единичным входом второго ратора, выход которого соединен с первым входом третьего элемента И, выход которого соединен с входами установки в нуль буферного регистра и регистра признаков микроопераций, выход старшего. разряда которого соединен с вторым входом третьего элемента ИЛИ и вторым управляющим входом мультиплексора адреса, выход первого элемента ИЛИ соединен с входом элемента НЕ, выход которого соединен с вторым входом третьего элемента И и вторым входом первого элемента И,1103230 фратора адреса, выход которого соединен с входом второго запоминающегоблока, первый информационный выходзапоминающего блока соединен с входами регистра признаков микроопераций,второй информационный выход второгозапоминающего блока соединен с информационным входом счетчика, управляющий выход второго запоминающего блокасоединен с нулевым входом первоготриггера, единичный выход которогосоединен с третьим входом первогоэлемента И, выход немодифицируемогокода адреса буферного регистра соединен с вторым информационным входоммультиплексора адреса, выход третьегоэлемента ИЛИ соединен также с вторым Изобретение относится к вычислительной технике и может быть исполь -зовано в качестве управляемого устройства с программируемой логикой в ЭВМ общего и специапьного назначения, а также АСУ технологическими процессами.Известно микропрограммное устройство управления, содержащее память микропрограмм, регистр адреса, дешифратор, регистр микрокоманд, генератор тактовых импульсов, блок формиро. вания синхроимпульсов, счетчик, формирователь импульсов, логические элемента И, И-НЕ 111 .сНедостатком устройства является ограниченная область применения: невозможна выдача микроопераций произвольной длительности,Наиболее близким к предложенному по технической сущности и достигаемому положительному эффекту является микропрограммное устройство управления, содержащее последовательно соединенные первый регистр адреса, первый дешифратор, первый блок памяти, второй регистр адреса и первый блок элементов И, второй вход которо. го является входом логических условий устройства, а выход соединен с входом первого регистра адреса, генератор тактовых импульсов,элемент ИЛИ, счетчик, выход которого 5 1 О 15 20 25 ЗО информационным входом мультиплексораадреса, выход регистра признаков микроопераций является выходом устройства, вход логических условий устройва соединен с вторым информационнымвходом мультиплексора логических условий, выход которого соединен с первым входом третьего элемента ИЛИ,второй вход которого соединен с выходом модифицируемого разряда буферного регистра, второй вход и выходчетвертого элемента И соединены соответственно с выходом первого элемента И и с тактовым входом дешифратораадреса, выход первого элемента ИЛИсоединен с вторым входом второгоэлемента И. соединен с входом дешифратора, второй, третий и четвертый блоки памяти, второй, третий и четвертый дешифраторы, третий и четвертый регистрыадреса, группу счетчиков, узел коммутации моментов начала микроопераций, группу блоков элементов И, первый, второй и третий элементы И,группу элементов ИЛИ, элемент НЕ,причем первый выход генератора тактовых импульсов подключен к первомувходу первого элемента И, второйвход которого подключен через элемент НЕ к выходу элемента ИЛИ ик первому входу второго элемента И,выход первого элемента И соединенс управляющими входами первого, второго, третьего, четвертого дешифраторов, информационные входы второго,третьего, четвертого дешифраторов .соединены соответственно с вторым,третьим, четвертым выходами первогорегистра адреса, а выходы черезвторой, четвертый блоки питания - спервым выходом устройства, входамитретьего и четвертого регистров адреса соответственно, выходы разрядов, кроме последнего третьего регистра адреса, соединены с первымивходами узла коммутации моментовначала микроопераций, вторые входыкоторого соединены с выходами дешифратора импульсов, а выходы узла коммутации соединены с первыми входами группы блоков элементов И, вторые входы которых соединены с выходами четвертого регистра адреса, а выходы - с информационными входами группы счетчиков, нулевые выходы которых через группу элементов ИЛИ подключены к второму выходу устройства и к выходам элемента ИЛИ, второй выход генератора импульсов соединен с первым входом третьего элемента И; второй вход которого подключен к выходу последнего разряда третьего регистра адреса, а выход - к счетному входу счетчика и к второму входу второго элемента И, выход которого соединен с вычитающими входами группы счетчиков 21 .Недостатком этого устройства явля. ется узкая область применения. 45 Цель изобретения - расширение области применения устройства путемформирования микроопераций произвольной длительности.Поставленная .цель достигается тем,что устройство, содержащее первыйи второй запоминающие блоки, регистрадреса, буферный регистр, регистрпризнаков микроопераций, счетчик адреса, счетчик, первый, второй, третий элементы ИЛИ, генератор тактовыхимпульсов, первый - четвертый элементы И, элемент НЕ, и мультиплексорлогических условий, причем выход 35регистра адреса соединен с первымвходом дешифратора адреса, выходкоторого соединен с входом первогозапоминающего блока, выход первогозапоминающего блока соединен с информационным входом буферного регистра, выход генератора. тактовых импульсов соединен с первыми входамипервого и второго элементов И, единичные выходы счетчика соединеныс входами первого элемента ИЛИ,выход второго элемента И соединенс вычитающим входом счетчика, выходнуля проверяемых логических условийбуферного регистра соединен с первым информационным входом мультиплексора логических условий, первыйвход устройства соединен с вторыминформационным входом мультиплексоралогических условий, дополнительно 55содержит мультиплексор адреса, дватриггера, одновибратор, два элементазадержки, причем кодовый вход устрой,ства соединен с первым информационным входом мультиплексора адреса,выход которого соединен с информационным входом регистра адреса, входзапуска устройства соединен с первымуправляющим входом мультиплексораадреса, с единичным входом первоготриггера и первым входом второго элемента ИЛИ, выход которого соединенс единичным входом второго триггера,единичный выход второго триггера соединен с входом одновибратора, выходкоторого соединен с первым входомтретьего элемента И, выход которогосоединен с входами установки в нульбуферного регистра и регистра признаков микроопераций, выход старшегоразряда которого соединен с вторымвходом третьего элемента ИЛИ и вторым управляющим входом мультиплексора адреса, выход первого элемента ИЛИсоединен с входом элемента НЕ, выход которого соединен с вторым входом третьего элемента И и вторымвходом первого элемента И, выход которого соединен с входом первогоэлемента задержки, выход первогоэлемента задержки соединен с нулевымвходом второго триггера, нулевойвыход которого соединен с первымвходом четвертого элемента И, выходчетвертого элемента И соединен с входом второго элемента задержки, выходкоторого соединен со счетным входомсчетчика адреса, выход счетчика адреса соединен с вторым входом дешифратора адреса, выход которого соединен с входом второго запоминающегоблока, первый информационный выходвторого запоминающего блока соединенс входами регистра признаков микроопераций, второй информационный выход второго запоминающего блока соединен с информационным входом счетчика, управляющий выход второго запоминающего блока соединен с нулевым входом первого триггера, единичный выход которого соединен стретьим входом первого элемента И,выход немодифицированного кода адреса буферного регистра соединен свторым информационным входом мультиплексора адреса, выход третьегоэлемента ИЛИ соединен также с вторыминформационным входом мультиплексораадреса, выход регистра признаковмикроопераций является выходом устройства, вход логических условийустройстВа соединен с вторым информационным входом мультиплексора ло30 Устройство работает следующимобразом,С выхода 25 устройства на информационный вход 6,3 мультиплексора45адреса 6 поступает код операции,представляющий адрес первой микроподпрограммы. Одновременно с входа 26 на управляющий вход мультиплексора адреса поступает сигнал "началоработы . По этому сигналу код опера 1 50ции через мультиплексор адреса 6 поступает в регистр адреса 3, определяя номер микроподпрограммы, Крометого, сигнал с входа 26 поступаетчерез элемент ИЛИ 19 на единичныйвход триггера 11, а также на единичный вход триггера 12, переводя ихв единичное состояние. По перепаду рических условий, выход которого соединен с первым входом третьего эле-мента ИЛИ, второй вход которого соединен с выходом модифицируемого разряда буферного регистра, второй входи выход четвертого элемента И соединены соответственно с выходом первогоэлемента И и с тактовым входом дешифратора адреса, выход первого элемента ИЛИ соединен с вторым входомОвторого элемента И,На чертеже приведена функциональная схема микропрограммного устройства управления.Микропрограммное устройство управления содержит первый запоминающийблок 1, второй запоминающий блок 2с первым 2.1, вторым 2.2 информационными полями и 2.3 управляющим полем,регистр адреса 3, буферный регистр 4 20с полями: 4.1 - немодифицируемогоразряда, 4,2 - модифицируемого разряда, 4.3 - кода логических условий,регистр признаков микроопераций 5,мультиплексор адреса 6 с полями: 256.1 - второй информационный вход,6.2 - второй управляющий, 6.3 - первый информационный, 6.4 - первыйуправляющий, мультиплексор логических условий 7, счетчик адреса 8,счетчик 9, дешифратор адреса 1 О,триггер управления 11, триггер оста"нова 12, генератор тактовых импульсов 13, элементы И 14-17, одновибратор 18, элементы ИЛИ 19-21, элементы задержки 22,23, элемент НЕ 24,кодовый вход 25 устройства, входзапуска 26 устройства, вход логических условий 27 устройства, выход 28устройства,40 потенциала на единичном выходе триггера 11 на выходе одновибратора 18появляется импульс, который производит установку в нуль буферного регистра 4 и регистра признаков микроопераций 5 (на выходе элемента НЕ 24 имеется сигнал, разрешающий обнулениерегистров 4 и 5 через элемент И 17). Триггер 12 устанавливается в единичное состояние и разрешает прохождение импульсов с выхода генератора 13 через элемент И 14 Первыйтактовый импульс с выхода элемента И 14 через элемент задержки 22производит обнуление триггера 11.Второй импульс с выхода генератора 13 через элементы И 14 и 16 поступает на синхронизирующий вход дешифратора адреса 10 и производитвыборку из первого 1 и второго 2 запоминающих блоков.Из запоминающего блокабудетсчитан адрес очередной микроподпрограммы, который заносится в буферныйрегистр 4. Микроподпрограмма представляет линейную последовательностьмикрокоманд микропрограммы. Операционная часть из запоминающего блока 2 поступает в регистр признаковмикроопераций 5, устанавливая соответствующие разряды состояние, Одновременно с выборкой информации иззапоминающих блоков 1 и 2 сигналчерез элемент задержки 23 поступаетна счетный вход .счетчика адреса 8,увеличивая его состояние на единицу.Очередной тактовый импульс разрешает выборку из запоминающего блока 2 второй микрокоманпы сопержашей только операдионнчю часть. Выбранная микрокоманда, поступая навходы регистра признаков микроопераций 5, переводит соответствующие разряды в противоположное состояние,чем заканчивают выдачу микрооперациис первого выхода и начинает выдачумикроопераций с второго и третьеговыходов. Содержимое счетчика адреса 8 увеличивается на единицу. Блок 2вновь начнет выдачу микрооперацийс первого выхода и закончит микрооперацию на втором выходе,Так как в данный момент временине нужно изменять состояние ни одного выхода, то в пятой микрокомандес целью исключения следующей "пустой"микрокоманды и оптимизации памятизадается код числа блокируемых тактовых импульсов, в данном случае он равен единице.После выборки пятой микрокоманды код числа блокируемых тактовых им,пульсов .с информационного выхода за" поминающего блока 2 поступает на информационные входы счетчика 9 и через элемент ИЛИ 20 элемент НЕ 24 запрещает прохождение тактового импульса с генератора 13 через элемент И 14. 1 О Одновременно пятая микрокоманда закончит выдачу микрооперации с второго выхода и начнет выдачу микроопераций с первого и третьего выходов. Состояние четвертого выхода по-прежнему 15 останется без изменения. С выхода элемента ИЛИ 20 высокий потенциал разрешает прохождение тактового импульса с генератора 13 через элемент И 15 на вычитающий вход сцетчи О ка 9. Низкие потенциалы с выходов обнулившегося счетчика 9 поступают на элемент ИЛИ 20 и с его выхода через элемент НЕ 24 разрешают прохождение тактовых импульсов через эле мент И 14. Тактовый импульс разрешит выборку информации из запоминающего блока 2 микрокоманды, которая изменит состояния соответствующих разрядов регистра 5 на противополож- ЗО ное, чем закончит выполнение микро- операций на первом и третьем выходах и начнет выдачу последней задаваемой микрооперации с второго выхода. Одно" временно с хранением признака послед 35 ней микрооперации микроподпрограммы в запоминающем блоке 2 хранится признак перехода к выполнению очередной микропрограммы.Переход к выполнению очередной микроподпрограммы (линейной последовательности микрокоманд) осуществляется в зависимости от логических условий, поступающих на вход 27 устройства. Модификация адреса очередной микроподпрограммы осуществляется следующим образом.В поле 41 буферного регистра 4 хранится код немодифицированного адреса (постоянная часть адреса), в поле 4.2 - модифицируемый разряд (или группа разрядов при проверке нескольких логических условий), в поле 4.3 - код проверяемого логического условия (или условий) . При поступлении на вход 27 устройства логического условия на выходе мультиплексора логических условий 7 будет либо сигнал логического нуля (если проверяемое логическое условие не выполнено), либо сигнал логической единицы (если проверяемое логическое условие выполнено). При этом постоянная часть адреса дополняется либо нулем, либо единицей в зависимости от выполнения логического условия.Метка-признак с поля 5.2 регистра признаков микроопераций поступает на управляющий вход 6.2 мультиплексора адреса 6 и производит запись сформированного адреса очередной микроподпрограммы в регистр адреса 3;Далее работа, устройства продолжается аналогично. С окончанием выдачи последней микрооперации микропрограммы с выхода поля 2.3 запоминающего блока 2 поступает метка- признак на нулевой вход триггера 12. Триггер 12 перейдет в нулевое состояние и запретит прохождение тактовых импульсов с выхода генератора 13, Устройство готово к приему и выполнению очередной микропрограммы. Применение изобретения позволяет расширить область применения устройства.дряше Корректор И,Мус Тираж 699 П Государственного комитета СССР о делам изобретений и открытий ква, Ж, Раужская наб., д. 4 37НИИПИ Заказ писно 3035, М атент", г,ужгород, ул.Проектна Филиал ПП

СмотретьЗаявка

3554689, 17.02.1983

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

БРАГИН ВИТАЛИЙ НИКОЛАЕВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, КНЫШ ПАВЕЛ ИВАНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.07.1984

Код ссылки

<a href="https://patents.su/6-1103230-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Микропрограммное устройство управления

Случайный патент: Производные 4-(моноалкиламино)бензойной кислоты или их соли, обладающие гиполипидемической активностью