Система передачи и приема информации с коррекцией ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

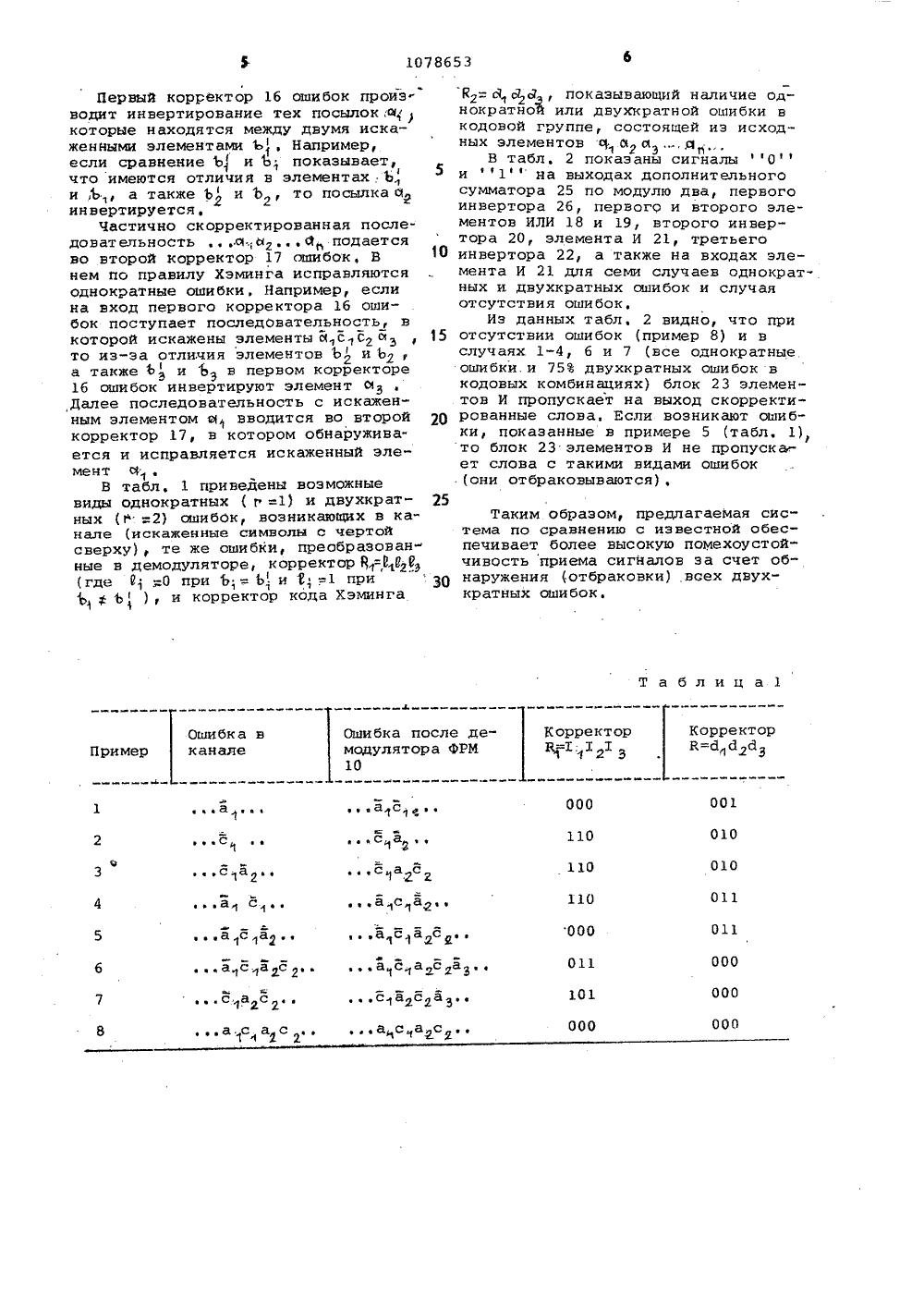

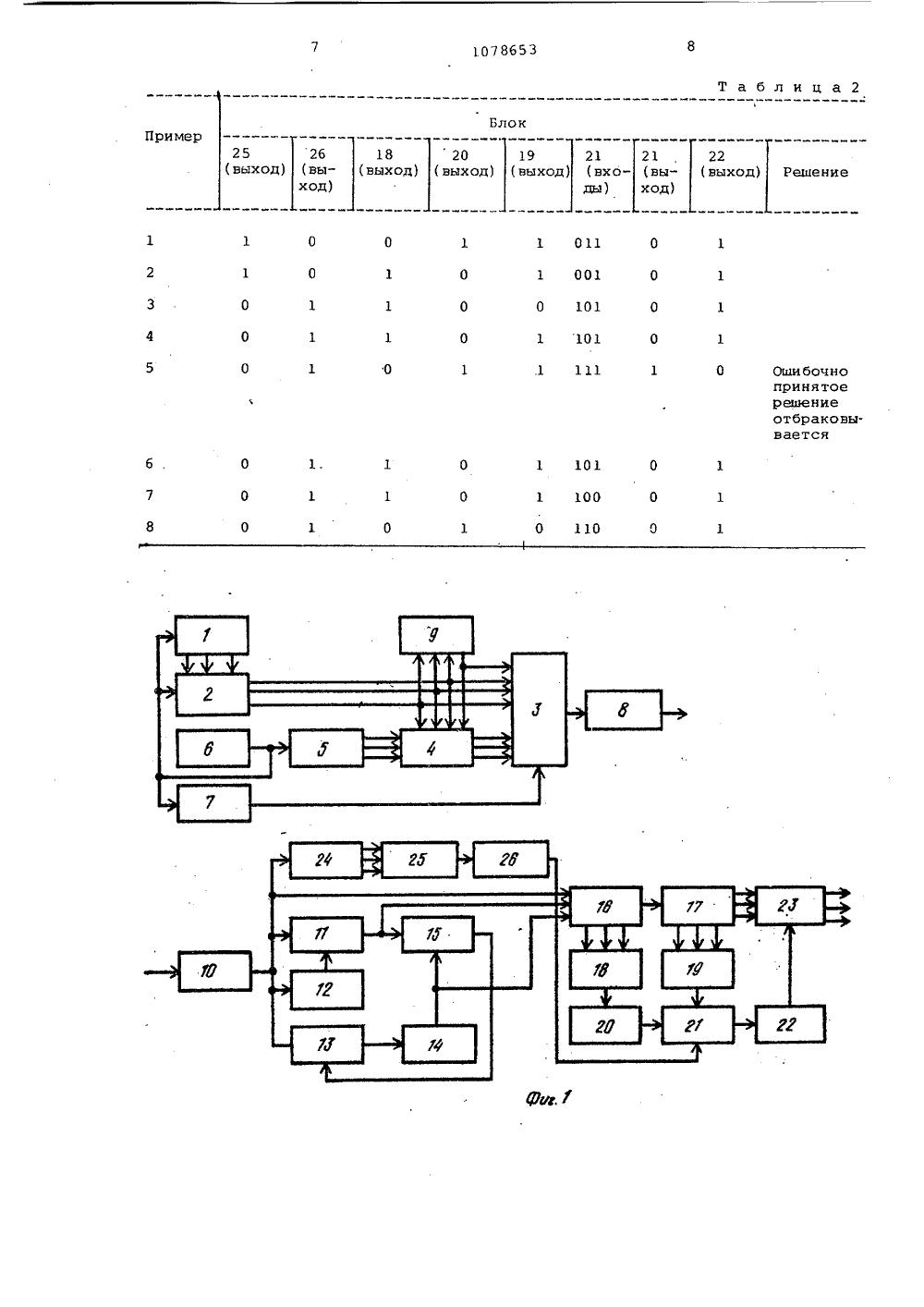

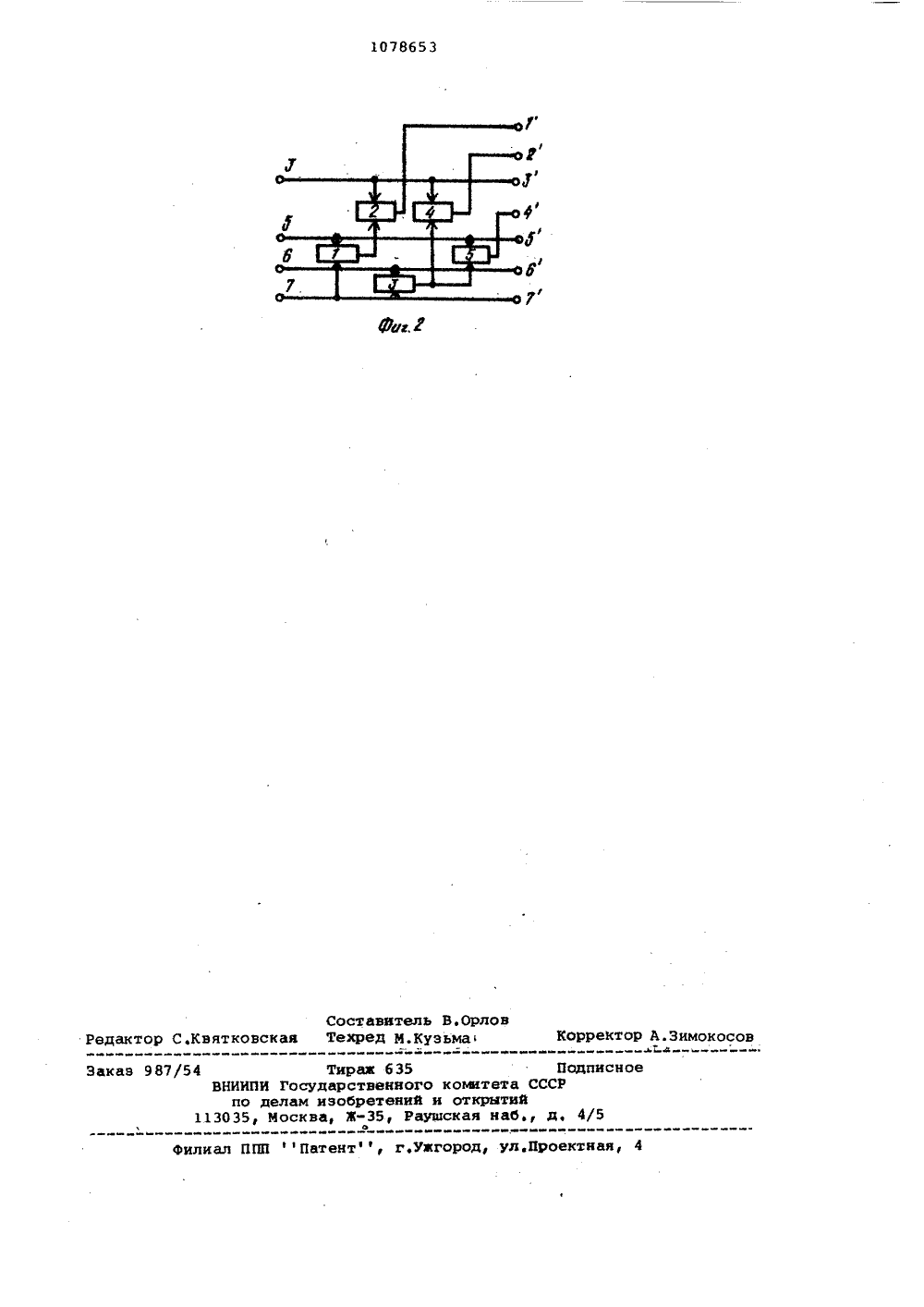

СУДАРСТВЕННЫИ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ Н АВТОРСКОМУ/ СВИДЕТЕПЬСТ Бюл. 9 9ов, Л М;Финк,Л.А. Горский электротехниче -связиБонч-Бруевича4(088.8)кое свидетельство СССН 04 1 1/10, 1978.е свидетельство СССРН 04 Ь 1/10, 1981,(54)(57) СИСТЕМА ПЕРЕДАЧИ И ПРИЕМАИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОШИБОК, содержащая на передающей сторойе последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизатор и генератор эталонного кода,последовательно соединенные регистри модулятор, а также блок сумматоров по модулю два и блок считывания,выход которого подключен к управляющему входу регистра, при этом выходыпреобразователИ кода подключены кобъединенным первым входам блока сумматоров по модулю два и регистра,выходы генератора эталонного кодаподключены к вторым входам блока сумматоров по модулю два, выходы которого подключены к другим входам регистра, выход синхронизатора подключен к объединенным входам блока кодирования, преобразователя кода и блока считывания, входы блока кодирования являются входами системы, наприемной стороне - последовательносоединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенныепервый корректор ошибок и второйкорректор ошибок, а также демодулятор, выход которого подключен к входу элемента задержки и другим входамсинхронизатора и сумматора по модулюдва, выход которого подключен к первому входу первого корректора ошибок,выход генератора эталонного кода подключен к второму входу первого корректора ошибок и другому входу коррелятора, о т л и ч а ю щ а я с я тем,что, с целью повышения помехоустойчивости, на передающей стороне введен сумматор по модулю два, входыкоторого соединены с выходами преобразователя кода, а выход сумматора Жпо модулю два подключен к дополнительным входам регистра и блока сум- Ц)маторов по модулю два, на приемнойстороне введены последовательно сое- Ъдиненные преобразователь кода, дополнительный сумматор по модулю два Яи первый инвертор, последовательносоединенные первый элемент ИЛИ, вто- фффффрой инвертор, элемент И и третий инвертор, а также выходной блок элементов И и второй элемент ИЛИ, входы 3которого соединены с первыми выхода- (фми второго корректора ошибок, а выход второго элемента ИЛИ подключенк второму входу элемента И, вторыевыходы второго корректора ошибокподключены к входам выходного блока элементов И, дополнительный входкоторого соединен с выходом третьего инвертора, выход демодулятораподключен к входу преобразователя 3 ькода и третьему входу первого корректора ошибок, а выход первого инвертора подключен к третьему входу элемента И.Изобретение относится к электросвязи и может быть использовано втелеметрии и при передаче данных,Известна система передачи и приемаинформации с коррекцией ошибок, содержащая на передающей стороне последовательно соединенные синхронизатор, генератор эталонного кода, блоксумматоров по модулю два и регистр,а также модулятор, на приемной стороне - демодулятор и объединенные по 10входу сумматор по модулю два и элемент задержки, выход которого подключен к второму входу сумматора по модулю два, выход которого подключенк первому входу коррелятора, к второ му входу которого подключен выходгенератора эталонного кода, к второму входу которого подключен выходсинхронизатора 1 3,Недостаток укаэанной системы20 низкая помехоустойчивость.Известна также система передачи и приема информации с коррекцией ошибкок, содержащая на передающей стороне последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизатор и генератор эталонного кода, последовательно соединенные регистр и модулятор а также блок сумматоров по модулю два и блок считывания, выход которого подключен к управляющему входу регистра, при этом выходы преобразователя кода подключены к объединенным первым З 5 входам блока сумматоров по модулю два и регистра, выходы генератора эталонного кода подключены к вторым входам блока сумматоров по модул два, выходы которого подключены к 40 другим входам регистра, выход синхронизатора подключен к объединенным входам блока кодирования, преобразователя кода и блока считывания, входы блока кодирования являются входа ми системы, на приемной стороне последовательно соединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, последовательно соединенные первый корректор ошибок и второй корректор ошибок, а также демодулятор, выход которог подключен к входу элемента задержки и другим входам синхронизатора и сумматора по модулю два, выход которого подключен к первому входу первого корректора ошибок, выход генератора эталонного кода подключен к второму входу первого корректора ошибок и другому входу коррелятора, 60 выход демодулятора подключен к второму входу второго корректора ошибок, а выход синхронизатора подключен к объединенным третьим входам первого корректора ошибок и второго, 65 корректора ошибок, выход которого является выходом системы Г 2 3Недостатком известной системы является низкая помехоустойчивость, вследствие чего 25 двухкратных оши бок не исправляется и не обнаруживаетсяЦель изобретения - повышение помехоустойчивости.Для достижения укаэанной цели в систему передачи и приема информации с коррекцией ошибок, содержащую на передающей стороне последовательно соединенные блок кодирования и преобразователь кода, последовательно соединенные синхронизатор и генератор эталонного кода, последователь. но соединенные регистр и модулятор, а также блок сумматоров по модулю два и блок считывания, выход которого подключен к управляющему входу регистра, при этом выходы преобразователя кода подключены к объединенным первым входам блока сумматоров по модулю два и регистра, выходы генератора эталонного кода подключены к вторым входам блока сумматоров по модулю два, выходы которого подключены к другим входам регистра, выход синхронизатора подключен к объединенным входам блока кодирования, преобразователя кода и блока считывания, входы блока кодирования являются входами системы, на приемной стороне - последовательно соединенные элемент задержки, сумматор по модулю два, коррелятор, синхронизатор и генератор эталонного кода, пос- ледовательно соединенные первый корректор ошибок и второй корректор ошибок, а также демодулятор, выход которого подключен к входу элемента задержки и другим входам синхронизатора и сумматора по модулю два, выход которого подключен к первому входу первого корректора ошибок, выход генератора эталонного кода подключен к второму входу первого корректора ошибок и другому входу коррелятора, на передающей стороне введен сумматор по модулю два, входы которого соединены с выходами преобразователя кода, а выход сумматора по модулю два подключен к дополнительным входам регистра и блока сумйаторов по модулю два, на приемной стороне введены последовательно соединенные преобразователь кода дополнительный сумматор по модулю два и первый инвертор, последовательно соединенные первый элемент ИЛИ, второй инвертор, элемент И и третий инвертор, а также выходной блок элементов И и второй элемент ИЛИ, входы которого соединены с первыми выходами второго корректора ошибок, а выход второго элемента ИЛИ подключен к второму входу элемента И, вто1078653 рые выходы второго корректора ошибок подключены к входам выходногоблока элементов И, дополнительныйвход которого соединен с выходомтретьего инвертора, выход демоцулятора подключен к входу преобразователя кода и третьему входу первогокорректора ошибок, а выход первогоинвертора подключен к третьему входу элемента И,На фиг, 1 приведена структурнаяэлектрическая схема системы передачи и приема информации с коррекциейошибок; на фиг, 2 - схема преобразователя кода,Система передачи и приема информации с коррекцией ошибок содержит напередающей стороне блок 1 кодирования, преобразователь 2 кода, регистр3, блок 4 сумматоров по модулю два,генератор 5 эталонного кода, синхронизатор 6, блок 7 считывания, модулятор 8 и сумматор 9 по модулюдва, на приемной стороне - демодулятор 10, сумматор 11 по модулю два,элемент 12 задержки, синхронизатор13, генератор 14 эталонного кода,коррелятор 15, первый корректор 16ошибок, второй корректор 17 ошибок,элементы ИЛИ 18 и 19, второй инвертор 20, элемент И 21, третий инвертор 22, выходной блок 23 элементовИ, преобразователь 24 кода, дополнительный сумматор 25 по модулю два ипервый инвертор 26,Система работает следующим образом,В блоке 1 кодирования формируется исходный двоичный кодовый сигналв виде К-разрядных слов, которые впреобразователе 2 кода (фиг, 2) преобразуются в О -значные слова в соответствии с кодом Хэминга, исправляющим однократные ошибки, Полученные и-значные кодовые комбинациизаписываются в регистр 3 (подаютсяна его первые входы) и следуют напервые входы блока 4 сумматоров помодулю два. На вторые входы блока 4сумматоров по модулю два подаютсял-значные эталонные слова, вырабатываемые в генераторе 5 эталонного кода. В блоке сумматоров по модулюдва производится поэлементное суммирование по модулю два символов информационного и эталонного слов,В сумматоре 9 по модулю два определяется символ:1где а. - символ кбда на выходе преобраэователя 2 кода, Этот символ с выхода сумматора 9 по модулю два поступает на вход блока 4 сумматоров по модулю два, где формируется символ=а ЯЬС= Л где Ъ, - дополнительный символ, выдаваемый генератором 5 эталонного кода,Кодовый сигнал с выходов блока 4 сумматоров по модулю два вводится в регистр 3 через его другие входы. При этом в регистре 3, содержащем 2ячеек, формируется кодовый сиг нал 1 1 2 г "о 01 1 причем символы с, и с размещаютсясоответственно в ячейках с нечетными и четными номерами,Из регистра 3 кодовый сигнал счи тывается по сигналам, которые вырабатывает блок 7 считывания, При этомпараллельный код преобразуется впоследовательный, В модуляторе 8 производится преобразование этого кода20 в код, который используется для передачи сигналов,На выходе демодулятора 10 при отсутствии помех образуется такая жепоследовательность посылок с и с.125 которая поступает на вход модулятора 8. Последовательный кодовый сигнал вводится на первый вход сумматора 11 по модулю два непосредственно и с задержкой на длительностьодной посылки (посредством элемента 12 задержки) на второй вход сумматора 11 по модулю два, При этомпроисходит восстановление на четныхпозициях кодового слова элементовЬ. эталонного кодас 01 аг 02 с С сн С с С с С с С112 233-Ф 5"В я+1 И 1 1 гЮЗЗс 4 СЪ " пгп с и+1) 40 11 2 2 3 3" " и и)+1 Р+1где Ы,1: с, Вс,; Ь,: с,.0+с., так какВосстановленный эталонный кодовыйсигнал Ьпоступает на вход корреля 45 тора 15, на другой вход которогоследует кодовый сигнал Ь с выхода)генератора 14 эталонного кода, Коррелятор 15 в каждой тактовой точкевычисляет Функцию Е Ь,Ь. и выделяет,):1основной пик функции корреляции, соответствующий групповому синхросигналу, т.е, сигналу, обозначающему,например, начало кодового 2 (о+1)-разф 55 рядного сигнала. Этот синхросигналслужит для обеспечения синфазностисигнала, формируемого синхронизатором 13, с входным сигналом.В первый корректор 16 ошибок вво" 60 дится последовательность посылок свыхода демодулятора 10 сс 1 ас,си с)ъ о+1 сг+1 ф сигналы Ь 1 ьг Ьзь ь. 1с выхода сумматора 11 по модуЗпо дваи сигналы Ь 1 ЬЬэЬ 4 Ь Ь .1 с выхо,да генератора 14 эталонного кода.1078653 Таблиц а 1 Ошибка после демодулятора ФРМ10 Ошибка вканаде Корректор В-Х:Х 18 КорректорЛ 2 3 Пример аЛс,.с, а 001 000 а с 010 110 с,а с мса 2000 101 000 000 аса с Первый корректор 16 ошибок производит инвертирование тех посылок;акоторые находятся между двумя искаженными элементами Ъ, Например,если сравнение Ъ и Ь показывает,что имеются отличия в элементах Ъи Ь, а также Ь и Ь , то посылка оинвертируется,Частично скорректированная последовательность о.,аг Ф подаетсяво второй корректор 17 ошйбок, Внем по правилу Хэминга исправляютсяоднократные ошибки, Например, еслина вход первого корректора 16 ошибок поступает последсвательность, вкоторой искажены элементы ю 1 Сл Сг оЭто из-за отличия элементов Ь и Ъ 2,а также Ьэ и Ъ в первом корректоре116 ошибок инвертируют элемент йЭДалее последовательность с искаженным элементом ФЛ вводится во второйкорректор 17, в котором обнаруживается и исправляется искаженный элемент сФ,В табл. 1 приведены возможныевиды однократных ( г:1) и двухкратных (г:2) ошибОк, возникающих в канале (искаженные символы с чертойсверху), те же ошибки, преобразованные в демодуляторе, корректор л=л 021 э(где 11 рО при Ъ;: Ь и ; р 1 приЬ Ь ), и корректор кода Хэминга Кг- й,оИ , показывающий наличие однократной или двухкратной ошибки вкодовой группе, состоящей из исходных элементов с б а -,йг эВ табл. 2 показаны сигналы05 и 1на выходах дополнительногосумматора 25 по модулю два, первогоинвертора 26, первого и второго элементов ИЛИ 18 и 19, второго инвертора 20, элемента И 21, третьего1 О инвертора 22, а также на входах элемента И 21 для семи случаев однократных и двухкратных ошибок и случаяотсутствия ошибок,Из данных табл. 2 видно, что при15 отсутствии ошибок (пример 8) и вслучаях 1-4, б и 7 (все однократныеошибки.и 75 двухкратных ошибок вкодовых комбинациях) блок 23 элементов И пропускает на выход скорректированные слова. Если возникают ошибки, показанные в примере 5 (табл. 1),то блок 23 элементов И не пропускает слова с такими видами ошибок(они отбраковываются),25 Таким образом, предлагаемая система по сравнению с известной обеспечивает более высокую помехоустойчивость приема сигналов за счет обЗ 0 наружения (отбраковки) всех двухкратных ошибок.1078653 Составитель В.ОрТехред М.Кузьма ор С.Квятковска каэ 987/54 Подписноеета СССРкрытийнабд, 4/5 илиал ППППатент ф, г,уагород, ул,Проектная Тирай 635 ВНИИПИ Государственного коан по делам изобретений и от 3035, Москва, 3-35, Раушская ф

СмотретьЗаявка

3429648, 22.04.1982

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

САФАРОВ РИЗА ТАДЖИЕВИЧ, ФИНК ЛЕВ МАТВЕЕВИЧ, БРУССЕР ФАЙВИШ ИЗРАИЛЕВИЧ, ГОР ЛЕВ АБРАМОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: информации, коррекцией, ошибок, передачи, приема

Опубликовано: 07.03.1984

Код ссылки

<a href="https://patents.su/6-1078653-sistema-peredachi-i-priema-informacii-s-korrekciejj-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема информации с коррекцией ошибок</a>

Предыдущий патент: Способ передачи дискретной информации с частотно-фазовой манипуляцией

Следующий патент: Пороговый декодер сверточного кода

Случайный патент: Композиция на основе полиэтилена