Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

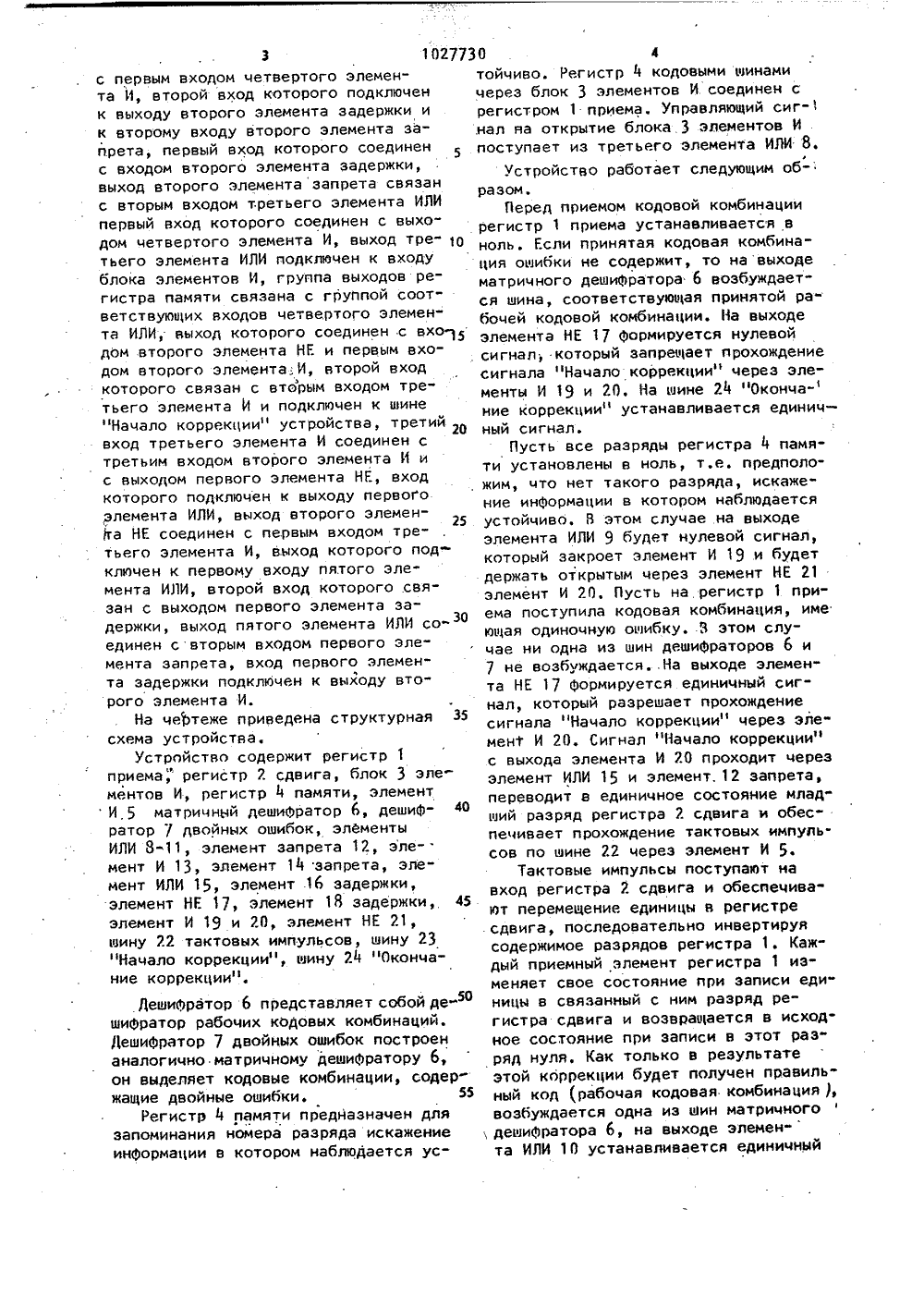

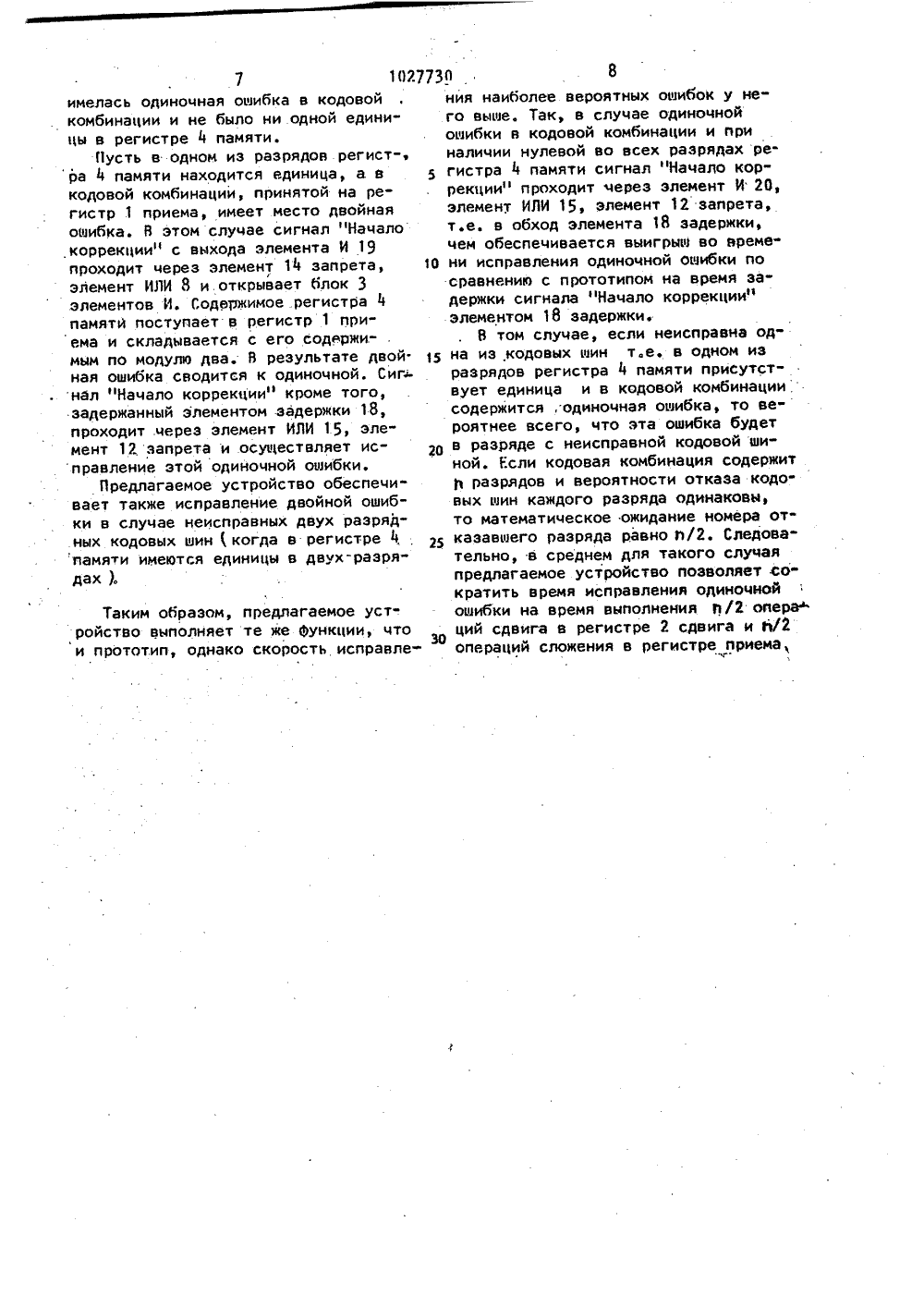

1027730 связан с выходом первого элементазадержки, выход пятого элемента ИЛИсоединен с вторым входом первого эле. Изобретение относится к вычислительной технике и может быть использовано в устройствах переработки ипередаци дискретной инФормации,Известно устройство, содержащее 5регистр приема, матрицу, регистр сдвига, элемент И, элемент ИЛИ, элементзапрета., элемент Фиксации оконцанияприема кодовой комбинации1,Недостатком устройства является 10возможность исправления линь одиночных ошибок.Наиболее близким к предлагаемомуявляется устройство, содержащее регистр приема, регистр сдвига, матрицнцй дешиФратор, дениФратор одиночныхошибок, первый и второй элементы ИЛИ,блок элементов И, регистр памяти,элемент И первый, второй, и третийэлементы запрета, элемент задержки, р 0первый вход элемента И является пер"вым входом устройства, второй входэлемента И соединен с первым входомрегистра сдвига и выходом первогоэлемента запрета, а выход - с вторым д 5входом регистра сдвига, выход которого соединен с первым входом регист"ра приема, выход которого соединенс входом матричного дешиФратора, выходы которого соединены с входамипервого элемента ИЛИ, выход которого соединен с первым входом первогоэлемента запрета и выходом устройства, вход дешиФратора одиночных ошибок соединен с выходом,регистра приема, а его выходы подключены к входам З 5второго элемента ИЛИ, выход которогоподклюцен к второму входу второгоэлемента запрета, выход которого соединен с первым входом третьего элемента запрета, второй вход которого 40соединен с вь 1 ходом первого элемента ИЛИ, а выход - с вторым входом,блока элементов И, первый вход блока элементов И соединен с выходом регистра памяти, а выход блока элементов И подключен к второму входу регистра приема, второй вход устройствасоединен с первым входом второго элемента запрета, вход первого элементазадержки подключен к выходу второгоэлемента И. мента запрета и входом элемента за - держки, выход которого подключен к второму входу первого элемента запрета2 3Недостатком устройства является низкая скорость коррекции ошибок. Цель изобретения - повышение быстродействия коррекции ошибок,Поставленная цель достигается тем,что в устройство для исправления ошибок, содержащее регистр приема, регистр сдвига блока элементов И, регистр памяти, первый элемент И, матричный дениФратор, первый и второйэлементы ИЛИ, первый и второй элементы запрета, первый элемент задержки,.прицем первый вход первого элемента И является тактовым входом устройства, второй вход первого элемента И подключен к выходу первогоэлемента запрета и первому входу ре.гистра сдвига, второй вход которогосоединен с выходом первого элемента И,.выход регистра сдвига связан с первымвходом регистра приема, выход которого связан с входом матричного дениФратора, группа выходов которогоподключена к группе соответствующихвходов первого элемента ИЛИ, выходкоторого соединен с первым входомпервого элемента запрета и являетсясигнальным выходом устройства, группа выходов регистра памяти подключенак группе входов блока элементов И,выход которого связан с вторым входом регистра приема, вход первогоэлемента задержки соединен с первымвходом второго элемента запрета, введены дешиФратор двойных ошибок, третий, четвертый и пятый элементы ИЛИ,второй, третий и четвертый элементы И, второй элемент задержки, первый и второй элементы НЕ, причем выход регистра приема подключен к входудениФратора двойных ошибок, группавыходов которого связана с группойсоответствующих входов второго элемента ИЛИ, выход которого соединен102773 Эс первым входом четвертого элемента И, второй вход которого подключенк выходу второго элемента задержки ик второму входу второго элемента запрета, первый вход которого соединенс входом второго элемента задержки,выход второго элемента запрета связанс вторым входом третьего элемента ИЛИпервый вход которого соединен с выходом четвертого элемента И, выход третьего элемента ИЛИ подключен к входублока элементов И, группа выходов регистра памяти связана с группой соответствующих входов четвертого элемента ИЛИ, выход которого соединен с вхо дом второго элемента НЕ и первым входом второго элемента.:.И, второй входкоторого связан с вторым входом третьего элемента И и подключен к шине"Начало коррекции" устройства, третийвход третьего элемента И соединен стретьим входом второго элемента И ис выходом первого элемента НЕ, входкоторого подключен к выходу первого,элемента ИЛИ, выход второго элемента НЕ соединен с первым входом третьего элемента И, выход которого подключен к первому входу пятого элемента ИЛИ, второй вход которого .связан с выходом первого элемента задержки, выход пятого элемента ИЛИ со" 030единен с вторым входом первого элемента запрета, вход первого элемента задержки подключен к выходу второго элемента И,На чертеже приведена структурная 35схема устройства.Устройство содержит регистрприема," регистр 2 сдвига, блок 3 элементов И, регистр М памяти, элементИ 5 матричный дешиФратор 6, дешиФ" 40ратор 7 двойных ошибок, элементыИЛИ 8-11, элемент запрета 12, элемент И 13, элемент 1 М запрета, элемент ИЛИ 15, элемент 16 задержки,элемент НЕ 17, элемент 18 задержки, 45элемент И 19 и 20, элемент НЕ 21,шину 22 тактовых импульсов, шину 23"Начало коррекции", шину 21 "Окончание коррекции".ДешиФратор 6 представляет собой де шиФратор рабочих кодовых комбинаций.дешиФратор 7 двойных ошибок построенаналогично матричному дешиФратору 6,он выделяет кодовые комбинации, содержащие двойные ошибки. 55Регистр 1 памяти предназначен длязапоминания номера разряда искажениеинФормации в котором наблюдается ус 0 4тойчиво. Регистр Й кодовыми шинамичерез блок 3 элементов И соединен с регистром 1 приема. Управляющий сиг нал яа открытие блока 3 элементов Ипоступает из третьего элемента ИЛИ 8,ЮУстройство работает следующим об-разом,Перед приемом кодовой комбинациирегистр 1 приема устанавливается в ноль. Если принятая кодовая комбинация ошибки не содержит, то на выходе матричного дешиФратора 6 возбуждает" ся шина, соответствующая принятой рабочей кодовой комбинации. На выходе элемента НЕ 17 Формируется нулевойсигнал; который запрещает прохождениесигнала "Начало коррекции" через элементы И 19 и 20. На шине 21 "Окончание коррекции" устанавливается единичный сигнал,Пусть все разряды регистра 1 памяти установлены в ноль, т,е. предположим, что нет такого разряда, искажение инФормации в котором наблюдается устойчиво, В этом случае на выходе элемента ИЛИ 9 будет нулевой сигнал, который закроет элемент И 19 и будет держать открытым через элемент НЕ 21 элемент И 20. Пусть на.регистр 1 приема поступила кодовая комбинация, име ющая одиночную ошибку. Э этом случае ни одна из шин дешиФраторов 6 и 7 не возбуждаетсяНа выходе элемента НЕ 17 Формируется единичный сигнал, который разрешает прохождение сигнала "Начало коррекции" через эле" мент И 20. Сигнал "Начало коррекции" с выхода элемента И 20 проходит через элемент ИЛИ 15 и элемент, 12 запрета, переводит е единичное состояние младший разряд регистра 2 сдвига и обеспечивает прохождение тактовых импуль. сов по вине 22 через элемент И 5.Тактовые импульсы поступают на вход регистра 2 сдвига и обеспечива" ют перемещение единицы в регистре сдвига, последовательно инвертируя содержимое разрядов регистра 1. Каж" дый приемный элемент регистра 1 изменяет свое состояние при записи еди" ницы в связанный с ним разряд регистра сдвига и возвращается в исходное состояние при записи в этот раз" ряд нуля. Как только в результате этой коррекции будет получен правильный код (рабочая кодовая комбинация ), возбуждается одна из шин матричногодешиФратора 6, на выходе элемен-та ИЛИ 10 устанавливается единичный27730 6ким образом, в случае коррекции ошибки возбуждается одна из шин матричного деши 6 ратора 6, и сигнал с выхода элемента ИЛИ 10 поступает на вход элемента 12 запрета, запрещая тем самым прохождение сигнала "Начала коррекции" на вход элемента И 5, Этот же го отказа (неисправности кодовой шины 5 10 сигнал, а на выходе элемента 12 запрета - нулевой сигнал Последний прекращает прохождение тактовых им- пульсов с шины 22 через элемент И 5 на регистр 2 сдвига, На шине "Оконца. ние коррекции" устанавливается единичный сигнал.Если ошибка в одном и том же разряде повторяется несколько раз, что свидетельствует о наличии устойчивото в соответствующий разряд регистра 4 памяти заносится единица. Наличие единиць 1 в одном из разрядов регистра 4 памяти фиксируется элементом ИЛИ 9, сигнал с выхода которого открывает по первому входу элемент И 19 и через элемент НЕ 21 закрывает элемент И 20,При наличии единицы в одном из разрядов регистра 4 памяти и отсутст" вии овиЬок в кодовой комбинации работа устройства не отличается от изложенного выше.Пусть один из разрядов регистра 4 памяти содержит единицу и в принятой кодовой комбинации содержится одиночсигнал поступает на шину 24 "Окончание коррекции".1 О Менее вероятным оказывается случай,когда одна из кодовых шин неисправна ( присутствует единица в одном из разрядов регистра 4 памяти ), а в кодовой комбинации имеет место одиночная ошиб 15 ка в другом разряде. В этом случае,после описанного выше поразрядногосложения по модулю два содержимого регистра 1 приема с содержимым регистра 4 памяти, одиночная ошибка перево дится в двойную. В результате этоговозбуждается одна из вин девифратора 7 двойных ошибок. Элемент 16 задержки осуществляет задержку сигнала"Начала коррекции" на время, необходи 25 мое для надежной переписи содержимого регистра 4 памяти в регистр 1 приема для сложения с его содержимым поная ошибка. В этом случае ни одна изшин матричного дешиФратора 6 и дешифратора 7 двойных ошибок не возбуждается, Нулевой сигнал с выхода элемента ИЛИ 10, пройдя через элемент НЕ 17, открывает по третьим входам элементь 1 И 1 9 и 20. Причем в данном случае элемент И 19 по первому входуоткрыт, а элемент И 20 закрыт, Сиг" нал "Начало коррекции", пройдя через элемент И 19, поступает на вход элементов 16 и 18 задержки, а также через элемент 14 запрета, и элемент ИЛИ 8 открывает блок 3 элементов И, Содержимое регистра 4 памяти поступает в регистр 1 приемных элементов, изменяя состояние соответствующего разряда кодовой комбинации ( выполняется операция поразрядного сложения по модулю 2 ), В результате оди ночная ошибка либо сводится к двойной, лиЬо преобразуется в рабочую кодовую комбинацию, Более вероятным является второй вариант, так как единица в данном разряде регистра 4 памяти говорит о неисправности кодовой шины этого разряда. Следовательно, если неисправна одна из кодовых шин и в кодовой комбинации присутствует одиночная ошибка, то вероятнее всего, что она возникла в разряде, имеющем неисправную кодовую шину. Тамодулю два, После этого сигнал с выхода элемента 16 задержки запрещает проЗо хождение сигнала "Начало коррекции"через элемент 14 запрета, это приводит к закрытию Ьлока 3 элементов И поаторому входу. В то же время сигнал свыхода элемента 16 задержки держит от"крытым по второму входу элемент И 13.Сигнал, возникший на одной из шин де"шифратора 7 двойных ошибок, проходитчерез элемент ИЛИ 11, открытый по второму входу элемент И 13, схему ИЛИ 840и вновь открывает блок 3 элементов И,разрешая тем самым повторное сложениепо модулю два содержимого регистра 1приема с содержимым регистра 4 памяти.В результатеэтого двойная ошибка сво,дится к первоначально присутствующей в кодовой комбинации одиночной оиибке. Элемент 18 задержки предназначен для задержки сигнала "Начало коррекции" на время, необходимое для описанной выше двойной пересылки содержи 5 О мого регистра 4 памяти в регистр 1приема. Сигнал с вцхода элемента 18задержки проходит через элементИЛИ 15, элемент 12 запрета, переводитв единичное состояние младший разряд55 регистра 2 сдвига и обеспечивает:прохождение тактовых импульсов через элемент И 5, Далее устройство работает аналогично описанному случаю, когдаТаким образом, предлагаемое устройство выполняет те же Функции, что и прототип, однако скорость исправле 7 102 имелась одиночная ошибка в кодовой комбинации и не было ни .одной единицы в регистре 4 памяти.Пусть в одном из разрядов регист-, ра 4 памяти находится единица, а в кодовой комбинации, принятой на регистр 1 приема, имеет место двойная ошибка. В этом случае сигнал "Начало коррекции" с выхода элемента И 19 проходит через элемент 14 запрета, элемент ИЛИ 8 и открывает блок 3 .элементов И. Содержимое .регистра 4 памяти поступает в регистр 1 приема и складывается с его содержи.- . мым по модулю два. В результате двой. ная ошибка сводится к одиночной. Сиг- нал "Начало коррекции" кроме того, задержанный элементом .задержки 18, проходит через элемент ИЛИ 15, эле" мент 12 запрета и осуществляет исправление этой одиночной ошибки.Предлагаемое устройство обеспечи" вает также исправление двойной ошибки в случае неисправных двух разрядных кодовых шинкогда в регистре 4. памяти имеются единицы в двух-разрядах ). 7730 8ния наиболее вероятных ошибок у не"го выше. Так, в случае одиночнойошибки в кодовой комбинации и приналичии нулевой во всех разрядах регистра 4 памяти сигнал "Начало кор"рекции" проходит через элемент И 20,элемент ИЛИ 15, элемент 12 запрета,т.е. в обход элемента 18 задержки,чем обеспечивается выигрыш во време ни исправления одиночной ошибки посравнению с прототипом на время задержки сигнала "Начало коррекциифэлементом 18 задержки.В том случае, если неисправна од" 15 на из кодовых шин т.е. в одном изразрядов регистра 4 памяти присутствует единица и в кодовой комбинациисодержится ,одиночная ошибка, то вероятнее всего, что эта ошибка будет 20 в разряде с неисправной кодовой шиной. Если кодовая комбинация содержитП разрядов и вероятности отказа кодовых шин каждого разряда одинаковы,то математическое ожидание номера от" 2 казавшего разряда равно и/2. Следовательно, в среднем для такого случаяпредлагаемое устройство позволяет сократить время исправления одиночнойошибки на время выполнения ь/2 операций сдвига в регистре 2 сдвига и 6/2операций сложения в регистре приема, 1027730и, Сафронова нта Ко П ннбго комитета тений и открыти Ра ская наб Деев евеевеееевзобр Ж" щщеерая, 4 д даПроек 110филиал т Состави Тех еееввеев еТиражИП 11 Госудапо делам ир МоскваППП "Пате итель Т.фа вещее 706 рстве ооектор О. Тиговеще вввещщеодписноеСССРй

СмотретьЗаявка

3409184, 22.03.1982

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

ПАЦКЕВИЧ СЕРГЕЙ АЛЕКСАНДРОВИЧ, ПАШКОВ ЮРИЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, ошибок

Опубликовано: 07.07.1983

Код ссылки

<a href="https://patents.su/6-1027730-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>