Устройство для вычитания по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 959067

Авторы: Королев, Краснобаев, Сергеев

Текст

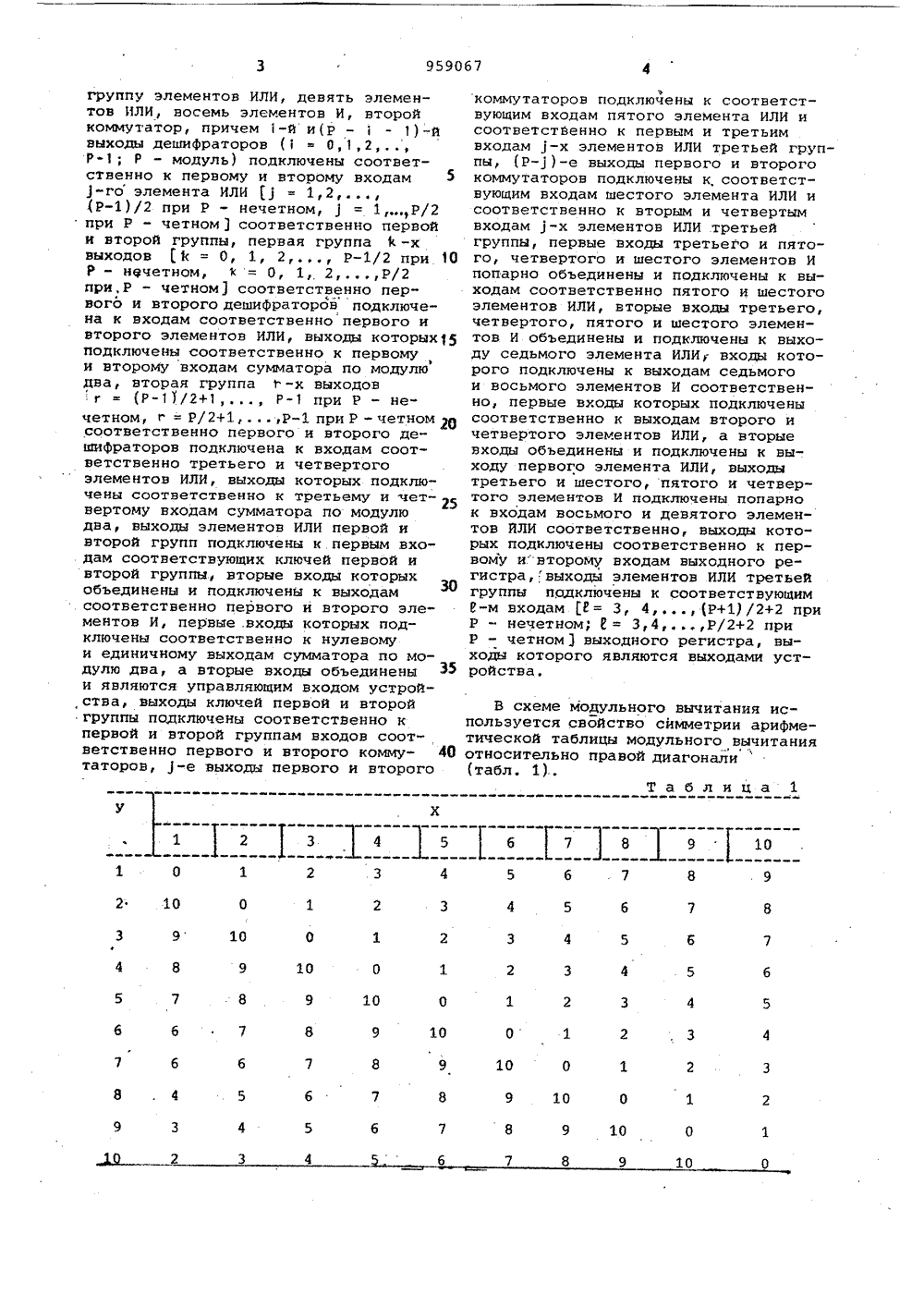

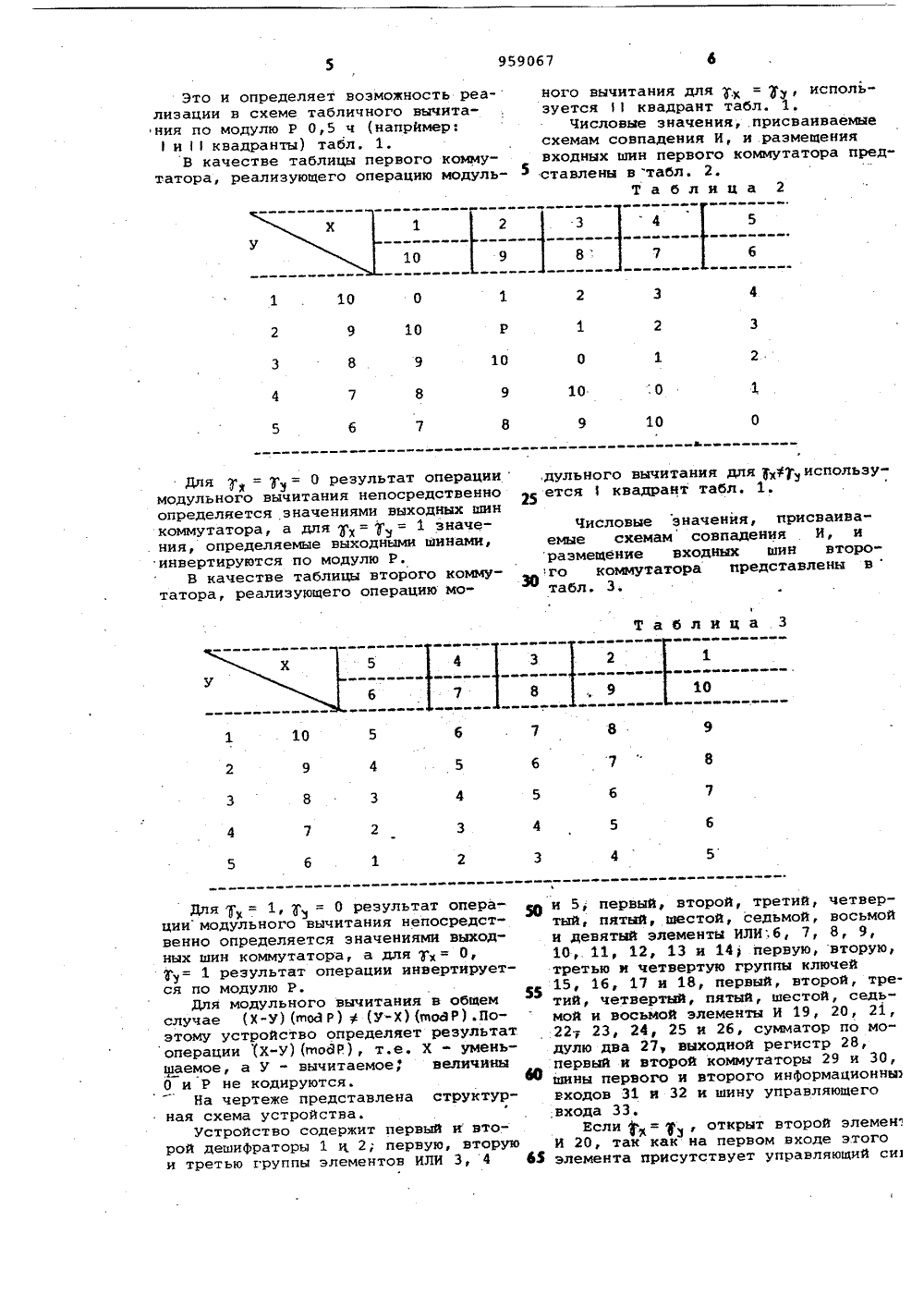

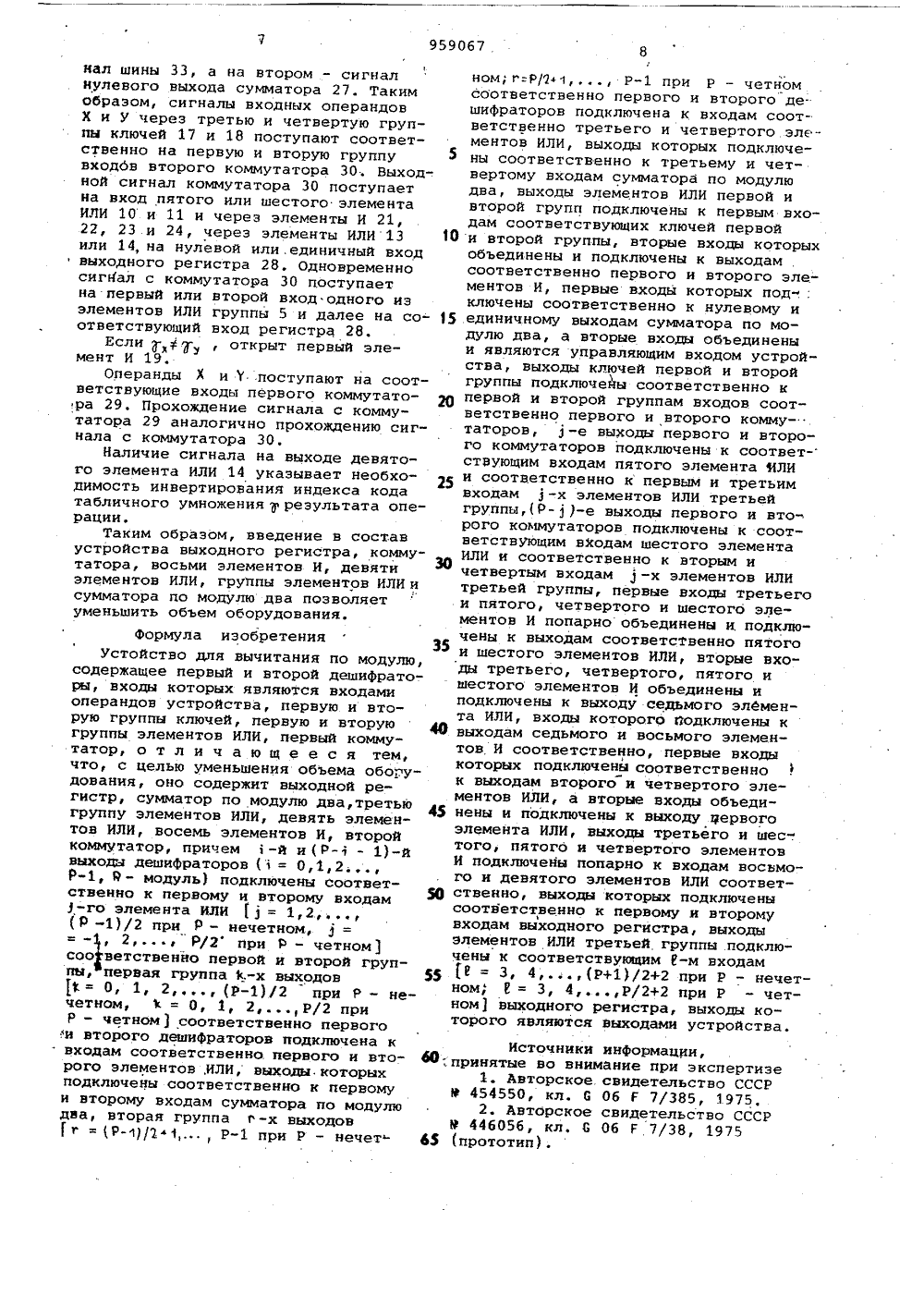

Гпи 959067 ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(22) Заявлено 061".80 (21) 3213273/18-24 1) М. Кл,С Об Г 7/49 с присоединением заявки Мо(23) Приоритет Государственный комитет СССР по делам изобретений и открытийДата опубликования описания 150982 В.А, Краснобаев, А,В, Королев и Б.И. Сергеев ф(54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ПО МОДУЛЮ Изобретение относится к вычисли- ". тельной технике.Известно устройство для сложения чисел в системе остаточных классов, содержащее двоичные матрицы сложения, группы элементов ИЛИ, блок упраВления, комбинационные схемы, группу элементов И и соответствующие связи 1.Недостаток устройства - большое количество оборудования.Наиболее близким к предлагаемому является отличительный сумматор-вычитатель. в системе остаточных классов, содержащий три двоично-десятичных операидных дешифратора с выходными кодовыми шинами, первый из которых соединен с входами первой группы ключевых схем, выходы которых связаны с входами соответствующих входных вентильных сборок, второй дешифратор выходами подключен к соответствующим входам формирователей, входы первого . и второго дешифраторовсоединены с шиной управляющего сигнала, выходную вентильную сборку и импульсные усилители выходных сигналов, а .также координатно-узловые трансформаторы, пассивную кодовую линейку. и вторую группу ключевых схем, причем выходы вход. ных вентильных сборок и формирователей соединены через соответствующиепервичные обмотки координатно-узловызтрансформаторов, вторичные обмоткикоторых Соединены с соответствующимивходами выходных вентильных сборок,выходы этих вентильных сборок связаны с первой группой входов пассивнойкодовой линейки, которая по второйгруппе входов соединена с выходамивторой группы ключевых схем, соеди- .ненных по входам и соответствующими выходными шинами третьего дешифратора, выходы пассивной кодовойлинейки соединены с соответствующими входами импульсных усилителейвыходных сигналов 2.Однако это устройство характеризуется большим количеством оборудования.Цель изобретения - уменьшениеобъема оборудования.Поставленная цель достигается тем,что устройство для вычитания по модулю, содержащее первый и второй де шифраторы, входы которых являютсявходами операндов устройства, первую.и вторую группы ключей, первую ивторую группы, элементов ИЛИ, первыйкоммутатор, содержит выхолной ре гистр, сумматор по модулю лвв, тростью(Р)/2 при Р - нечетном, ) = 1Р/2при Р - четном 1 соответственно первойи второй группы, первая группа М -хвыходовй = О, 1, 2 Р/2 при 10Р - нЕчетном,= О, 1, 2. Р/2при,Р - четном) соответственно первого и второго дешифраторов подключена к входам соответственно первого ивторого элементов ИЛИ, выходы которых 15подключены соответственно к первомуи второму входам сумматора по модулюдва, вторая группа 1.-х выходов(РУ/2+1 Рпри Р - нечетном, г = Р/2+1Рпри Р в четн 2 Осоответственно первого и второго дешифраторов подключена к входам соответственно третьего и четвертогоэлементов ИЛИ, выходы которых подключены соответственно к третьему и четвертому входам сумматора по модулюдва, выходы элементов ИЛИ первой ивторой групп подключены к первым входам соответствующих ключей первой ивторой группы, вторые входы которыхобъединены и подключены к выходамсоответственно первого и второго элементов И, первые .входы которых подключены соответственно к нулевомуи единичному выходам сумматора по модулю два, а вторые входы объединеныи являются управляющим входом устройства, выходы ключей первой и второйгруппы подключены соответственно кпервой и второй группам входов соответственно первого и второго коммутаторов, )-е выходы первого и второго 1 2 3 4 коммутаторов подключены к соответствующим входам пятого элемента ИЛИ и соответстВенно к первым и третьим входам )-х элементов ИЛИ третьей группы, (Р)-е выходы первого и второго коммутаторов подключены к, соответствующим входам шестого элемента ИЛИ и соответственно к вторым и четвертым входам 1-х элементов ИЛИ третьей группы, первые входы третьего и пятого, четвертого и шестого элементов И попарно объединены и подключены к выходам соответственно пятого и шестого элементов ИЛИ, вторые входы третьего, четвертого, пятого и шестого элементов И объединены и подключены к выходу седьмого элемента ИЛИк входы которого подключены к выходам седьмого и восьмого элементов И соответственно, первые входы которых подключены соответственно к выходам второго и четвертого элементов ИЛИ, а вторые входы объединены и подключены к выходу первого элемента ИЛИ, выходы третьего и шестого, пятого и четвертого элементов И подключены попарно к входам восьмого и девятого элементов йЛИ соответственно, выходы которых подключены соответственно к первому ивторому входам выходного регистра,выходы элементов ИЛИ третьей группы подключены к соответствующим 1-м входам 0 = 3, 4(Р+1) /2+2 при Р - нечетном; Г = 3,4. Р/2+2 при Р - четном 3 выходного регистра, выходы которого являются выходами устройства. В схеме модульного вычитания испольэуется свойство симметрии арифметической таблицы модульного вычитания относительно правой диагонали (табл. 1).5 959067 10 10 0 10 10 2 9 10 3Таблица 3 10 10 Это и определяет возможность реализации в схеме табличного вычитания по модулю Р 0,5 ч (например:иквадранты) табл, 1.В качестве таблицы первого коммутатора, реализующего операцию модульДля )" = у = 0 результат операциимодульного вычитания непосредственно определяется значениями выходных шин коммутатора, а для г = у = 1 значения, определяемые выходными шинами, инвертируются по модулю Р.В качестве таблицы второго коммутатора, реализующего операцию моДля= 1,= 0 результат операциимодульного вычитания непосредственно определяется значениями выходных шин коммутатора, а для у = О,1 результат операции инвертируется по модулю Р.Для модульного вычитания в общем случае (Х-У)(вод Р) Ф (У-Х)(водР).Поэтому устройство определяет результат операции (Х-У)(тодР), т.е, Х - уменьшаемое, а У - вычитаемое, величины 0 и Р не кодируются.На чертеже представлена структурная схема устройства.Устройство содержит первый ивторой дешифраторы 1 и 2; первую, вторую и третью группы элементов ИЛИ 3, 4 ного вычитания для тх = , используется ) квадрант табл. 1,Числовые значения, .присваиваемые схемам совпадения И, и размещения входных шин первого коммутатора представлены в табл. 2.Таблица 2,дульного вычитания для )использу 25 етсяквадрант табл. 1,Числовые значения, присваиваемые схемам совпадения И, и размещение входных шин второго коммутатора представлены втабл. 3,д и 5; первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмойи девятый элементы ИЛИ.,6, 7, 8, 9,10, 11, 12, 13 и 14 первую, вторую,третью и четвертую группы ключей15, 16, 17 и 18, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И 19, 20, 21,22-, 23, 24, 25 и 26, сумматор по модулю два 27, выходной регистр 28,первый н второй коммутаторы 29 и 30,шины первого и второго информационнывходов 31 и 32 и шину управляющего,входа ЗЗ.Если ф = у, открыт второй элеменИ 20, так как на первом входе этого 63 элемента присутствует управляющий си959067 иал шины 33, а на втором - сигнал нулевого выхода сумматора 27Таким образом, сигналы входных операндов Х и У через третью и четвертую группы ключей 17 и 18 поступают соответственно на первую и вторую группу входбв второго коммутатора 30. Выход-. ной сигнал коммутатора 30 поступает на вход пятого или шестого элемента ИЛИ 10 и 11 и через элементы И 21, 22, 23 и 24, через элементы ИЛИ 13 10 или 14, на нулевой или,единичный вход выходного регистра 28, Одновременно сигнал с коммутатора 30 поступает на первый или второй вход одного из элементов ИЛИ группы 5 и далее на со ответствующий вход регистра 28.Если у 4 у , открыт первый элемент И 19.Операнды Х и У .поступают на соответствующие входы первого коммутато.ра 29. Прохождение сигнала с коммутатора 29 аналогично прохождению сигнала с коммутатора 30.Наличие сигнала на выходе девятого элемента ИЛИ 14 указывает необходимость инвертирования индекса кода табличного умножения у результата операции.Таким образом, введение в состав устройства выходного регистра, коммутатора, восьми элементов И, девяти Зо элементов ИЛИ, грунпы элементов ИЛИ и сумматора по модулю два позволяет уменьшить объем оборудования. Формула изобретения 35устойство для вычитания по модулю,содержащее первый и второй дешифраторы, входы которых являются входамиоперандов устройства, первую и вторую группы ключей, первую и вторую,рргруппы элементов ИЛИ, первый коммутатор, о т л и ч а ю щ е е с я тем,что, с целью уменьшения объема оборудования, оно содержит выходной регистр, сумматор по модулю два третью 45группу элементов ИЛИ, девять элементов ИЛИ, восемь элементов И, второйкоммутатор, причем 1 -й и ( Р- - 1)-йвыходы дешифраторов ( 1 = 0,1,2,Р, Р " модуль) подключены соответственно к первому и второму входам 503-го элемента ИЛИ= 1,2.и второго дешифраторов подключена квходам соответственно, первого и вто;рого элементов,ИЛИ, выХоды. которыхподключены соответственно к первомуи второму входам сумматора по модулюдва, вторая группа-х выходов( г = (Р)/1.1 Рпри Р - нечет ыом; г:Р/141 Рпри Р - четномсоответственно первого и второго дешифраторов подключена к входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены соответственно к третьему и четвертому входам сумматора по модулюдва, выходы элементов ИЛИ первой ивторой групп подключены к первым входам соответствующих ключей первойи второй группы, вторые входы которыхобъединены и подключены к выходам .соответственно первого и второго эле. -ментов И, первые входы которых под:ключены соответственно к нулевому иединичному выходам сумматора по модулю два, а вторые входы объединеныи являются управляющим входом устройства, выходы ключей первой и второйгруппы подключены соответственно кпервой и второй группам входов соответственно первого и второго коммутаторов, 1-е выходы первого и второго коммутаторов подключены к соответ-стаующим входам пятого элемента ИЛИи соответственно к первым и третьимвходам-х элементов ИЛИ третьейгруппы,(Р-)-е выходы первого и второго коммутаторов подключены к соответствующим входам шестого элементаИЛИ и соответственно к вторым ичетвертым входам ) -х элементов ИЛИтретьей группы, первые входы третьегои пятого, четвертого и шестого элементов И попарно объединены и. подключены к выходам соответственно пятогои шестого элементов ИЛИ, вторые входы третьего, четвертого, пятого ишестого элементов И объединены иподключены к выходу седьмого элемента ИЛИ, входы которого подключены квыходам седьмого и восьмого элементов И соответственно, первые входыкоторых подключены соответственнок выходам второго и четвертого элементов ИЛИ, а вторые входы объединены и подключены к выходу первогоэлемента ИЛИ, выходы третьего и шес-.того, пятого и четвертого элементовИ подключены попарно к входам восьмого и девятого элементов ИЛИ соответственно, выходы которых подключенысоответственно к первому и второмувходам выходного регистра, выходыэлементов ИЛИ третьей группы .подключены к соответствующим 0-м входамР = 3, 4(Р+1)/2+2 при Р - нечетном; 1 = 3, 4 Р/2+2 при Р - четном 1 выходного регистра, выходы которого являются выходами устройства. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРФ 454550, кл. С 06 Г 7/385, 1975.2. АвтОрское свидетельство СССР9 446056, кл, 6 06 Г 7/38, 1975959067 СоставительТехред;М.Кошт Евстигнеевра рректор Г, й иштулине акт сное 5 ая, 4 аэ 7017/65 ВНИИПИ Госуд по делам и 113035, Москраж 731 рственного комите обретений и открыа Ж, Раушская иал ППП "Патент", г, Ужгород, ул. П ССйФб е

СмотретьЗаявка

3213273, 08.12.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА Н. И. КРЫЛОВА

КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ, КОРОЛЕВ АНАТОЛИЙ ВИКТОРОВИЧ, СЕРГЕЕВ БОРИС ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/49

Опубликовано: 15.09.1982

Код ссылки

<a href="https://patents.su/5-959067-ustrojjstvo-dlya-vychitaniya-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычитания по модулю</a>

Предыдущий патент: Устройство для сравнения чисел

Следующий патент: Устройство для умножения по модулю

Случайный патент: Копировально-фрезерный станок