Микропрограммное устройствоуправления c коррекцией де фектных микрокоманд

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 807291

Авторы: Елисеев, Кондратьев, Петушков

Текст

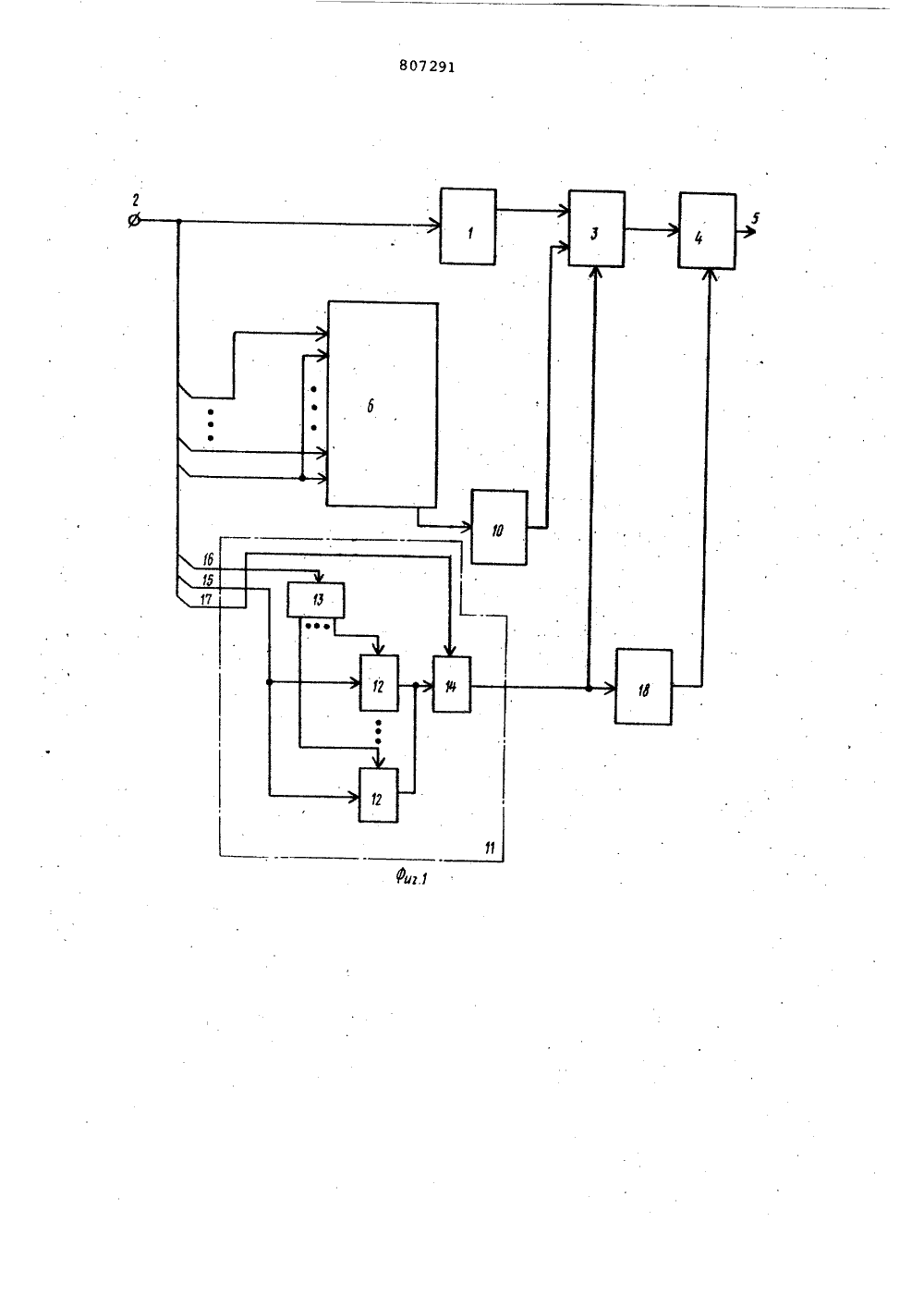

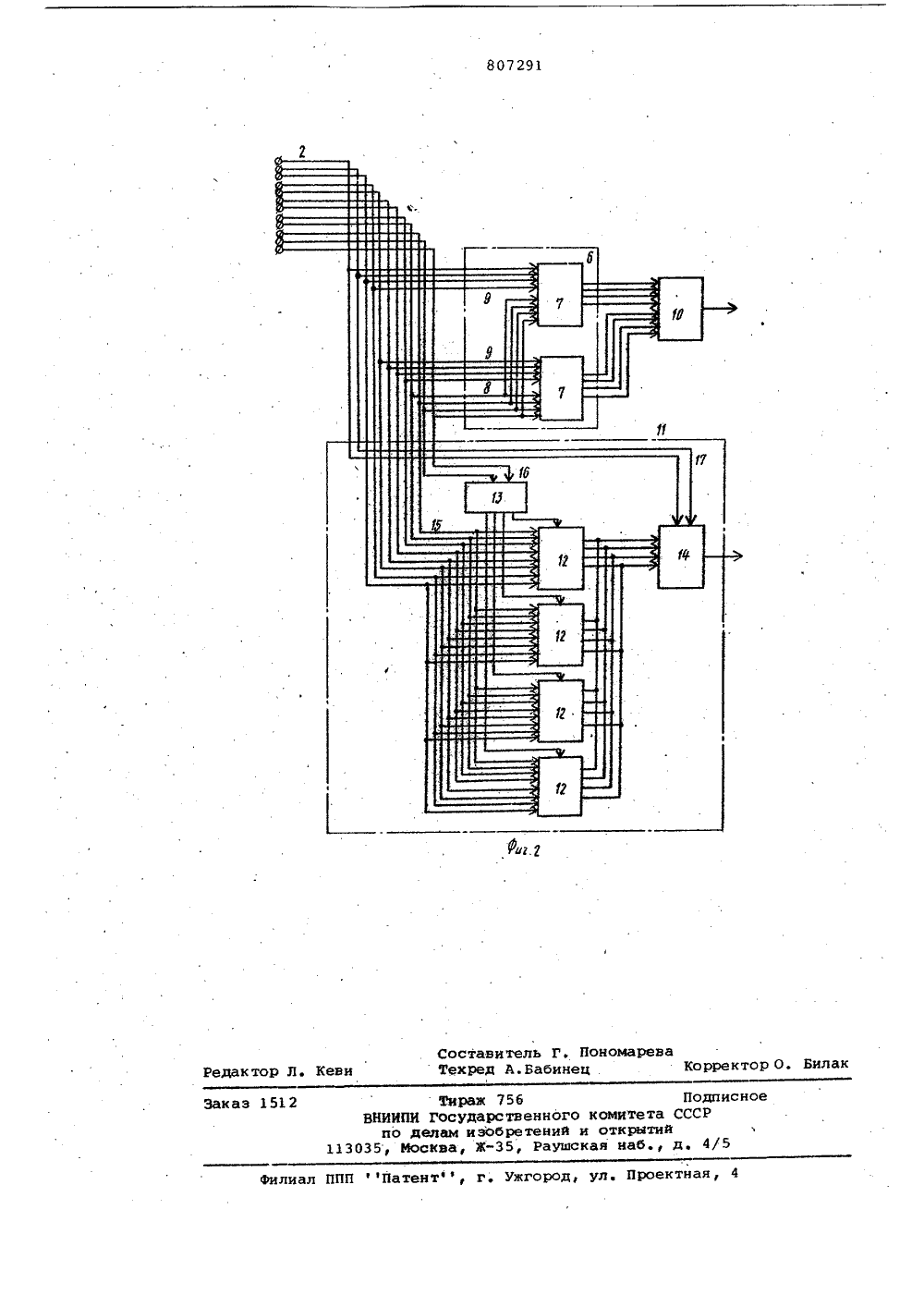

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВ ИТВЛЬСТВУ Союз Советскик Социалистических Рвсеублнк(22) Заявлено 301078 (21) 2679896/18-24с присоединением заявки Йо(51)М. Кл.з 6 06 Р 9/22 Государственный комитет СССР оо аелам изобретений и открытийДата опубликования описания 23,02814 р(72) Авторы изобретения А,П, Кондратьев, А,Н, Петушков и А.А,(71)Заявитель Цель изобретения - упрощение устройства и повышение быстродействияЦель достигается тем, что микропрограммное устройство управления, содержащее основную память, дополнительную память, преобразователь адреса,регистр микрокоманды и узел вы-: работки микроопераций, причем разряды микрокоманды адресного входа устройства соединены с адресным входом основной памяти, выход которой соединен с первым информационным входом регистра микрокоманды, второй информационный вход которого соединен с выходом дополнительной памяти, адресный вход которой соединен с выхо" дом преобразователя адреса, выход регистра микрокоманды соединен с информационным входом узла выработки микроопераций, выход которого соединен синформационным выходом устройства, дополнительно содержит узел задания режимов и узел анализа адреса, причем группа относительных Разрядов адресного входа устройства соединена с первой группой адресных входов преобразователя адреса, вторая группа адресных входов которого соединейа с группой разрядов номера модуля адресного входа устройства,ИзобРетение относится к электронной вычислительной технике и может. использоваться в электронных вычислительных машинах и в системахцифровой автоматики для цифровой обработки данных,Известны микропрограммные устройства управления (МУУ), элементамиуправляющей памяти которых являетсяпамять, допускающая только считывание информации 1).Недостатком их является невозможность корректировки микрокоманд впамяти без дорогостоящей Физическойпеределки самой управляющей памяти. 15Наиболее близким к предлагаемомупо технической сущности является микропрограммное устройство управленияс коррекцией деФектных микрокоманд,содержащее основную память, дополнительную память, преобразователь адреса, состоящий иэ и накопительныхэлементов, регистр микрокоманды иузел выработки микроопераций (2)Недостатком устройства является 25большой объем оборудования схемыкоррекции управляющей памяти, а также снижение быстродействия устройства иэ-за применения этой схемы коррекции. 30(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОРРЕКЦИЕЙ ДЕФЕКТНЫХ МИКРОКОМАНЦразряды номера разряда которого соединены с первым входом узла анализа адреса, второй и третий входы которого соединены соответственно с разрядами номера сегмента и разрядами адреса ячейки адресного входа ус тройства, выход узла анализа адреса соединен с управляющим входом регистра микрокоманд и с входом узла задания режимов, выход которого соеди нен с управляющим входом узла выработки микроопераций. Кроме того, узел го анализа адреса содержит пг накопительных элементов, дешифратор и коммутатор, причем управляющий входкоммутатора соединен с первым входом узла анализа адреса, второй вход которого г 5 соединен с входом дешифратора, группа выходов которого соединена с управляющим входом соответствующего накопительного элемента, адресные входы которых соединены с третьим входом 2 О узла анализа адреса, выходы накопительных элементов соединены с соответствующим входом коммутатора,. выход которого соединен с выходом узла анализа адреса."На Фиг 1 изображена структурная схема устройства; на Фиг, 2 - пример конкретной реализации отдельных узлов,. Устройство микропрограммного Уп равления содержит основную память 1, К-разрядный адресный вход 2,. устройства, регистр 3 микрокоманд, узел 4 выработки микроопераций, информационный выход 5 устройства, преобразо ватель б адреса, состоящий из и накопительных элементов 7, Совокупность К разрядов адресного входа 2 устройства скомпанованы в разрядные группы двояким образом. В(п+1)-кратное разбиение Разрядов адресного входа 2 устройства включена общая группа разрядов номера модуля 8 и и отдельных разрядных групп - групп относительных РазРядов 9 Кроме того, устройство содержит дополнительную память 10, 45 узел 11 анализа адреса, состоящий иэ в накопительных элементов 12, дешиФРатора 13 и коммутатора 14, при этом использовано трехкратное разбиение разрядов адресного входа 2 устройст Ова, включающее младшую разрядную группу " Разряды 15 адреса ячейки, промежуточную разрядную группу - разряды16 номера сегмента и старшую разрядную группу - разряды 17 номера раэ" 55ряда, узел 18 Задания режимов.1Основная память 1 служит для хранения рабочих микрокоманд, Дополнительная память 10, которая по объемузначительно меньше основной памяти 1 60 служит для оперативной записи и хранения скорректированных микрокоманд, которые в основной памяти 1 оказались дефектными, например, из-за ошибок микропрограммирования, 65 Преобразователь 6 адреса служит для преобразования адресов дефектных микрокоманд з адреса меньшей Разрядности дополнительной Гамяти 10. На зыхОДе преобразователя 6 аДРеса появляются преобразованные адреса как де 4 г)ектных, так и корректных микрОком нд при зтОМ преобразОзатель 6 адреса запрограммирован так. что разным адресагл дефектных микрокоманд на его входе соответствуют разные адреса на его выходе, адреса корректных микро- команД преобразуются В случайные аД- реса, которые совпадают как друГ с Другом,. так и с преобразованными адресами дефектных микрокоманд,Например, при К=12, п=2 и при использовании накопительггых элементов 7 с организацией 256 слов х 4 бита преобразователь 6 адреса с выходом на 8 Раэрядоз реализуется следующим Образом (ФиГ е 2)ОбщаЯ Группа Раз РЯДОз 8 номера мОДУлЯ аДреснОГО вхо - Да 2 Устройства содержит 4 старших разряда адреса и подключена к первой группе адресных входов (к четырем старшим адресным входам) обоих накопительных элементов 7. Дзе отдельные разрядные группы относительных Разрядов 9 содержат также по 4разряда, причем первая группа - 4младших, а вторая - 4 промежуточныхразряда адреса Устройства, Каждая отдельная разрядная группа относительных разрядоз 9 подключена к второйгруппе адресных входов (к четыреммладшим адресным входам) соответствующих накопительных элементов 7, Такая органиэация преобразователя адреса позволяет адресовать в дополнительной паггяти от 10 до 256 дефектных микрокоманд, причем реализуется одно" значное распределение адресов этих Микрокоманд в накопительных элементах 7.Узел 11 анализа адрЕса (Фиг. 1) служит для анализа адресов поступающих на адресный вход устройства 2, на необходимость коррекций. Каждому адресу Основной памяти 1 в накопительных элементах 12 соответствует одноразрядная ячейка памяти, в которой записано фО или 1 в зависимости от того, является микрокоманда по этому адресу корректной или деФектной соответственно.Узел 18 задания режимов задает режим рабочего или холостого такта для узла 4 выработки микроопераций в зависимости от сигнала 0 или 1 на выходе узла 11 анализа адреса.Устройство работает следующим образомм.В каждом рабочем такте иэ основной памяти 1 по адресу, поступающему на адресный вход 2 устройства з регистр 3 микрокоманды считывается рабочая микрокоманда . Узел 4 выработки микро- операций на основе этой микрокоманды Формирует управляющие коды микроопераций, которые поступают на информационный выход 5 устройства.В каждом такте адрес, поступившийна адресный вход 2 устройства, анализируется узлом 11 анализа адресана наличие адреса дефектной микрокоманды, При обнаружении этого адресана выходе .узла 11 анализа адреса появляется сигнал, по которому запрещается прием рабочей микрокоманды врегистр 3 микрокоманды из основнойпамяти 1 и разрешается прием из дополнительной памяти 10. Узел 18 задания режимов по. этому сигналу задаетрежим холостого такта, запрещая выработку микроопераций узлом 4 выработки микроопераций.В каждом такте адрес, поступивший.на адресный вход 2 устройства, преобразуется преобразователем б адресав адрес дополнительной памяти 10, Покаждому преобразованному адресу дефектной микрокоманды в дополнительной памяти 10 хранится скорректированная микрокоманда,В холостом такте скорректированная микрокоманда считывается из дополнительной памяти 10 и заноситсяв регистр 3 микрокоманды, В следующем такте узлом 18 задания режимовзадается обычный режим рабочего такта,Изобретение обеспечивает повышение быстродействия устройства и уменьшение обьема оборудования.Быстродействие устройства повышается за счет того, что длительностьрабочего такта устройства определяется только быстродействием основнойпамяти и другими причинами, не связанными со схемами коррекций дефектных микрокоманд.Только при необходимости коррекции дефектной микрокоманды вводитсяхолостой такт на время, требуемоедля считывания скорректированной микрокоманды из дополнительной памяти 10.45Формула изобретения 1. Микропрограммное устройство управления с коррекцией дефектныхмикрокоманд, содержащее основную память, дополнительную память, преобразователь адреса, регистр микроко манды и узел выработки .микрбопераций, причем разряды микрокоманды адресного входа устройства соединены с адресным входом основной памяти, выход которой соединен с первым информационным входом регистра микрокоманды,второй информационный вход которогосоединен с выходом дополнительной памяти, адресный вход которой соединенс выходом преобразователя адреса, выход регистра микрокоманды соединен гинформационным входом узла выработкимикроопераций, выход которого соединен с информационным выходом устройства, о т л и ч а ю щ е е с я тем,что, с целью упрощения устройства иповыаения быстродействия, оно дополнительно содержит узел задания режимов и узел анализа адреса, причемгруппа относительных разрядов адресного входа устройства соединена спервой группой. адресных входов преобразователя адреса, вторая группа адресных входов которого сбединена сгруппой, разрядов номера, модуля адресного входа устройства, разряды номера разряда которого соединены спервым входом узла анализа адреса,второй и третий входы которого соединены соответственно с разрядами номерасегмента и разрядами адреса ячейкиадресного входа устройства, выходузла анализа адреса соединен с управляющим входом регистра микрокоманд и с входом узла задания режимов, выход которого соединен с управляющим входом узла выработки микроопераций.2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что узел анали"за адреса содержит щ накопительныхэлементов, дешифратор и коммутатор,причем управляющий вход коммутаторасоединен с первым входом узла анализа адреса, второй вход которого соединен а входом дешифратора, группавыходов которого соединена с управляющим входом соответствукюего накопительного элемента, адресные входыкото 1 ых.соединены с третьим входомузла .анализа адреса, выходы накопительных элементов соединены с соответствующим входом коммутатора, выход которого соединен с выходом уэ"ла анализа адреса.Источники информации,принятые во внимание при экспертизе1. Хассон С. Микропрограммное устройство управленияВып. 1М 1974,2. Патент, Франции Р 2328263,кл. 6 11 С 29/ОО, опублик. 1977(пРототип).807291 оставитель Г, Пономареваехред А.Бабинец Корректор О. Билак ор Л. Кеви каз иал ППППатентф ф, г. Ужгород, ул. Проектна Тираж 756 ВНИИПИ Государств енног по делам изобретений 35, Иосква, Ж-З 5, Рауш

СмотретьЗаявка

2679896, 30.10.1978

ПРЕДПРИЯТИЕ ПЯ М-5339

КОНДРАТЬЕВ АНАТОЛИЙ ПАВЛОВИЧ, ПЕТУШКОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ЕЛИСЕЕВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: коррекцией, микрокоманд, микропрограммное, устройствоуправления, фектных

Опубликовано: 23.02.1981

Код ссылки

<a href="https://patents.su/5-807291-mikroprogrammnoe-ustrojjstvoupravleniya-c-korrekciejj-de-fektnykh-mikrokomand.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройствоуправления c коррекцией де фектных микрокоманд</a>

Предыдущий патент: Микропрограммное устройство управ-ления

Следующий патент: Устройство для обслуживания запросов

Случайный патент: Муфта для ступенчатого цементирования скважин