Процессор для сопряжения цвм с каналами передачи данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

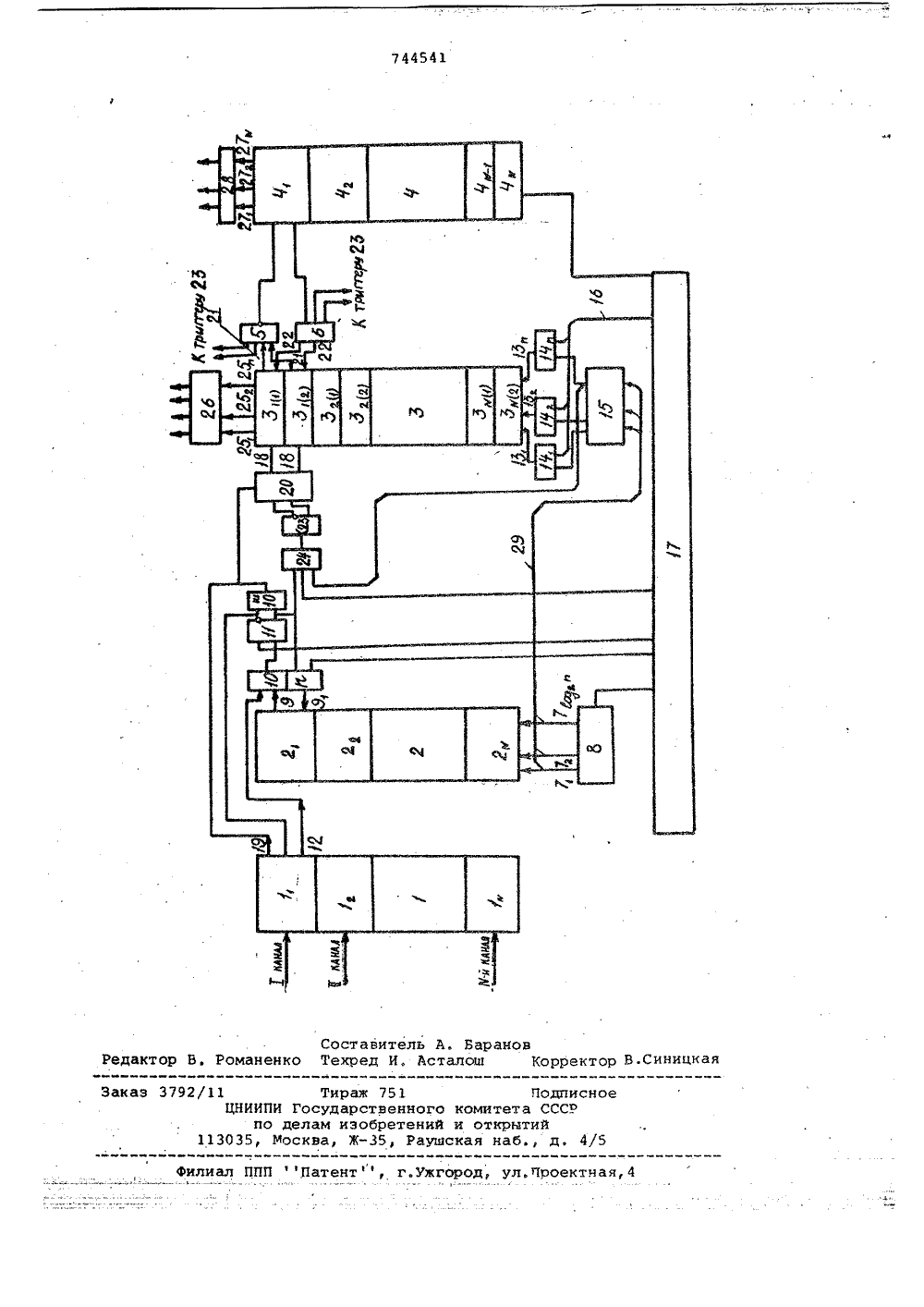

ОПИСАНИЕИЗОБМтЕНИЯ 74454 Союз Советских Социалистических Республик(22) Заявлено 130278 121) 2579689/18-24 (1)м2 С 06 Р 3/04 с присоединением заявки Ио(23) Приоритет Государственный комитет СССР по делам изобретений и открытийДата опубликования описания 300680(54) ПРОЦЕССОР ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ ММ 1 ИНЫ С КАНАЛАМИ ПЕРЕДАЧИ ДАННЫХИзобретение относится к вычислительной технике и предназначено для ввода в ЦВМ информации,поинимаемой по каналам передачи данных. 5Известно специализированное устройство, выполняющее Функции приема, анализа и выдачи в универсальную ЦВМ информации, принимаемой в виде дво-, ичных кодов по каналам передачи дан О ных, Это устройство, разработанное для сопряжения ЦВМ 1 Минскс каналами передачи данных, позволяет вести обмен информацией с 32 абонентами по телеграфным и телефонным ли киям связи. Оно содержит 32 линейных блока, предназначенных для побитной регистрации информации и побитной выдачи ее в каналы, а также гоупповое оборудование, включающее блоки 20 управления, сканирование линий, групповое,ооорудование Формирования и анализа знаков, оперативную память накопления знаков и блок выдачи данных в ЦВМ 111. 25Однако устройство Минск.имеет громоздкое индивидуальное оборудование каналов, выполненноЕ.с применением электромеханических реле, и низкую производительность, что ЗО связано с последовательным характером обслуживания каналов передачи данных.Наиболее близким по технической сущности к предлагаемому является мультиплексор, содержащий линейное оборудование 125 каналов и мультиплексор, осуществляющий сканирование линейных блоков, Формирование знаков и их анализ с целью выделения служебных кодов, а также управление обмена с мультиплексным каналом ЦВМ. Хранение накапливаемых знаков и всей управляющей информации каналов осуществляется в блоке оперативной памяти, где за каждым входящим каналом закреплен буфер на 2 знака, Для выполнения всех Функций, связанных с обслуживанием каналов, в схему введен специальный операционный блок, в котором осуществляется формирование и анализ принимаемых знаков при последовательном опросе каналов Г 21. Недостаток устройства заключается в низкой производительности и сложности оборудования, связанных с наличием в нем группового опера-. ционногоустройства, обслуживающего каналы путем их сканирования,Цель изобретения - сокращениеобъЕма оборудования и повышениебыстродействия устройства,Поставленная цель достигаетсятем, что в процессор для сопряженияциФровой вычислительной машины сканалами передачи данных, содержащийблок приема данных, блок управления,блок выдачи данных, счетчик разрядов,дешиФратор, шиФратор, регистр, групПу элементов ИЛИ, первую группу коммутаторон, вторую группу коммутаторов,причем входы блока приема данных являются входами устройства, входы блокавыдачи данных соединены с первой группой выходов коммутаторов первой группы, первая гоуппа выходов блока выдачи данных подключена к первойгруппе входов коммутаторов второйгруппы, вторая группа выходов блокавыдачи данных соединена со входамишиФратора, выходы которого являютсяпервой группой выходов процессора,а управляющий вход блока выдачи данных подключен к первому выходу блокауправления, второй выход которогоподключен ко входу счетчика, выходыкоторого соединены со входами дешиФратора, выходы которого подключены кперным входам элементов ИЛИ группы,вторые входы которых подключены ктретьему выходу блока управления, выходы регистра являются второй группойвыходов процессора, введены первый ивторой блоки ассоциативной памяти,четыре группы элементов И, группатриггеров совпадения, группа триггеров коммутации, третья группа коммутаторон, при этом первая группавыходов блока приема данных соединена с первыми нходами соответствующих элементов И первой группы, вторые входы которых подключены к выходам первого блока ассоциативной памяти, первая группа входов которогосоединена с выходамй счетчика, вторая группа выходов блока приема данных подключена к первым входам соответствующих элемечтон И второй груп-пы, выходы которых объединены с соответствующими выходами третьей группы выходов блока приема данных и подключены к первым входам коммутаторовтретьей группы, выходы которых со-,единены с первой группой входов второго блока ассоциативной памяти, первая группа выходов которого подключена к первым входам соответствующихкоммутаторов первой группы, вторыевходы которых объединены; с вторымивходами соответствующих коммутатороввторой и третьей групп и подключенык выходам соответствующих триггеровкоммутации группы, входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с выходами дешиФратора,вторые входы элементов И соединенй с четвертым выходом блока управления, а третьи выходы элементовИ третьей группы объединены с первыми входами элементов И четвертойгруппы, вторыми входами элементов Ивторой группы и подключены к выходамсоответствующих триггеров совпадения группы, первые нходы которых соединены с выходами элементов И первойгруппы, а вторые входы триггеров совпадения группы подключены к пятомувыходу блока управления, шестой выходкоторого соединен со вторыми входами элементов И четвертой группы, выходы которых подключены ко второйгруппе входов первого блока ассоциативной памяти, группа входов регист 15 ра соединена со второй группой выходов второго блока ассоциативной памяти, вторая группа входон которого соединена с выходами элементон ИЛИ группы, а третья группа входов второго2 О блока ассоциативной памяти подключенак выходам коммутаторов второй группы.На чертеже изображена структурнаясхема процессора.Устройство содержит блок 1 поразрядного приема данных (БПП) от И каналов с ячейками 11, 1, , 1 я (поодной ячейке на каждый канал); первый блок 2 ассоциативной памяти (БСР)с ячейками 21, 2, , 2, по 1 од 2,разрядов в каждой; второй блок 3 ассоциативной памяти(БНА) с ячейками31(,), 3,( 1,3(,), 3(,) (подне п-разрядных ячейки на канал) иблок 4 выдачи данных (БОВ) с ячейками 41, 4,4,,Каждая ячейка БОВ 4 соединена скоммутатором 5 первой группы и коммутатором б второй группы (на чертеже дано изображение для одного какала). Первый блок 2 ассоциативной .4 О памяти шинами 71, 77 ыопроса-записи подключен к выходамсчетчика 8 разрядов, а шина 9 совпадения каждой ячейки подсоединеначерез элемент 10 И первой группы кустановочному входу триггера 11 индикатора совпадения группы. Ча второйвход элемента 10 И подключен выход12 синхронизации соответствующегокакала БПП.Второй блок 3 ассоциативной памяти шинами, 131, 1313 и опросазаписи через элементы 144, 14 14ИЛИ группы подключен к выходам дешиФратора 15 номера разрядов. Вторые входы элементов 14(14 ИЛИ объеди 55 иены шиной 16 анализа знакон подключенной к блоку 17 упранления.Шины 18 разрешения записи каждойпары ячеек БНА 3 подключены к соответствующим инФормационным выходамбО 19 БПП через коммутаторы 20 третьейгруппы. Шины 21 совпадения каждойпары ячеек подключены к коммутатору5 первой группы, а шины 22 разрешения чтения - к коммутатору б нто 65 рой группы.Счетные входы триггеров 23 коммутации ячеек БИА через элементы 24 И третьей группы подключены к и-му выходу дешифратора 15 номера разрядов.Кроме того, блок БНА 3 шинами 25, 2525(т соединен с выходным ре: гистром 2 б, а блок БОВ 4 - шинами 27, 2727 с шифратором 28 номера читаемого знака.Входы дешифратора 15 номера разрядов шиной 29 соединены с выходами счетчика 8 разрядов первого блока 2 ассоциативной памяти.Устройство работает следующим образом.Блок 1 поразрядного приема данных фиксирует сигналы поразрядной синхро низации и информационных сигналов принимаемых разрядов по каждому каналу и хранит эти сигналы до их опроса в течение времени Топр =Тсчетй - , гдеоп р счет- В - скорость модуляции н канале. 2 ОНа ассоциативную память (АП) возлагаются подсчет разрядов принимаемых знаков по каждому каналу, Формирование знаков из принимаемых разрядов и их хранение до выдачи н ЦВМ, 25 анализ принятых знаков с целью выделения служебных кодов и отфильтровывания тех знаков, которые не передаются в ЦВИ (например, комбинации покоя или синхрокомбинации) . 30Первый блок 2 ассоциативной памяти осуществляет подсчет разрядов принимаемых знаков, для чего шины . опроса-записи этого блока подключены к счетчику 8 разрядов, работающему З 5 по модулю с тактовой частотой Га Вп,Шина 9 совпадения каждой ячейки 2 т, 22 подключены к триггеру 11 совпадения через элемент 10 И, на ее второй вход подается синхросигнал, О сопровождающий каждый бит принимаемой информацииЕдиничное состояние триггера 11 разрешает запись (по шине разрешения, записи) очередного состояния счет чика 8 разрядон в соответствующую ячейку 2, 22 н блока 2, чем и достигается решение первой задачи параллельно по всем каналам устройства за время одного цикла счетчика 5 О(Тсчет ВНакопление знаков и их анализ реализуются вторым блоком 3 ассоциативной памяти, в котором за каждым из И каналов закрепляется по две ячейки разрядности и. В одной иэ этих ячеек знак формируется, а во второй хранится, до выдачи в ЦВ(т.Запись принимаемых битов в некото. рый разряд второго блока 3 ассоциативной памяти разрешается в том случае, если триггер 11 индикатора совпадения И, первого блока 2 ассоциативной памяти при опросе ячейки счетчика разрядов этого блока установлен в единицу. Запись всех одноименных разрядов по всем каналам производится одновременно.Коммутация каждой пары ячеек одного канала второго блока 3 ассоциативной памяти осуществляется с помощью триггера 23, переключаемого посчетному входу сигналом с п-го выхода дешифратора 15 номера разрядов,если очередной знак по данному каналу полностью принят,Третья задача-анализ принятыхзнаков выполняется путем опроса этихзнаков кодом служебных комбинаций,подаваемым на шины 13, 13113,опроса-записи через элементы 14(,1414 ИЛИ, на вторые входыкоторых подключены выходы дешифратора 15 номера разрядов.При совпадении кодой, принятыхв ячейки памяти с кодом опроса, навыходах этих ячеек возникают сигналысонпадения, которые инвертируются ипоступают на входы БОВ 4 через комму,таторы 5, управляемые триггерами 23.БОВ 4 сигналы готовности знака Фиксируются и знаки ставятся в очередьна выдачу в ЦВМ.БОВ 4 содержит триггеры запоминания сигналов готовности знаков илогические элементы очередности ихвыдачи в ЦВИ, удовлетворяющие запросы на выдачу знаков, в соответствиис номерами каналов.Шифратор 28 номера читаемого знака подключен К выходам БОВ 4 для формирования номера знака, поступившегов данный момент в выходной регистр 2 бдля выдачи в ЦВМ.Блок 17 управления формирует сигналы управления всеми блоками процессора.Таким образом, работа процессора осуществляется в следующей последовательности: опрос БСР кодом номера раз. ряда (счетчик 8); запись очередного разряда знака в БИА, запись состояния счетчика 8 разрядов в БСР; переключение триггеров 23, опрос БЧА служебным кодом, добавление фединицы в счетчик 8; чтение очередного знака из БНАЯ гашение триггера 11 индикатора совпадения.Указанный цикл повторяется регулярно с периодом Т = рВппри этом осуществляется прием и анализ знаков по всем обслуживаемым каналам одновременно и последовательная выдача их параллельным кодом в ЦВИ.Предлагаемое устройство выигрывает в производительности и объеме оборудования. Отдельное операционное устройство в процессоре отсутствует. Управление предлагаемым устройством проще, чем связано с регулярностью и малым числом сигналов цикла управления. Производительность процессора характеризуется предельной скоростью передачи данных по каналам и744541 числом обФормула изобретениямаксимально допустимымслуживаемых каналов,ветсующих элементов И второй группы, выходы которых объединены с соответствующими выходами третьей группы выходов блока приема данных и подключены к первым входам коммутаторовтретьей группы, выходы которых соединены с первой группой входов второгоблока ассоциативной памяти, перваягруппа выходов которого подключенак первым входам соответствующих.коммутаторов первой группы, вторые входы которых объединены с вторыми входами соответствующих коммутатороввторой и третьей групп и подключенык выходам соответствующих, триггеровкоммутации группы, входы которых соединены с выходами элементов И третьей группы, первые входы которых соединены с выходами дешифратора, вторые входы элементов И соединены счетвертым выходом блока управления,а третьи выходы элементов И третьейгруппы объединены с первыми входамиэлементов И четвертой группы, вторыми входами элементов И второй группыи подключены к выходам соответствую"ших тригГеров совпадения группы,первые входы которых соединены с выходами элементов И первой группы, авторые входы триггеров совпадениягруппы подключены к пятому выходублока управления, шестой выиЬд которого соединен со вторыми входамиэлементов И четвертой группы,выходыкоторых подключены ко второй группевходов первого блока ассоциативнойпамяти, группа входов регистра соединена со второй группой выходов второго блока ассоциативной памяти, втораягруппа входов которого соединенас выходами элементов ИЛИ группы, атретья группа входов второго блокаассоциатквнрй памяти подключена к выходам коммутаторов второй группы. Источники информации,принятые во внимание при экспертизе1, Четвериков В.И. Преобразованиеи перецача информации в АСЧ. И.,Высшая школа", 1974.2. усольцев А, Г.и Кислин Б, П.Сопряжение дискретных каналов связис ЭВМ. М., Связь, 1973 (прототип).Составитель А. БарановРедактор В. Романенко Техред И, Лсталош Корректор В Снницк а лиал ППП Патент г.ужгород, ул,Проектная 3792/11 цнии п 113035, Тираж 75 Государстве елам изобре сква, Ж,Подписноеного комитета СССРений и откритийРаушская наб., д, 4/5

СмотретьЗаявка

2579689, 13.02.1978

ПРЕДПРИЯТИЕ ПЯ М-5308

СУЛИН ЛЕВ ИППОЛИТОВИЧ, АНТЮХОВ ВАЛЕРИЙ ИВАНОВИЧ, АЛЕКСЕЕВА СВЕТЛАНА ЛЕОНИДОВНА, ИПАТОВ МИХАИЛ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 3/04

Метки: данных, каналами, передачи, процессор, сопряжения, цвм

Опубликовано: 30.06.1980

Код ссылки

<a href="https://patents.su/5-744541-processor-dlya-sopryazheniya-cvm-s-kanalami-peredachi-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для сопряжения цвм с каналами передачи данных</a>

Предыдущий патент: Мультиплексный канал

Следующий патент: Устройство для многоканального сопряжения телеграфных каналов с электронной вычислительной машиной

Случайный патент: Способ установки зазора между торцами цапф оси баланса и накладными камнями