Устройство для моделирования конечных автоматов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 717775

Автор: Серебринский

Текст

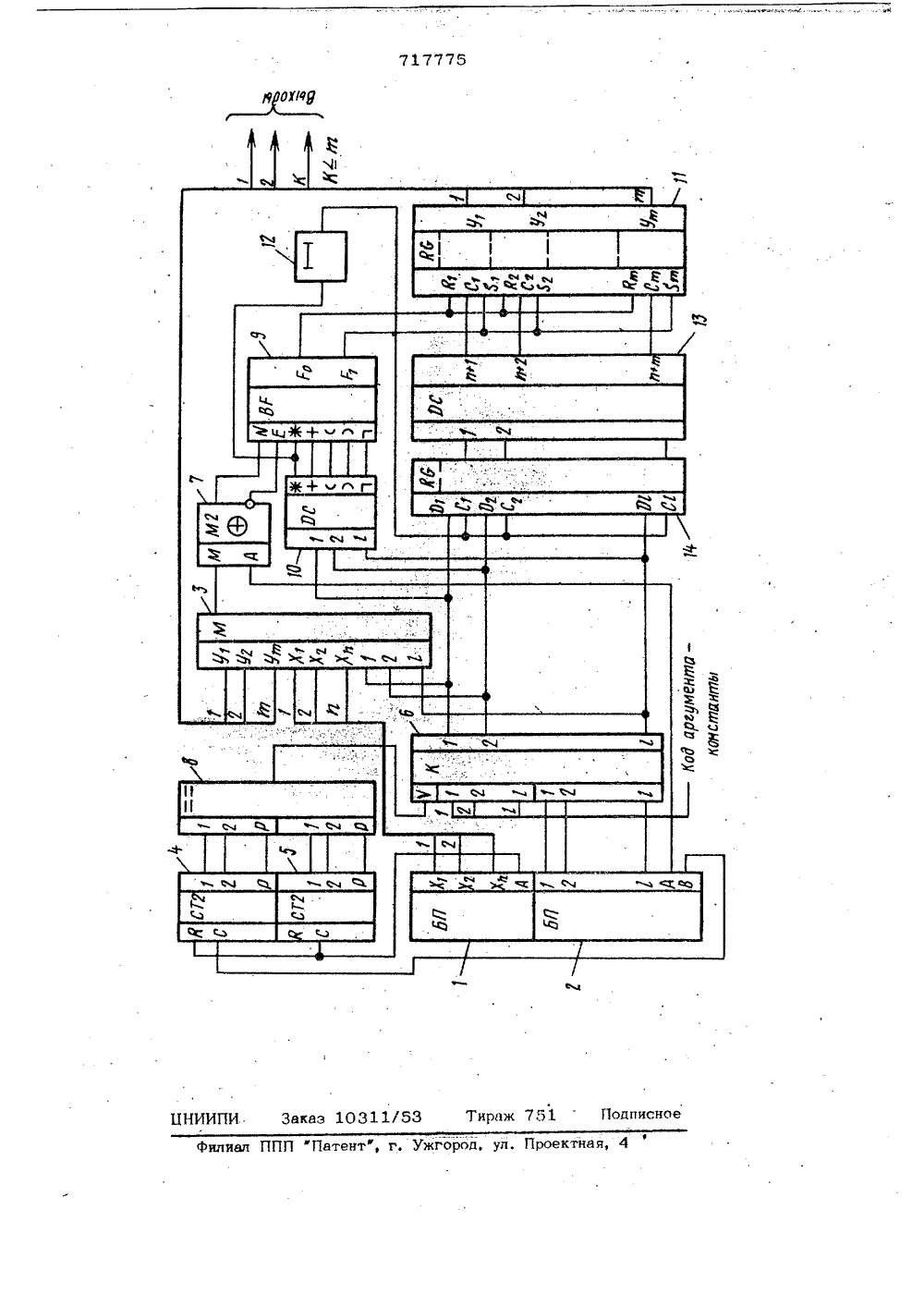

) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВ КОНЕЧНЫХ АВТОМАТОВ 20 1Изобретение относится к области вычислительной техники, а более конкретно к схемам ЦВМ и может быть ис пользовано при моделировании цифровых схем с целью их проверки и диа-. гностики.Известно устройство для моделирования логических схем содержащее блоки памяти, блок вычисления логи-. ческих функций, коммутаторы, элементы И, блок сравнения и блок управле- ниЯ 11,Недостатком известного изобретения является невозможность моделирования конечных автоматов, содержащих неисправности.Наиболее близким по техническому решению к предлагаемому является усчройство, содержащее первый блок памяти, мультиплексор, выход которого подключен к первому входу сумма- тора по модулю два, второй вход которого соединен с первым виодом первого блока памяти, лервьК и второй выходы сумматора по модулю два подключены к первому и второму вхоцамблока вычисления булевых функций,группа входов которого соединена свыходами первого дешифратора, первыйф регистр, выходы которого соединенысо входом второго дещифратора, второй регистр, выходы которого подключены к первой группе входов мульти-,плексора МНедостатком известного устройстваявляется сложность подготовительныхопераций, необходимых при моделировании неисправностей, возникающих вконечном автомате,15Цель изобретениярасширениефункциональных возможностей за счетмоделирования конечных автоматов сучетом неисправностей автомата,Поставленная цель достигается тем,что в устройство дополнительно введены второй блок памяти, коммутатор,ЗО дешифратор служебных символов 10, регистр внутренних переменных 11, эле- зБ мент задержки 12, дешифратор внутренних переменных 13, регистр функций 14,Устройство работает следуюшим образом.Моделируемый конечный автомат . 40 описывается в виде системы булевых функций.Эти функции должны быть представлены в форме, при которой знаки отрицания относятся либо только к одному 4 з аргументу, либо ко всему аналитическому выражению функции, знак равенства удаляется, а перед символом функции и в конце всей системы ставится символФЯНапример, система функцийУ 1 каях х хр)д х 4 фх будет представлена следующим образомЧ,х (кр +х,к )1 Ч Х+х ,/Записанная таким образом система функций кодируется позначно и вводится в блок памяти 2. В блок памяти 1 37177вый выход второго блока памяти подключен ко входу первого счетчика ик первому вхопу второго счетчика, второй вход которого соединен со вторымвыходом первого блока памяти, выхоцы5первого и второго счетчиков подключены ко входам блока сравнения, выходкоторого соединен с первым вхопом коммутатора, первая группа входов которо.го соепинена с входом устройства, вторая группа входов коммутатора соединена с выходами первого блока памяти, выходы коммутатора подключеныко второй группе вхопов мультиплексора, ко вхоцам первого дешифратора ик первой группе входов первого регистра, вторая группа шдов которого через элемент задержки соединена с первым выходом первого/ пешифратора, выходы второго дешифратора попключень 1к первой группе входов второго регист ра, вторая и третья группы входов которого соединены с первыми вторымвыходами блока вычисления булевых функций, группа выходов второго блоха памяти подключена к третьей группе вхоцов мультиплексора,Описываемое устройство представлено на чертеже. Оно содержит блокй памяти 1 и 2, мультиплексор 3, счетчики 4 и 5, коммутатор 6, сумматорпо модулю два 7, блок сравнения 8,блок вычисления булевых функций 9,75 4вводится массив, отражающий времен ную диаграмму входных сигналов моделируемого объекта в вине меняющихсяпеременных х,х х,При моделировании конечного автомата без неисправностей в блок памяти 1 вводится единица в разряде Апервого слом, а в блок памяти 2 вразряде В будут нули, При этом в начале моделирования счетчики 4 и 5устанавливаются соответственно в состояния ф 0 и 1, которые сохраняются до конца моделирования, т,е, до полного считывания блока памяти 1 Навыходе схемы сравнения 8 будет всевремя нуль и коммутатор 6 будет пропускать информашпо с блока памяти 2..Информация с блока памяти 2 будет поцаваться циклически, причем каждомуциклу соответствует одна итерация моделируемой схемы, Один или несколькоциклов блока памяти 2 соответствуютвыборке очередного слова блока памяти 1, При каждом цикле блока памяти 2 будет производиться вычислениезначений булевых функций, храняшихсяв нем, и для каждого набора аргументов будет вычислен набор значений функций, Это происходит следующим образом;Первый выведенный из блока памяти 2 символ ф буцет дешифрован дешифратором 10, который подаст сигналы на блок вычисления булевых функций 9 и элемент задержки 12, с выходакоторого задержанный сигнал запишетв регистр функций 14 код функции, следующий за знаком +, Код функциибудет дешифрован дешифратором внутренних переменных 13, и на соответствующий триггер регистра внутренних переменных 11 будет попая разрешающий впотенциал, т.е. будет аь."брана вычисляемая функция, Следующий за знакомфункции знак аргумента будет воздей.ствовать на мультиплексор 3 по вхо/дам 1, 2, ,. с и сбответствуюшее значение аргумента с одного из его вхо,пов, х 3 фх 2"хп 1 г "цщ будет1подано на выход мультиплексора 3,после чего поступит на вход М сумматора по модулю два 7. Одновременно будет подан разряд А с блока памяти 2 навход А сумматора по модулю два 7.Сравнение сигналов, поступивших навходы сумматора по модулю два 7 обеспечит подачу одного из сигналов Е илиК на входы блока вычисления булевыхфункций 9. Сигналы Е или И будут поБ6чего на выходе схемы сравнения 8 появится единица, которая будет подана на управляющий вход Ч коммутатора 6, в результате чего на выход коммутатора будет пропущен код аргумента-константы, т.е, код- одной иэ переменных, предварительно эафиксиромнных на нуле либо на единице на одном из входов Х,Х, к, у,у 2, Чмультиплексора 3. При дальнейшем выводе информации иэ блока памяти 2 счетчик 4 будет подавать на выход 1, 2,Р двоичные цифры 2, 3, 4,и т,д а счетчик 5 будет сохраняться в состоянии "1до окончания вывода информации из блока памяти 1, При этом на выход схемы сравнения 8 до конца считымния содержимого блока памяти 1 будет подаваться "Оф и коммутатор 6 будет пропускать йнформацию из блока памяти 2. В результате этого при первом цикле блока памяти 1 моделируется первая неисправность списка,хранящегося в блоке памяти 2, Второй,третий и дальнейшие циклы блока памяти 1 будут моделиромть вторую,Прй этом на выходах регистра внуЗОтренних переменных 11 будут формиразличных неисправностях, Эти временные диаграммы могут быть использованы для построения таблиц неисправностей, диагностических словарей илидля проверки полноты текстов. Устройство для моделирования конеч- ных автоматов благодаря наличию блоков и связей между ними позволяет труда при моделировании конечного автомата с неисправностями,Формула изобретения Устройство для моделирования конечных автоматов, содержащее первый блок памяти, мультиплексор, выход которого подключен к первому входу сумматора по модулю два, второй вход которого соединен с первым выходом первого блока памяти, первый и второй выходы сумматора по модулю два подключены к первому и второму входам блока вычисления булевых функций, группа входов которого соединена с выходами первого дешифратора, йервый регистр,71777являться на входах блока 9 каждыйраэ при считывании аргументов, и ихзначения являются результатом подстановки конкретных значений аргументов на входах мультиплексора 3 в ана-.литическое выражение функции, Кромеэтих сигналов на входы блока вычисления булевых функций 9 подаются сиРкалы + С,) р " с выходовдешифратора служебных символов в результате дешифрации кодов этих символов, Эти символы имеют следующиезначения: ф- символ стоящий передсимволом функции, порождающий сигналзаписи кода функции в регистр М, 15+ - символ дизъюнкции, С иЭ - сим-.волы скобок и 1 - символ отрицания,означающий отрицание функции и стоящий в конце аналитического выражения функции, Поданные в определенной 20последовательности сигналы Я,Е,+,+( э д 1 на входы блока вычислениябулевых функций 9 при выводе из блока памяти 2 аналитического выражения функции обеспечат вычисление конкретного значения функции блоком 9 ипоявление в результате одного иэ сигтретью и дальнейшие неисправности. палов Г, или г на его выходе. Этотсигнал запишет значение вычисленнойбулевой функции в один из триггероврегистра внутренних переменных 11. роваться временные диаграммы при Все следукйцие булевые функции будутвычислены аналогичным образом. Вычисленные значения булевых функцийподаются на входы мультиплексора 3 35Ц, Ч 2, , Ч,и могут участвоватьв дальнейших вычислениях. 3 результате многократного вычисления функций на выходах регистра внутреннихпеременных 11 формируется временная 40 существенно снизить затрать 1 ручного диаграмма выходных сигналов.Моделирование неисправностей конечного автомата происходит следующимобразомБлок памяти 1 заполняется так же, 45как при моделировании без неисправ-ностей. В блок памяти 2, кроме описания моделируемой схемы, вводитсясписок неисправностей в виде единиц вФразряде В, Первое считываемое словоблока памяти 1 установит счетчик 4в состояние фОф, а счетчик 5 отсчитает единицу в разряде А блока памяти 1. После этого начнется вывод информации блока памяти 2, При этомпервая моделируемая неисправность заданного списка в разряде В будет оъсчитана счетчиком 4, в результате7 71 выХоды которого соединены со входом второго дешифратора, второй регистр, выходы которого подключень 1 к первой группе входов мультиплексора, о тл и ч а "ю" щ е е с я.тем, что, с целью расширения функциональных возможнос-, тей за счет моделирования конечных автоматов с учетом неисправностей автомата, в устройство дополнительно вверены второй блок памяти, коммутатор, первый и второй счетчики, блок сравнения и элемент задержки, цричем первый выход второго блока памяти подключен ко входу первого счетчика и к первому входу второго счетчика, второй вход которого соединен со вторым выходом первого блока памяти, выходы первого и второго счетчиковподключены ко входам блока сравнения, выход которого соединен с первым входом коммутатора, первая группа входов которого соедйнена совходой уса. ройства, вторая группа входов коммутатора соединена с выходами первого блока памяти, выходы коммутатора 777 д8подключены ко второй группе входовмультиплексора, ко входам первого дешифратора и к первой труппе входовпервого регистра, вторая группа входовкоторого через элемент задержки соединена с первым выходом первого де шифратора, выходы второго дешифратора поаключейы к первой группе входоввторого регистра, вторая и третьяО группы входов которого соединены спервым и вторым выходами блока вычисления булевых функций, группа выходов второго блока памяти подключена к третьей группе входов мульти В плек сор а,Источники информациипринятые во внимание при экспертизе1, Авторское свидетельствоИд 471587, кл. С 06 Г 15/20,03.05.73,2. Авторское свидетельство СССР

СмотретьЗаявка

2464839, 21.03.1977

ПРЕДПРИЯТИЕ ПЯ В-8835

СЕРЕБРИНСКИЙ ВАЛЕНТИН ВИКТОРОВИЧ

МПК / Метки

МПК: G06N 7/06

Метки: автоматов, конечных, моделирования

Опубликовано: 25.02.1980

Код ссылки

<a href="https://patents.su/5-717775-ustrojjstvo-dlya-modelirovaniya-konechnykh-avtomatov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования конечных автоматов</a>

Предыдущий патент: Устройство для синхронизации вычислительной системы

Следующий патент: Устройство для вероятностного моделирования сложных систем

Случайный патент: Контейнер для выращивания растений