Преобразователь временных интервалов в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 683018

Авторы: Аксенов, Личидов, Трофименко

Текст

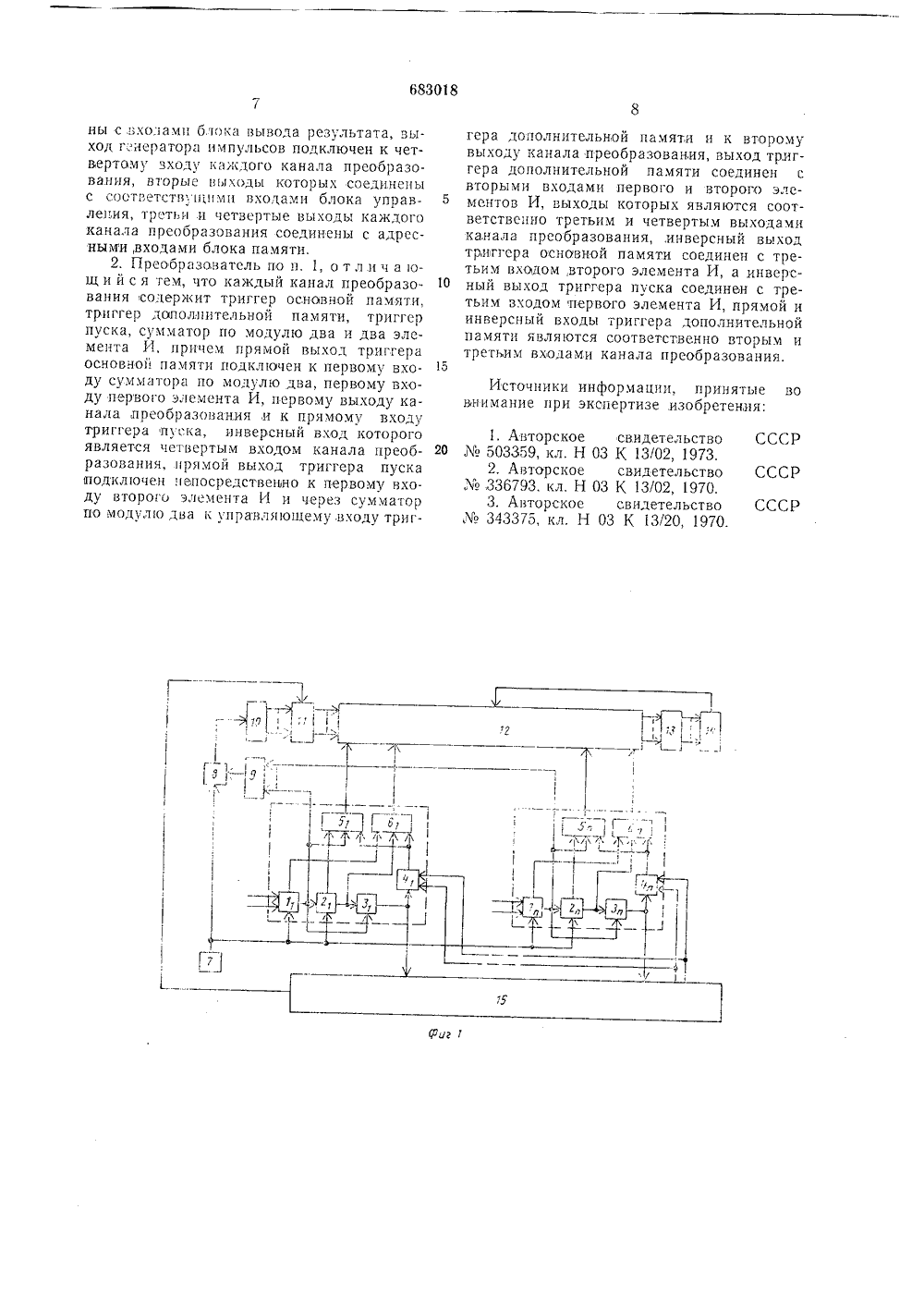

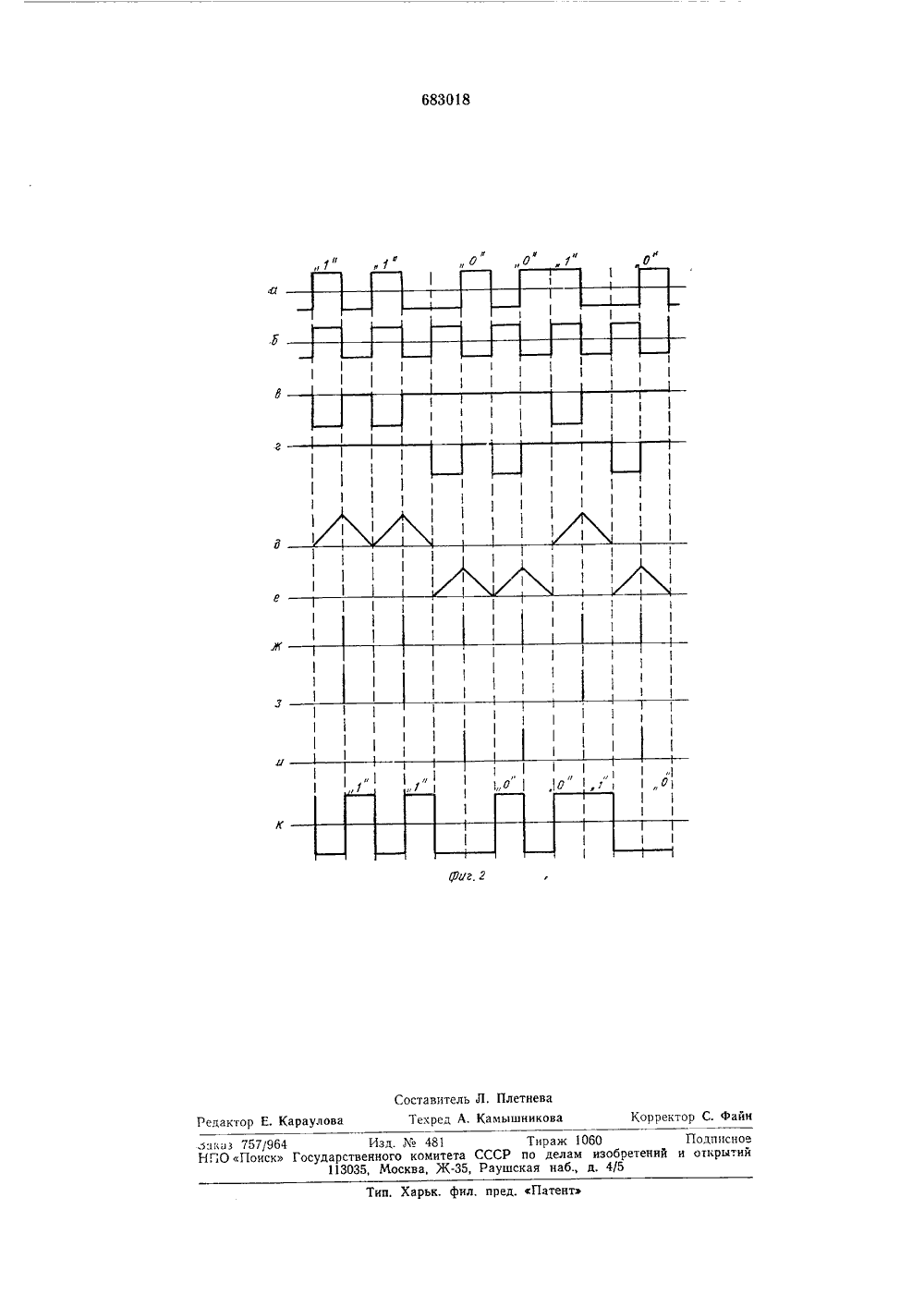

Союз Советских Социалистических Республик) Дата опубликования описания 31,08.79 СССРделам иэобретеии и открытий2 Изобретение относится к области вычислительной техники и может быть использовано в измерительных устройствах, в устройствах автоматики.и вычислительных устройствах,Известные преобразователи временныхинтервалов, позволяют лишь преобразовывать одиночные или периодически повторяюшиеся временные интервалы, поступающие от одного источника 11, 2.1 ОНаиболее близкое к изобретению техническое решение - преобразователь временных интервалов в код, содержащий в каждом канале триггер основной памяти, триггер пуска, триггер дополнительной памяти, 15а в групповой части - генератор счетныхимпульсов, ключ, счетчик, группу элементовИ, блок разрешения, схему блокировки,блок управления, блок памяти, блок вывода результатов преобразования 13. 20Недостатком известного преобразователя является то, что он не позволяет производить одновременные преобразования,входных сигналов от нескольких источников, у которых начало временных интервалов разнесено во времени относительнодруг друга. Это объясняется тем, что в нем,индивидуально оцифровываются в блокепамяти лишь моменты окончания,временных интервалов, а момент их начала дол- ЗО жен быть общим для всех интервалов, так как он фиксируется в преобразователе только исходным (нулевым) состоянием счетчика, Следовательно этот преобразователь позволяет производить лишь одновременное преобразование нескольких временных интервалов, связанных друг с другом общим начальным (пусковым) моментом, что сужает функциональные возможности известного устройства.Цель изобретения - расширение функциональных возможностей преобразователя.Указанная цель достигается тем, что в преобразователь временных интервалов в код, содержагций идентичные каналь 1 преобразования по количеству одновременно преобразуемых временных интервалов, генератор импульсов, выход которого подключен непосредственно к первому входу каждого канала преобразования и через илюч к входу счетного блока, выходы которого через блок элементов И соединены с информационным;: входамн блока памяти, управляющий вход которого подключен к входу блока вывода результата, блок управления, первый выход которого подключен к управляющему входу блока элементов И, второй и третий выходы блока управления соединены соответственно с вторыми и третьимп входами каждого канала преобразо 6830185 10 15 20 25 30 35 40 45 50 55 00 05 вания, первые выходы которых через блок разрешения подключены к одному из ходов ключа, дополнительно введен блок вычитания, ходы которого подключены к ыходам блока памяти. Выходы блока вычитания .поразрядно соединены с входами блока вывода результата, Выход генератора,импульсов подключен к четвертому ходу каждого канала преобразования, вторые выходы которых соединены с соответстзующими входами блока управления, Третьи и четвертые выходы каждого канала преобразования соединены с адресными входами блока памяти.Кроме того, каждый канал преобразоания содержит триггер основной памяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И. Прямой выход триггера основной памятя подключен к первому входу сумматора по модулю два, первому входу первого элемента И, первому выходу канала преобразования и к прямому входу триггера пуска, инверсный вход которого является четвертым водом канала преобразования. Прямой выход триггера пуска подключен непосредственно к первому входу второго элемента И и через сумматор по модулю два к управляющему входу триггера дополнительной памяти и к второму выходу канала преобразования. Выход триггера дополнительной памяти соединен с вторыми входами первого и,второго элементов И, выходы которы.; являются соответственно третьим и четвертым выходами канала преобразования. Инверсный выход триггера основной памяти соединен с третьим входом второго элемента И, а инверсный выход триггера .пска соединен с третьим входом пьерого элемента И. Прямой и инверсный входы триггера дополнительной памяти я- ляются соответственно вторым и третьим входами канала преобразования.На фиг. 1 приведена структурная схема предлагаемого преобразователя; на фиг.2 - временная диаграмма его работы.Преобразователь содержит входную часть, разбитую на и независимых каналов (по числу временных интервалов), и групповую часть. На фиг. 1 ооозначены входы, на которые поступает сигнал, соответствующий началу одного из преобразуемых временных интервалов, входы, на,которые поступает сигнал, соответствующий концу одного из этих интервалов, триггеры 1 ь, 1 осноной памяти, триггеры 2 2 пуска, информационные входы которых подключены к прямым выходам соответствующих триггеров основной памяти, логические элементы 3, Зсложения по модулю да, входы которых связаны с прямыми выходами триггеров основной памяти,и триггеров пуска, а выходы с информационными входамн триггсро 4, 4 дополнительной памяти, прямыс выходы последнего связаны с соответстующими входами элементов И 5 , 5 и 6 ь,6Групповая часть преобразователя содержит генератор 7 счстных импульсов, ы.ход которого соединен с одним из входов ключа 8 и с синхронизирующими входами триггеров основной памяти и триггеров пуска всех, каналов, другой вход ключа подключен к выходу блока 9 разрешения, входы которого связаны с прямыми выходами всех триггеров основной памяти, Выход (люча под(лчен ( счетном) вход счетно о блока 10, выходы которого через элемент И 11 соединены с информационными входами блока 12 памяти, адресные ходы которого подключены к выходам соответствующих элементов И 5 5,и элементов И 6, 6, а информационные выходы блока 12 памяти через вычитатель 13 соединены с входами блока 14 ыода результатов преобразования, уираляющнй выход которого подключен к управляющему входу блока памяти, Входы блока 15 управления связаны с выходами логических элементов сложения по модулю два, а один из входов блока управления соединен со стробирующими входами группы элементов И 11, два других выхода блока управления подключены к соответствующим синхронизирующим входам всех триггеров дополнительной памяти.Преобразователь работает следующимобразом.Пусть на один,из входов триггера основной памяти, например, первого канала поступил сигнал, соответствующий началу первого временного интервала. По первому счетному импульсу с генератора 7 он фиксируется в триггере 1, основной памяти, С появлением на прямом выходе триггера 1 основной памяти высокого уровня напряжения блок 9 разрешения переключается, формируя на выходе сигнал управления ключом 8. С этого момента последующие счетные импульсы с выхода генератора 7 начинают поступать через ключ 8 на вход счетного блока 10.Одновременно с момента фиксации втриггере 1 основной памяти сигнала о начале данного временного интервала на выходе логического элемента З сложения по модулю два начинает формироваться сигнал пуска, который поступает на информационный вход триггера 4 дополнительной памятии на вход блока 15 управления, По этому сигналу блок 15 управлечия вырабатыает три управляющих импульса. Первый уираляющий импульс этой серии фиксирует сигнал пускатриперс 4 дополнительной памяти. На его прямом ыходс поя- ляется сигнал с высоким уронем напряжения, который через элемент 5 поступает на адресный вход блока 12 памяти как сигнал освящена к РО лпгг.гл чл,.1 О 20 25 зо 35 15 40 45 50 55 60 65 памяти, подготавливая их к приему исходного, кода со счетного блока 10.Второй управляющий импульс (импульс записи), сформированный блоков 15 управлеция поступает на стробируюший вход элсмсцтя Й 11 и осуществляет запись исходного кода счетчика 10 (т. е. производится оцифровка принятого сигнала о начале дан;ого временного интервала) в,выбранные ячейки блока 12 памяти. Третий управляющий импульс этой серии поступает на вход сброса триггера 4, дополнительной памяти, переводит его в исходное состояние и прекращает тем самым действие сигнала обраценця к блоку 12 памяти.С приходом второго счетного импульса с выхода генератора 7 триггер 2, пуска переходит в единичное состояние, что вызывает прекращение сигнала пуска на выходе логического элемента 3, сложения по модулю два. Одновременно с этим счетный блок 10 подсчитывает поступающие на его вход счетные импульсы.Аналогично происходит процесс оцифровки приходящих сигналов о начале временных интервалов и по л 5 обому другому каналу, т. е. какдый раз в момент выработки сигнала обращения к блоку 12 памяти в соответствующие его ячейки записывается текущий код счетного блока 10,Пусть теперь в определенный момент времени на другой вход триггера основной памяти (например, первого канала) посту- лает сиггнал об окончании данного временного интервала. Очередным счетным импульсом с выхода генератора 7 он фиксируется в триггере 1, основной памяти, что вызывает появление на прямом его выходе низкого уровня напряжения. При этом на выходе логического элемента 3 сложения по модулю два вновь выделяется сигнал луска, а блок 15 управления вырабатывает очередную серию управляющих импульсов, по,которым триггер 4, дополнительной памяти формирует сигнал обращения. Последний поступает на адресный вход блока 12 памяти (в данном случае через элемент б) и в соответствующие ячейки его памяти записывается текущий код счетного блока 10, который соответствует сигналу,об окончании данного временного интервала. Последующим счетным импульсом с выхода генератора 7 триггер 2, пуска переходит в нулевое состояние, что вызывает прекращение сигнала пуска на выходе логического элемента 3 Сложения по модулю два.Аналогично проходит процесс оцифровки приходящих сигналов Об окончании временных интервалов и по любому другому каналу, причем с приходом сигнала об окончании последнего из преобразуемых временных,интервалов и фиксации его в соответствующем триггере 1 основной памяти блок 9 разрешения переключается в исходное состояние и запрещает прохождение через ключ 8 счетных импульсов на вход счетного блока О. На этом заканчивается процесс оцифровки всех поступающих сигналов о начале и конце преобразуемых врехец 5 ых интервалов.Далее с помоЦьк, блоа 14 вывода результатов преобразования осуществляется процесс последовательного счцтыванця из ячеек блока 12 памяти в блок вычггацця 13 кодов, соответствующих онцу ц началу первого временного интервала. В блоке вы- и 5 яния 13 путем Вы 5 итянця этих ОЦОБ 011- ределяется ооцчательый результат преобразования первого временцого интервала в код и счцть 5 ванпе его в блок 14 вывода результатов преобразования. Зятем определяется кол преобразования второго временного интервала, третьего и тя далее до и-го временного интервала. После вычислений и преобразований в ол Всех временных интервалов осуществляется устяцовка с 5 етного Олок; 16 В цсхолцОс сос 10 яцце и ЦИКЛ РЯООТЫ ПРЕООРЯЗОВЯТЕЛ 5 ВНОВЬ ПОВТО- ряется.Предлагаемый преобразозатель Временных интервалов В од за счет обеспечения для кажлого из независимых каналов по- СЛЕДОЗЯТЕЛЬНОЦ ОЦИфРОВИ 5 ЯСЦГНЯЛЯ, СО- ответств 5 ощего цаЯлу време:ного интервала, так и сигнала, соопве 1 ству 5 ошего его концу, и послелуюшего нахождения с помощью вычитателя кола их разности. который является искомым колом преобразуемого времечного интервала, позволяет расширить фунцлональныс возможностц данно- ГО преоорязовятел 5 по с 5 яв 1 ЯниО с известнь.м. Формула изобретения 1. Преобразозатель временных ит 5 тервалов в ол, содержащий цдецгцчные каналы преобразования по колич ству олцоврсмецно преобразуемых Временных интервалов, генератор импульсов, выход которого подключен непосредственно к первому входу каждого канала преобразования ц через ключ к входу счетного блока, 15 ыходы которого через блок элементоз И соединены с информационными входамц блока памяти, управляющий вход которого подклцочец к входу блока вывода результата, блок управления, первый выход которого подключен к управляющему входу блока элементов Ивторой и третий выходы блока упраВления соединены соответственно с Вторыми,и третьими входамц каждого канала преобразования, первые Выходы которых через блок разрешения подключены к одному из входов ключа, о т л и ч а ю щл й с я тем, что, с целью расширения функпцанальных возможностей, в него лопол 55 ительно введен блок вы питания, входы которого подклОчены к выходам блоя памяти. выходы блока вычитания поразрядно соединены с входамп блока вывода результата, зыход г:.нсратора импульсов подключен к четвертому входу каждого канала преобразовапия, вторые выходы которых соединены с соответств; гцпми входами блока управления, третьи,и четвертые выходы каждого канала преобразования соединены с адресными, входами блока памяти.2. Преобразователь по и, 1, о т л и ч а ющ и й с я тем, что каждый канал преобразования содержит триггер основной памяти, триггер дополнительной памяти, триггер пуска, сумматор по модулю два и два элемента И, причем прямой выход триггера основной памяти подкл 1 очен к первому входу сумматора по модулю два, первому входу первого элемента И, первому выходу канала лреобразования,и к прямому входу триггера пуска, инверсный вход которого является четвертым входом канала преобразования, прямой выход триггера пуска аодкл 1 очен непосредственно к первому входу второго элемента И и через сумматор по модулю два к управляющему, входу триг 1. Авторское свидетельство 20503359, кл. Н 03 К 13/02, 1973. 2, Авторское свидетельство,336793. кл. Н 03 К 13/02, 1970. 3. Авторское свидетельство343375, кл. Н 03 К 13/20, 1970.СССРСССРСССР гера дополнительной памяти и к второму выходу канала преобразования, выход триггера дополнительной памяти соединен с вторыми входами первого и второго элементов И, выходы которых являются соответственно третьим и четвертым выходами канала преобразованияинверсный выход триггера основной памяти соединен с третьим входом, второго элемента И, а инверс ный выход триггера пуска соединен с третьим входом первого элемента И, прямой и инверсный входы триггера дополнительной памяти являются соответственно вторым и третьим входами канала преобразования.15Источники информации, принятые вовнимание при экспертизе изобретения:683018 1Составитель Л. Плетневааулова Техред А. Камышникова Корректор С. Фа ктор Е Т рьк. фил. пред. Патент лзказ 757/964 Изд.481 Тираж 1060 ПодписноеНПОПоиск Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2457141, 01.03.1977

ПРЕДПРИЯТИЕ ПЯ Г-4812

ЛИЧИДОВ ЮРИЙ ЯКОВЛЕВИЧ, ТРОФИМЕНКО ВАЛЕРИЙ ГРИГОРЬЕВИЧ, АКСЕНОВ БОРИС ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03K 13/20

Метки: временных, интервалов, код

Опубликовано: 30.08.1979

Код ссылки

<a href="https://patents.su/5-683018-preobrazovatel-vremennykh-intervalov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь временных интервалов в код</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Устройство коммутации и защиты источника напряжения

Случайный патент: Состав для предотвращения и ликвидации гололеда на дорогах