Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

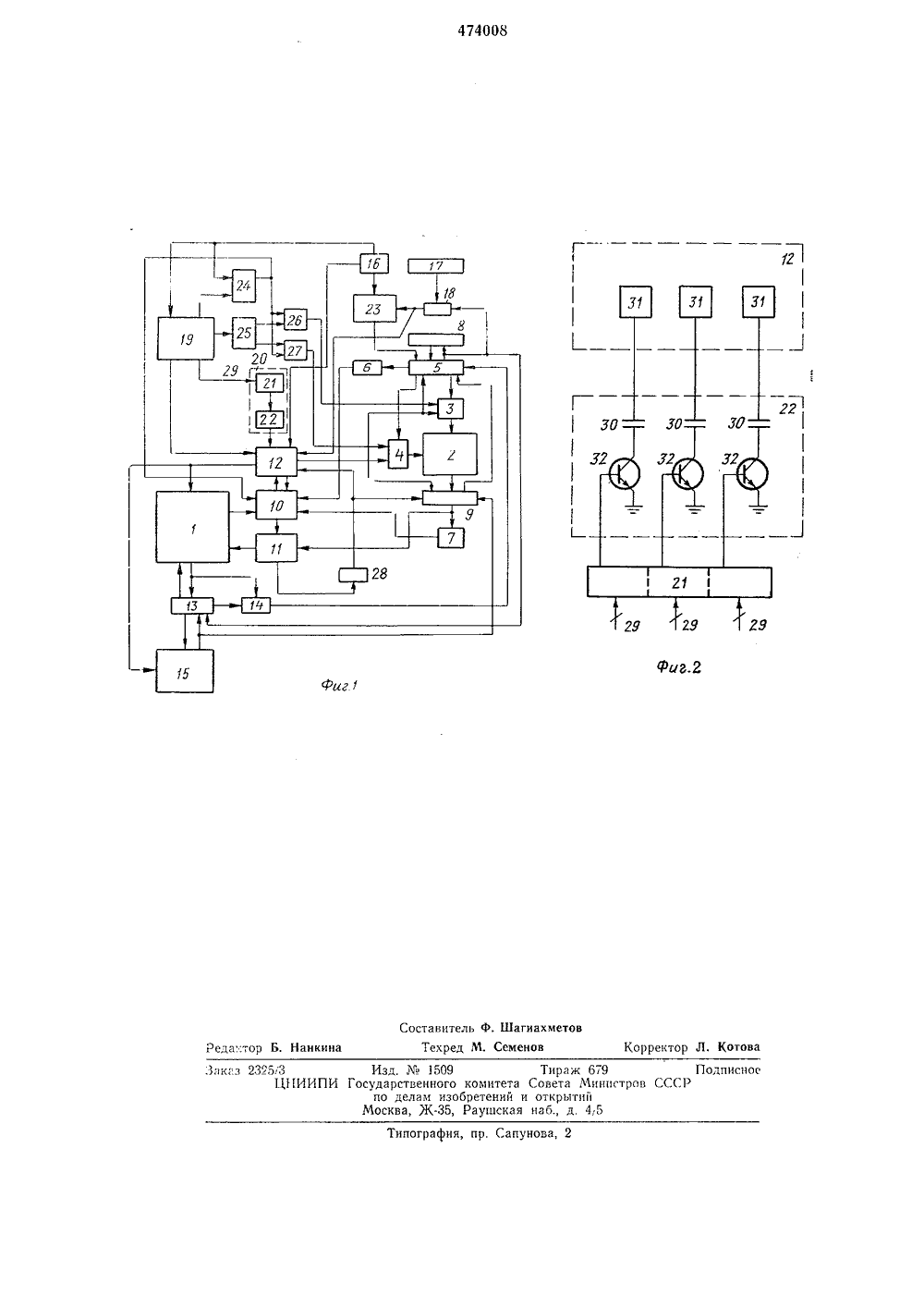

1 474008 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Соцйалистииесиих Реслбл и(О 1) Ч. Кл. 6 06 9,126 06 11,00 с присоединением заявки М Государственный комитетСовета Министров СССРоа делам изобретенийи открытий(54) МИКРОПРО 1 Р.дММНЫЙ ПРОЦЕССОР Изобретение относится к области вычислительной техники и, в частности, к организац 11 диагностического контроля микропрограммного процессора.Известен микропрограммнь 1 й процессор, включающий арифметико-логический блок, связанный с запоминающим блоком, блок контроля, выходы которого соединены с первыми входами блока синхронизации и блока дешифрации микрокоманд, блок управления диагностикой, первый выход которого соединен со вторым входом блока синхронизации, узел контроля четности, блок запоминания микрокоманд, связанный с первым входом регистра микрокоманд, с выходами дешнфраторов горизонтальных и вертикальных шин, соответствующие входы которых соединены с выходами блока синхронизации, адресного регистра блока запоминания микрокоманд и выходами горизонтального и вертикального вентилей блокировки, причем вход блока управления диагностикой соединен с одним выходом переключателя ре 5 кимов, другой выход которого соединен с третьим входом блока синхронизации, первый выход блока и дешифрации микрокоманд соединен со входом арифметико-логического блока, соответствующий выход которого соединен с первым входом блока контроля, второй вход которого через узел контроля четности соединен с выходом регистра мнкрокоманд и вторым входом блока дешифрации мнкрокох 31 д.Недостаток известного м кропрограммногопроцессора закспочается в том, что автоматн ческая диагностика аппаратуры требует больших затрат оборудования.Цель нзобретсшя - упрощение процессора.Поставленная ц;ль досп 1 гастся тем, чтомикропрограммьй процессор содержит блок 10 изменения длительности импульсов, трнггерьперексночения выооркп, инверсии контроля н инверсии блокировки, причем входы триггера инверсии контроля сосднеь. со входом н вторым выходом Олока управле 1 ня д,1 гостн кой, третий вьход которого соедисн с однимиз входов триггера инверсии блокировки, выходы которого соеднены с первымн входамн горизонтального и вертикального вентилей ОлокнрОВкн, вторые Входы коОрь 1 х соединены 20 с одним нз выходов триггера инверсии ко 1 проля и с третьим входом блока ксштроля, чст- вертыЙ выход бл 01:,аравлення днагнос-ко 1 через Олок изменен 5 длительности импульсовов соединен с четвертым входом блока снн хроннзацни, пятый вход которого соедг 1 ен совторым входом регистра мнкрокоманд и через триггер перекл 10 чення выоорки - со Вторым выходом блока дешифрации мцкрс команд, а третий ьход регистра мнкрокоманд ЗО соединен с выходом запомнающего блока.3Блок-схема микропрограммного процессора предсГавлеца ца фиг. 1; ца фиг. 2 приведе)1 схема блока изменения длительности имИУльсОВ,Микропрограммный процессор (фиг. 1) содержит арифметико-логический блок 1, блок2 запоминания микрокоманд, дешифратор 3горизонтальны.( Гцин, дешифратор 4 вертильцых шиц, адресный регистр 5 блока запоминания мцрокоманд, узлы 6, 7, контролячетости, адресный регистр 8 повтора микроО)ацд, регистр мцкрокоманд 9, блок контро,1 Я 10, ОлО 11 дешифрации микрокОмацд,блок синхронизации 12, регистр 13 запоминакпцего блока, схему сравнения 14, запоминаюццй блок 15, переключатель режимов 16, рег)ц:тр лючей 17 остацова по адресу, схемуср н.цц 18 регистра лилей, блок 19 управлсшя диагцостцой, блок 20 изменения длительности импульсов, регистр 21, схему 22 изменения длительности импульсов, блок 23 зацикливания микропрограмм, триггер 24 инверсии контроля, триггер 25 инверсии блокировки, горизонтальный вентиль блокировки26, вертикальный вентиль блокировки 27, триггер 28 переключения выборки, шины 29 регулцровц длительности,Н)1 фиг, 2 обозначены; 30 - конденсаторы;31 -- формирователи; 32 - транзисторы.Микропрограммный процессор работает следующим образом.Все преобразования информации при работе процессора выполняются в арифметикологическом блоке (АЛБ) 1. В процессоре использован микропрограммный принцип управления. Управляющие слова 1 микрокоманды) хранятся в блоке 2 запоминания микрокоманд, представляющем собой постояннуюпамять с матричной выборкой. Разрядностьуправляющего слова совпадает с разрядностью команд и информационных слов процессора,Выбор определенного управляющего словапроизводится с помощью дешифратора 3 горизонтальных шин и дешифратора 4 вертикальных шин, соединенных с младшими истаршими разрядами адресного регистра 5блока запоминания микрокоманд. Передачиинформации в адресный регистр блока запоминания микрокоманд контролируются по четности с помощью узла 6 контроля четности,Выполнение текущей микрокоманды совмещено с выборкой следующей микрокомандыцз блока 2 запоминания микрокоманд.Перед образованием адреса очередного управляющего слова в адресном регистре 5блока запоминания микрокоманд его содержимое передается в адресный регистр 8 повтора микрокоманд. В случае обнаружениясбоя при выполнении микрокоманды содеркимое адресного регистра повтора микрокомандпередается в адресный регистр блока запомицация микрокоманд, и повторяется выполнечпе мпкрокоманды, в которой обнаруженсбой,5 10 15 20 25 30 35 40 45 50 55 60 65 4Мик 1 эоком анды выбираотс 51 В регистр иик- рОомацд 9 и коцролируютс 5 ИО 1 стцости с помощью уз,А 7 коцтрО 151 стцос ц. Г 1 ри этОм все управляющие слова цме)от Очетш)с число единиц.ВыхОды узлов 6 и 7 коцтро;я четцОстц, а также выход схемы контроля АЛБ 1 соединяются с блоком контроля 10, который осуществляет синхронизацию коцрол 51, фцсирует сбои и управляет ре)кимами работы процессора при сбоях и отказах.Группа младших разрядов рш истра микро- команд 9 перед выборкой следующей микро- команды передается в младшие разряды адресного регистра 5 блока запоминания мцкроком анд.При вьполпенни микрос)мацд бло 11 Дешифрации микроома цд дсодцр ет состояние уцрвляющцх полей регисгра микро- команд 9 и вырабатывает уровц управления для выполнения полного цабора микрокоманд процессора,Блок синхронизации 12 вырабатывает сицхроцизирующие последовательности для работы АЛБ 1, блока 2 запоминация микрокоманд и запоминающего блока 15. Обмен информацией с запоминающим блоком 15 производится через регистр 13 запоминаюнего блока, который может быть связан с любым регистром АЛБ 1.Схема сравнения 14 производит сравнение информации в регистра 13 запоминающего блока и ца выходной шине АЛБ 1. Выход схемы сравнения 14 соединен с младшим разрядом адресного регистра 5 блока запоминания микрокоманд и используется для ветвления микропрограмм при работе процессора и в процедурах диагностики.Режимы работы процессора задаются с переключателя режимов 16. Имеются следующие режимы работы:1) рабочий;2) с остацовом по адресу микрокомацды;3) с остацовом по сбою;4) диагностики;5) зацикливани 51 5 Икропрограм;51,В рабочем режиме процессор автоматически выполняет текущие команды программы. При обнаружении отказа производятся переход в ловушку и программная обработка информации об отказе.Режим с остановом по адресу микрокомацды используется при отладке и для облегчения ру)цой диагностики. Для реализации этого режима на пульте управления имеется регистр ключей 17 остацова по адресу, с помощью которого набирается адрес блока 2 запоминания микрокоманд, после выборки из которого мик рокомацды необходим останов.После того, как адрес в адресном регистре 5 блока запоминания микрокоманд совпадает с содержимым регистра ключей 17 останова по адресу, схема сравнения 18 возбудит блокирующий сигнал, который остановит синхроцизирующуО последовательность блока запо 4740085минанц 51 м 1 к 1)окомацд в блоке с 11 цхроццзс 1 - ции 2.В режиме остацова по сбою сигнал с иереклочателя режимов 16 блокирует работу блока синхронизации 12 прц наличии сгц:15 а сбоя из блока контроля 10.В предлагаемом устройстве автоматическая диагностика охватывает блок 2 запоминания микрокомацд с дешцфраторамц горизонтальных и вертикальных шиц 3, 4, адресный регистр 5 блока запоминания микрокоманд, регистр микрокомацд 9 с узлом 7 контроля четности, блок синхронизации 12, часть блока контроля 10, часть блока 11 дешифрации микрокомацд и регистр 13 запоминающего блока со схемой сравнения 14.В режиме диагностики переключатель режимов 16 включает блок 19 управления диагностикой и устанавливает в единицу триггер 24 инверсии контроля.Одной из наиболее трудных областей для диагностики является блок синхронизации, так как отказы формирователей импульсов, особенно те, которые приводят к уменьшению длительности импульсов и увеличению частоты времецных последовательностей, чрезвычайно трудно поддаются автоматической локализации.В предлагаемом устройстве в начальной стадии диагностики блок 19 управления диагностикой по шинам 29 регулировки длительности сбрасывает в О все триггера регистра 21 изменения длительности импульсов. При этом включаются все транзисторы 32 блока 20 изменения длительности импульсов и конденсаторы 30 подсоединяются к земле 1 фиг. 2).Конденсаторы 30 подключены к времязадающим цепям формирователей импульсов 31 блока синхронизации 12. Когда транзисторы 32 выключены, конденсаторы 30 отсоединецы от земли, и формирователи импульсов 31 вырабатывают временные последовательности, соответствуощце номинальной скорости раооты процессора. Когда какой-либо из транзисторов 32 включен, оц подсоединяет к земле соответствующий конденсатор 30, ц длл одного из устройств процессора вырабатывается временная последовательность пониженной частоты. Таким образом, в начальной стадии диагностики блок синхронизации 12 вьрабатывает для всех устройств процессора временные последовательности пониженной частоты.Диагностика начинается с диагностики коротких замыканий в дешифраторах горизонтальных и вертикальньх шин 3 ц 4 блока 2 запоминания микрокоманд. При этом устанавливается в 1 триггер 24 инверсии контроля и триггер 25 инверсии блокировки, которые включают горизонтальный вентиль блокировки 26, Кроме того, триггер 24 инверсии контроля инвертирует контроль блока запоминания микрокоманд в блоке контроля 10, т. е. считывание слов с четным числом единиц считается правильным, а с нечетным - ошибочным. 5 10 15 20 25 30 35 40 45 50 55 60 65 6Блок 19 управления диагностикой зац 1(к:. От в блоке сицхронцзации 12 времецнуО последовательность блока 2 запоминания микро- команд ц после каждого обращения 5 О 611 НГ 5 с единицу к адресному регистру 5 блока зацоминдни 51 мцкр 01(оман Выполцл 51, акцм ОР- разом, сканцровацце блока запомццаццл мцкрокоманд. После полного цикла сканиронания триггер 25 инверсии блокировки сорасываетсл в О, горизонтальный вентиль бгОкцровкц 26 выключается, включается вертикальный вентиль блокировки 27 и производится сканирование блока 2 запоминания мпкро(омацд с О 1- ключенным дешцфратором 4 вертикальных шин.В данных режимах, если нет коротких за мыканий в дешифраторах горизонтальных и вертикальных шин 3 и 4, цз блока запоминания микрокоманд должна счцтыватьсл нулевая (четная) информация. В случае считывания нечетной информации временная последовательность блокируется, ц по состоянию триггера 25 инверсии блокировки и информации в регистре микрокоманд 9 определяется, в каком из дешифраторов горизонтальных и вертикальных шин 3, 4 произошло короткое замыкание.После прохождения двух циклов сканирования триггер 24 инверсии контроля сбрасывается в О, ц производится сканирование блока 2 запоминания микрокомацд со считыванием и контролем реальной информации. При останове по сбою содержимое адресного регистра 5 блока запоминания мцкрокомацд и регистра микрокомацд 9 сигнализирует место неисправности.После успешного завершения одного цикла сканирования блок 19 управлешл диагностикой устанавливает в 1 соответствующий триггер в регистре 21 изменения длительности импульсов, который через схему 22 цзмсцс 1 цл длительности импульсов устанавливал номинальную временнуо последовательность блока 2 запомццацп 5 мцкроком 51 цд в б,О 1(е сццхронизацци 12.После этого запускаетсл е 1 це Од 11 П цпк,1 ск 1- пирования.Сканирование блока запоминания мцкрокоманд завершаетсл считыванием по фцксцрованному адресу информации с 1 ецравильцой четностью 1 четной), чтобы проверить функ. ционировацие узла 7 контроля четности ц схемы фиксации сбоя блока запоминания мцкрокоманд в блоке контроля 10.После завершения диагностики блока 2 запоминания микрокоманд осуществляетсл переход к микропрограммной диагност;Не, выполняемой в два этапа. На первом этапе дц 11.Постические микропрограммы, выбираем с из блока запоминания микрокоманд, производят диагностику всех регистров и триггеров процессора. На втором этапе Пагцостц 1 сс(Ие микропрограммы, выбираемые цз запомцц 5 ПО щего блока 15, производят дцачОстцку ком бцнационной логики.5 10 7Первый этап микропрограммной диагностики производится методом раскрутктт, начиная с регистра 13 запоминатощего блока и постепенно захватывая регистры и триггеры АЛБ 1.Диагностика проводится обычными методами с использованием для локализации неисправностей диагностических словарей остановов.Первый этап микропрограммной диагностики проводится сначала с временной последовательностью АЛБ 1 пониженной частоты. При успешном завершении этого подэтапа блок 19 управления диагностикой через соответствующий разряд регистра 21 изменения длительности импульсов и схему 22 Измеситя длительности импульсов устанавливает поминальную временную пос;едовательность АЛБ 1, и цикл микропрограммной диагностики первого этапа повторяется,Первый этап микропрограммной диагностики завершается проверкой аппаратуры считывания запоминающего блока 15 в регистр 13 запоминающего блока в режиме номинальной временной последовательности запоминающего блока и установкой триггера 28 перес,точения выборки в единичное состояние. При этом в блоке синхронизации 12 блокируется временная последователтт Ость блока 2 запоминания микрокоманд и перед выбортой каждой микрокоманды запускается врем, иная последовательности запоминающего блока 15. Адрес выборки определяется адресчьтм рсгистро 1 блока запоминания микрокомяпд т в рсгпстре микрокоманд 9 включаются цепи приема информации из запомиттающего блока 15.Таким образом, второй этап микропрограммной диагностики производится под управлением запоминаюцтего блока 15, что существенно сократцяет Ооьем блока 2 запоминания микрокоматтд, необходпмьй для диагностики. Кроме того, данный режим работы используется при отладке микропрограмм, что позволяет оперативно вносить ттзметтсния.В случае, если автоматическая дттагпостик: пе может точно локализовать место неисправности, в предлагаемом устройстве используется реким заттикливания микропрограмм, существенно облегчающий режим ручной диагностики.Данный режим позволяет зацикливать любые микропрограммы, а такке фрагменты пз них. Режим зацикливания микропрограмм, в основном, использует аппаратурх Остяповя го адресу и повтора микрокоманд.Начальный адрес цикла набирается в адресном регистре 8 повтора микрокоманд, а конечный адрес цикла набирается в регистре ключей 17 останова по адресу.При пуске процессора в работу блока 23 зацикливания микропротрамм передает сОдепжимое адресного регистра 8 повтора микро- команд в адресный регистр 5 блока запоминания мнкрокоманд и бло: прует обратную передачу. Когда содержимое адресного регистра 15 20 25 ЗО 35 40 45 50 55 60 65 О, О к 11 3 а и с 1я 1 И 51 м И кр О к О М а 11,1 О х дс Г 1) я В. о конечному адресу цикла, пяс)рянш)му В рсгистре ключей 17 остаповя по адресу, схем;1 сравненя 18 передает сигнал В блок 23 затшкливания микропрограмм, который вновь с.сутцсствляет передачу содержимого адресного регистра 8 повтора мтткрокомяпд В адресный регистр 5 блока запоминания микро- КОМВНД И Т,;1,Предмет изобретения.Чик)с)программнт 11 процессор, содержащий арифметико-лопческий олок, связанный с запоминающим блоком, блок контроля, вьХоды которого соединены с первыми входами б;ока синхронизации и блока дешифрации микрокомяпд, блок управления диагностикой, первый выход которого соединен со вторым входом блока синхронизации, узел контроля четности, с)лок запоминания микрокоматд, свя ИАй с псрным Входом регистра митсрокомяпд, с выходами дешпфраторов горизон ялтптьтх 11 Всрттт(альнтэтх шттн, соответствуО- щие Входы которых соединены с Выходами блока синхронизации, адресого регистра блока запоминания микрокомяпд и выходами горизонтального и вертикального вентилей блокировки, причем вход Олока управления диаг Остикой соединен с одним выходом переклю тте,т 51 режимов, другой выход которого соединен с третьим входом блока синхронизации, пепвый выход блока дешифрации микро- команд соединен со входом арпфметико-логического блока, соответствующий выход которого соединен с первым входом блока контроля, второй вход которого через узел контроля четности соединен с выходом регистра мпкрокоманд и вторым входом блока дешифрации мпкрокоманд, отличающийся тем, что, с целью упрощения процессора, он содерсит Олок изътепения длительнОсти импульсов, риггеры переключения выборки, инверсии контроля и инверсии Олокировки, причем входы триггера инверсии контроля соединены со входом и со вторым выходом блока управления диагностикой, третий выход которого соеди; еп с одним из Входов триггера инверсии блокировки, выходы которого соединены с псрвымп Входами горизонтального и вертикального вентилей олокировки, вторые входы КОТОРт.; СОЕДПЧЕС ОДНИМ ИЗ ВЫХОДОВ тРИГ- геда инверсии контроля и с третьим входом блока контроля, четвертый выход блока управления диагностикой через блок измеения длительности импульсов соединен с четвертым входом блока синхронизации, пятый вход которого соединен со вторым входом регистра микрокомянд и чеоез триггер переклточегтия выборки - - со вторым Выходом блока дешифрации микрокоманд, а третий вход регистра микрокомапд сос диттеп с выходом запоминаю. щего блока,.Заказ 23253Ц 1 ИИ ПодписноСР Типография, пр. Сапунов Изд.1509Государственного комитетапо делам изобретений иМосква, Ж, Раугнская 1Тираж 679овета Министровткрытийаб., д. 4,5

СмотретьЗаявка

1741209, 20.01.1972

ПРЕДПРИЯТИЕ ПЯ Г-4128

ДОЛКАРТ ВЛАДИМИР МИХАЙЛОВИЧ, ЕВДОЛЮК ЮРИЙ МАКСИМОВИЧ, КАНЕВСКИЙ МИХАИЛ МАТВЕЕВИЧ, НОВИК ГРИГОРИЙ ХАЦКЕЛЕВИЧ, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ, УЛЬЯНОВА ЕЛЕНА КОНСТАНТИНОВНА

МПК / Метки

МПК: G06F 19/00, G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 15.06.1975

Код ссылки

<a href="https://patents.su/5-474008-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для хранения и формирования микрокоманд

Следующий патент: Устройство для контроля арифметических операций по модулю три

Случайный патент: Способ развертки магнитного поля в спектрометрической аппаратуре и устройство для его осуществления