Устройство для формирования цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1802402

Авторы: Нанобашвили, Сванидзе

Текст

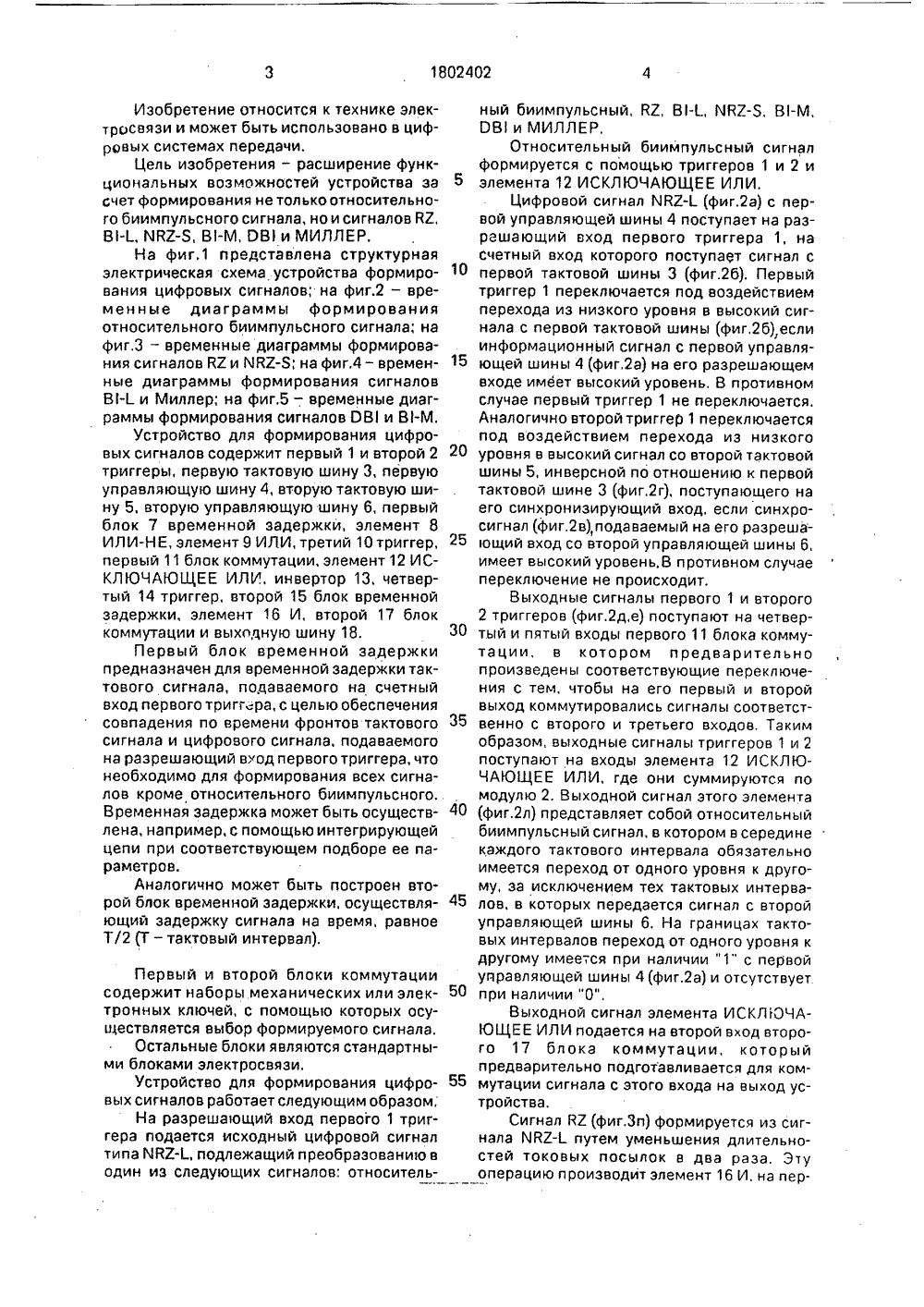

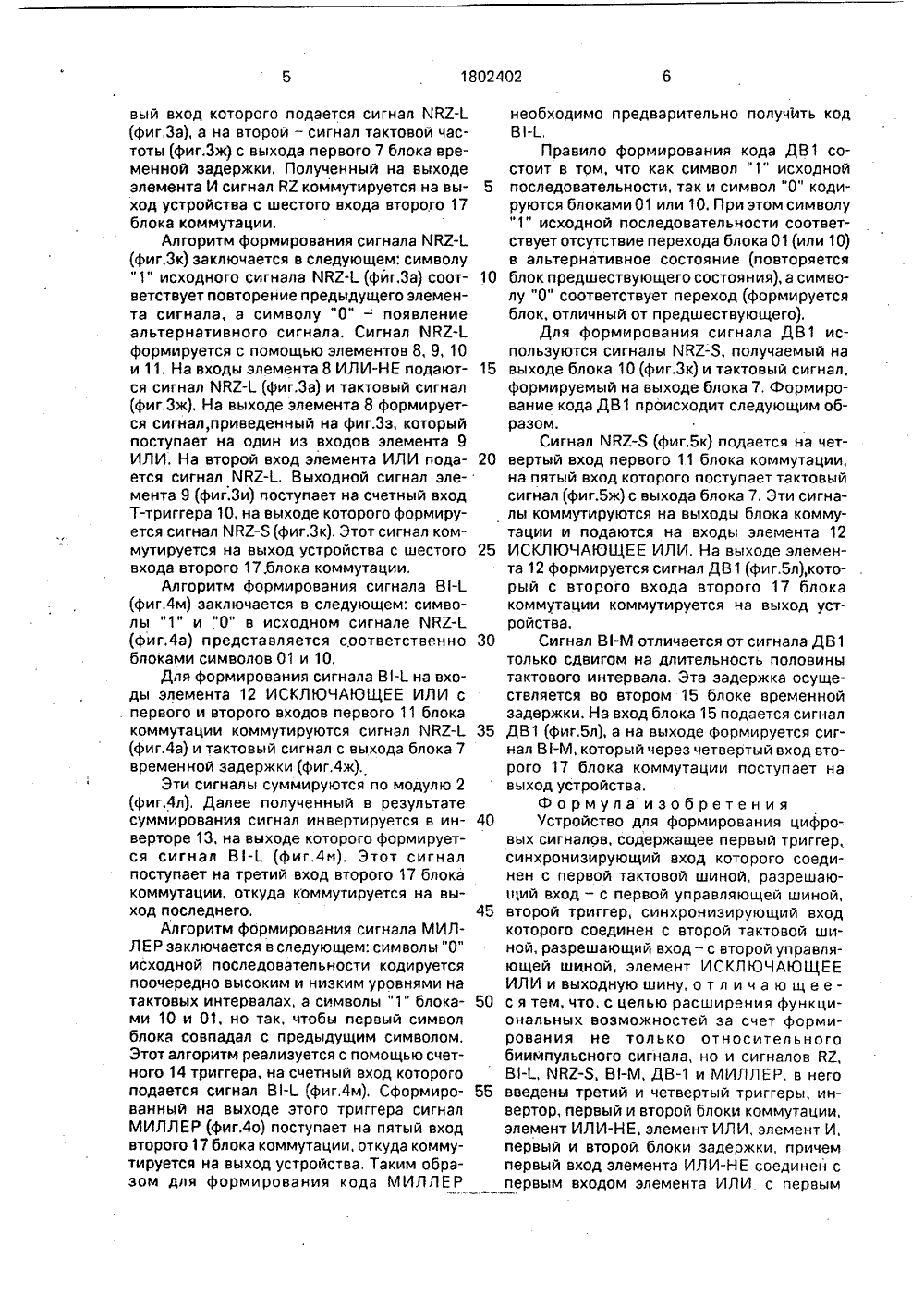

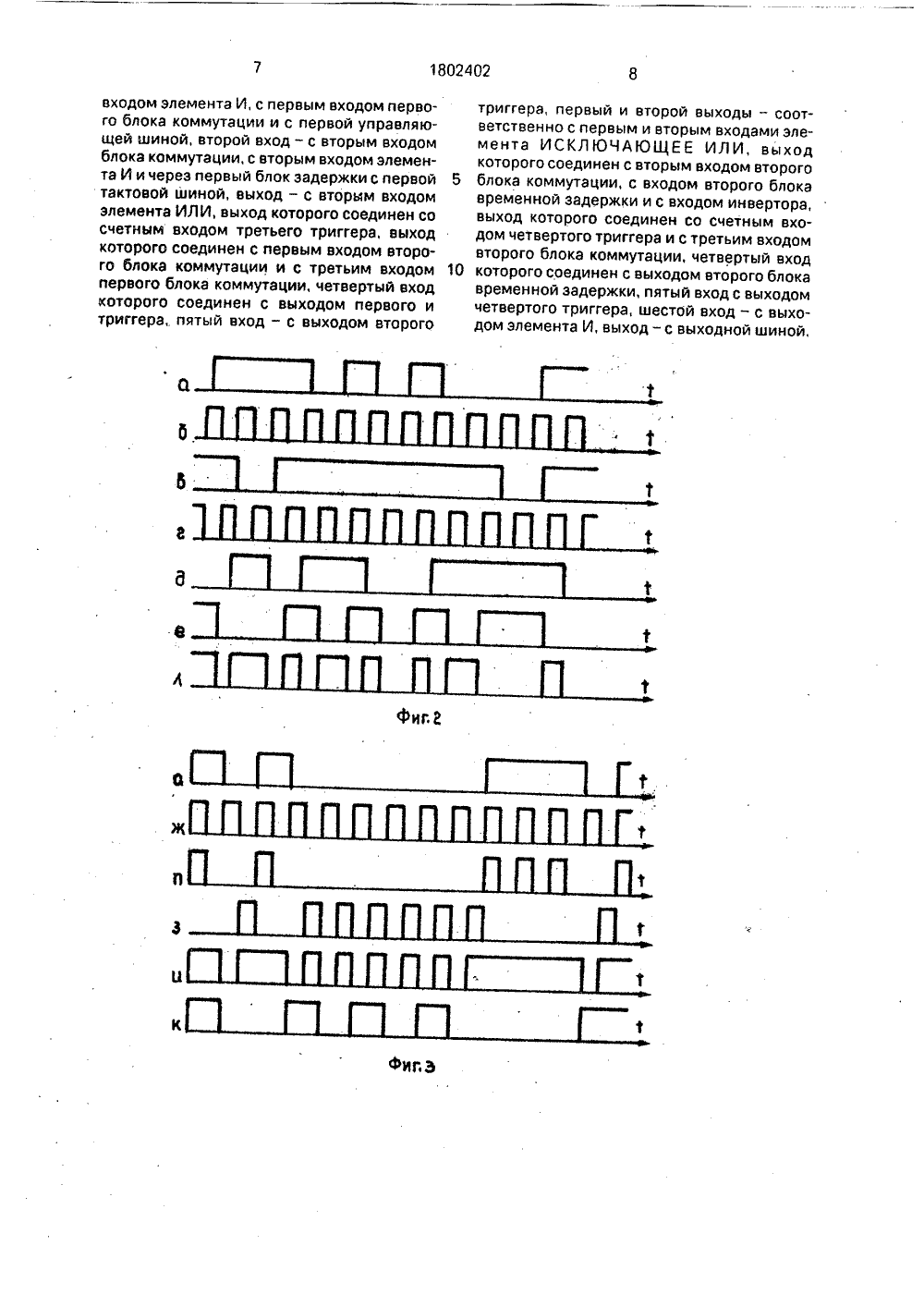

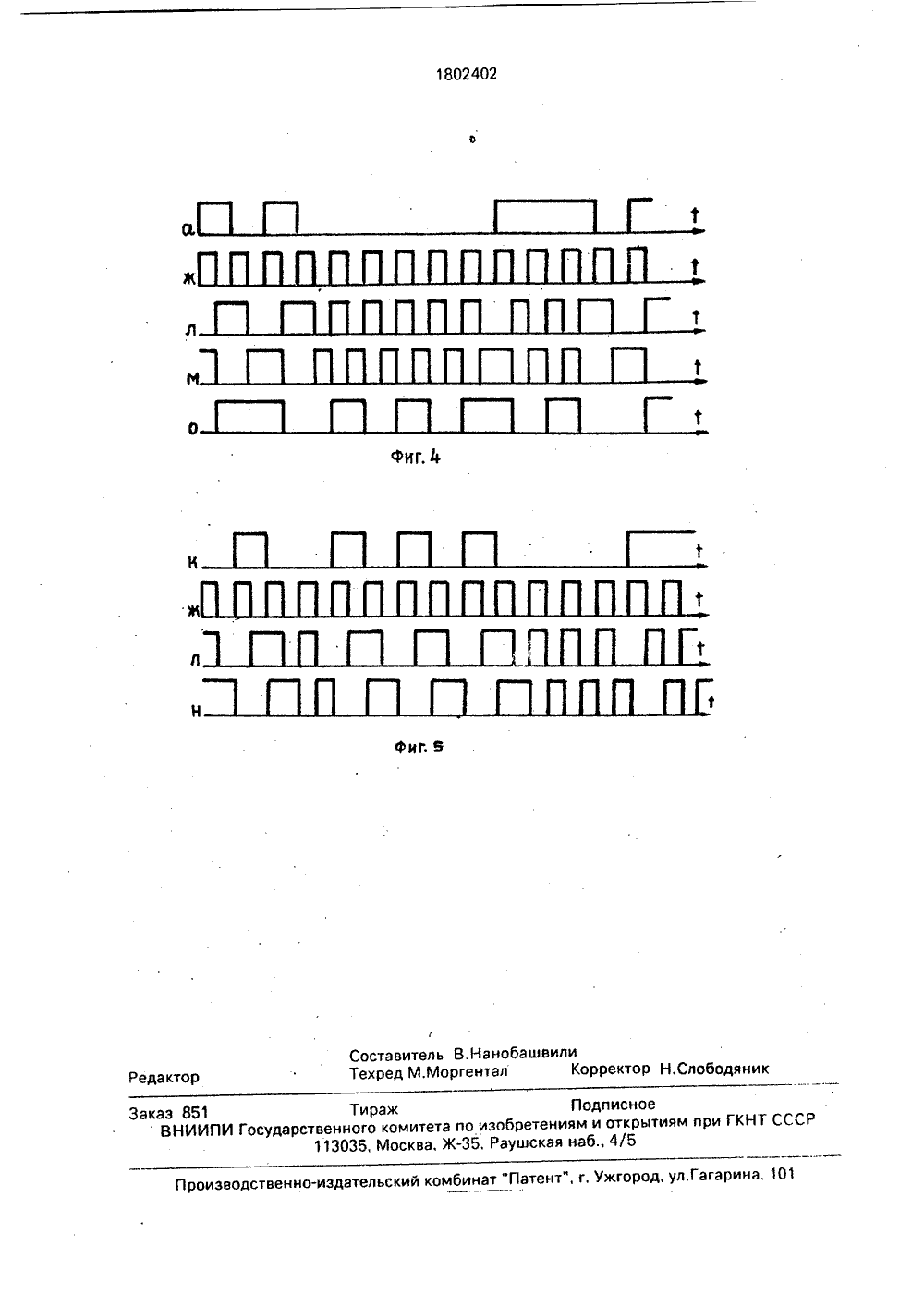

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1802402 А 1 п 9) 3 К 5/ ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ ВАНИЯ овано ойство блока ЮЩЕЕ (16), 2 шины О КАВТОРСКОМУ СВИДЕТЕЛЬСТ(71) Грузинский технический университе(56) Авторское свидетельство СССРМ 978375, кл, Н 04 1 5/14, 1980,Авторское свидетельство СССРМ 1396255, кл. Н 03 К 5/01, 1986,(54) УСТРОЙСТВО ДЛЯ ФОРМИРОЦИФРОВЫХ СИГНАЛОВ(57) Изобретение может быть использв цифровых системах передачи. Устрсодержит: 4 триггера (1, 2, 10, 14), 2временной задержки (7, 15), 2 блокатации (11, 17), 1 элемент ИЛИ-НЕ (8),мент ИЛИ (9), 1 элемент ИСКЛЮЧАИЛИ (12), 1 инвертор (1 3), 1 элемент Итактовые шины (3, 5), 2 управляющиеИзобретение относится к технике электросвязи и может быть использовано в цифровых системах передачи.Цель изобретения - расширение функциональных возможностей устройства за счет формирования не только относительного биимпульсного сигнала, но и сигналов ВЕ, ВН, ИВ 2-Я, В 1-М, ОВ 1 и МИЛЛЕР,На фиг.1 представлена структурная электрическая схема устройства формирования цифровых сигналов, на фиг.2 - временные диаграммы формирования относительного биимпульсного сигнала; на фиг.З - временные диаграммы формирования сигналов ВЕ и ИВЕ-Я, на фиг,4 - временные диаграммы формирования сигналов ВН и Миллер; на фиг.5 - временные диаграммы формирования сигналов ОВ 1 и В 1-М.Устройство для формирования цифровых сигналов содержит первый 1 и второй 2 триггеры, первую тактовую шину 3, первую управляющую шину 4, вторую тактовую шину 5, вторую управляющую шину 6, первый блок 7 временной задержки, элемент 8 ИЛИ-НЕ, элемент 9 ИЛИ, третий 10 триггер, первый 11 блок коммутации, элемент 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор 13, четвертый 14 триггер, второй 15 блок временной задержки, элемент 16 И, второй 17 блок коммутации и выходную шину 18,Первый блок временной задержки предназначен для временной задержки тактового сигнала, подаваемого на счетный вход первого тригг -ра, с целью обеспечения совпадения по времени фронтов тактового сигнала и цифрового сигнала. подаваемого на разрешающий в, од первого триггера, что необходимо для формирования всех сигналов кроме относительного биимпульсного. Временная задержка может быть осуществлена, например, с помощью интегрирующей цепи при соответствующем подборе ее параметров.Аналогично может быть построен второй блок временной задержки, осуществляющий задержку сигнала на время, равное Т/2 (Т - тактовый интервал). Первый и второй блоки коммутации содержит наборы механических или электронных ключей, с помощью которых осуществляется выбор формируемого сигнала,Остальные блоки являются стандартными блоками электросвязи,Устройство для формирования цифровых сигналов работает следующим образом;На разрешающий вход первого 1 триггера подается исходный цифровой сигнал типа МВ 7-1, подлежащий преобразованию в один иэ следующих сигналов; относительный биимпульсный, ВЕ, ВН, ИВУ, В 1-М,ОВ и МИЛЛЕР.Относительный биимпульсный сигналформируется с помощью триггеров 1 и 2 и5 элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ.Цифровой сигнал ИВЕ(фиг.2 а) с первой управляющей шины 4 поступает на разрешающий вход первого триггера 1, насчетный вход которого поступает сигнал спервой тактовой шины 3 (фиг,2 б). Первыйтриггер 1 переключается под воздействиемперехода из низкого уровня в высокий сигнала с первой тактовой шины (фиг.2 б),еслиинформационный сигнал с первой управля 15 ющей шины 4 (фиг,2 а) на его разрешающемвходе имеет высокий уровень, В противномслучае первый триггер 1 не переключается.Аналогично второй триггер 1 переключаетсяпод воздействием перехода из низкого20 уровня в высокий сигнал со второй тактовойшины 5, инверсной по отношению к первойтактовой шине 3 (фиг,2 г), поступающего наего синхронизирующий вход, если синхросигнал (фиг,2 в),подаваемый на его разрешающий вход со второй управляющей шины 6,имеет высокий уровень,В противном случаепереключение не происходит.Выходные сигналы первого 1 и второго2 триггеров (фиг.2 д,е) поступают на четверЗО тый и пятый входы первого 11 блока коммутации, в котором предварительнопроизведены соответствующие переключения с тем, чтобы на его первый и второйвыход коммутировались сигналы соответст 35 венно с второго и третьего входов, Такимобразом, выходные сигналы триггеров 1 и 2поступают на входы элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, где они суммируются помодулю 2, Выходной сигнал этого элемента40 (фиг.2 л) представляет собой относительныйбиимпульсный сигнал, в котором в серединекаждого тактового интервала обязательноимеется переход от одного уровня к другому, за исключением тех тактовых интерва 45 лов, в которых передается сигнал с второйуправляющей шины 6. На границах тактовых интервалов переход от одного уровня кдругому имеется при наличии "1" с первойуправляющей шины 4 (фиг.2 а) и отсутствует50 при наличии "0",Выходной сигнал элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подается на второй вход второго 17 блока коммутации, которыйпредварительно подготавливается для ком 55 мутации сигнала с этого входа на выход устройства.Сигнал ВЕ (фиг.Зп) формируется из сигнала ИВЕпутем уменьшения длительностей токовых посылок в два раза, Этуоперацию производит элемент 16 И, на первый вход которого подается сигнал ЙВ 2-1(фиг,За), а на второй - сигнал тактовой частоты (фиг.Зж) с выхода первого 7 блока временной задержки, Полученный на выходеэлемента И сигнал В 2 коммутируется на выход устройства с шестого входа второго 17блока коммутации,Алгоритм формирования сигнала йВ 2-1"1" исходного сигнала ЙВ 2- (фиг,За) соответствует повторение предыдущего элемента сигнала, а символу "0" - появлениеальтернативного сигнала. Сигнал КВ 2-1.формируется с помощью элементов 8, 9, 10и 11, На входы элемента 8 ИЛИ-НЕ подаются сигнал КВ 2-1. (фиг.За) и тактовый сигнал(фиг,Зж), На выходе элемента 8 формируется сигнал, приведенный на фиг,Зз, которыйпоступает на один из входов элемента 9ИЛИ, На второй вход элемента ИЛИ подается сигнал ИВ 2-1, Выходной сигнал элемента 9 (фиг.Зи) поступает на счетный входТ-триггера 10, на выходе которого формируется сигнал ИВ 2-Я (фиг.Зк), Этот сигнал коммутируется на выход устройства с шестоговхода второго 17,блока коммутации,Алгоритм формирования сигнала ВН(фиг,4 м) заключается в следующем: символы "1" и "0" в исходном сигнале ЙВ 2-1(фиг.4 а) представляется соответственноблоками символов 01 и 10.Для формирования сигнала В 1-1 на входы элемента 12 ИСКЛЮЧАЮЩЕЕ ИЛИ с. первого и второго входов первого 11 блокакоммутации коммутируются сигнал ЙВ 2-1(фиг.4 а) и тактовый сигнал с выхода блока 7временной задержки (фиг,4 ж).Эти сигналы суммируются по модулю 2(фиг,4 л), Далее полученный в результатесуммирования сигнал инвертируется в инверторе 13, на выходе которого формируется сигнал В 1-1 (фиг.4 н), Этот сигналпоступает на третий вход второго 17 блокакоммутации, откуда коммутируется на выход последнего,Алгоритм формирования сигнала МИЛЛ Е Р заключается в следующем: символы "0"исходной последовательности кодируетсяпоочередно высоким и низким уровнями натактовых интервалах, а символы "1" блоками 10 и 01, но так, чтобы первый символблока совпадал с предыдущим символом,Этот алгоритм реализуется с помощью счетного 14 триггера, на счетный вход которогоподается сигнал В 1-1. (фиг.4 м), Сформированный на выходе этого триггера сигналМИЛЛЕР (фиг.4 о) поступает на пятый входвторого 17 блока коммутации, откуда коммутируется на выход устройства, Таким образом для формирования кода МИЛЛЕР необходимо предварительно получить кодВН,Правило формирования кода ДВ 1 состоит в том, что как символ "1" исходной5 последовательности, так и символ "0" кодируются блоками 01 или 10, При этом символу"1" исходной последовательности соответствует отсутствие перехода блока 01 (или 10)в альтернативное состояние (повторяется10 блок предшествующего состояния), а символу "0" соответствует переход (формируетсяблок, отличный от предшествующего),Для формирования сигнала ДВ 1 используются сигналы МВ 2-3, получаемый на15 выходе блока 10 (фиг.Зк) и тактовый сигнал,формируемый на выходе блока 7, Формирование кода ДВ 1 происходит следующим образом.Сигнал ИВ 2-Я (фиг,5 к) подается на чет 20 вертый вход первого 11 блока коммутации,на пятый вход которого поступает тактовыйсигнал (фиг.5 ж) с выхода блока 7. Эти сигналы коммутируются на выходы блока коммутации и подаются на входы элемента 1225 ИСКЛЮЧАЮЩЕЕ ИЛИ. На выходе элемента 12 формируется сигнал ДВ 1 (фиг.5 л),который с второго входа второго 17 блокакоммутации коммутируется на выход устройства.30 Сигнал В 1-М отличается от сигнала ДВ 1только сдвигом на длительность половинытактового интервала. Эта задержка осуществляется во втором 15 блоке временнойзадержки, На вход блока 15 подается сигнал35 ДВ 1 (фиг,5 л), а на выходе формируется сигнал В 1-М, который через четвертый вход второго 17 блока коммутации поступает навыход устройства.Формула изобретения40 Устройство для формирования цифровых сигналов, содержащее первый триггер,синхронизирующий вход которого соединен с первой тактовой шиной, разрешающий вход - с первой управляющей шиной,45 второй триггер, синхронизирующий входкоторого соединен с второй тактовой шиной, разрешающий вход - с второй управляющей шиной, элемент ИСКЛЮЧАЮЩЕЕИЛИ и выходную шину, о т л и ч а ю щ е е 0 с я тем, что, с целью расширения функциональных возможностей за счет формирования не только относительногобиимпульсного сигнала, но и сигналов В 2,В 1-1, 1 чВ 2-3, В 1-М, ДВи МИЛЛЕР, в него5 введены третий и четвертый триггеры, инвертор, первый и второй блоки коммутации,элемент ИЛИ-НЕ, элемент ИЛИ, элемент И,первый и второй блоки задержки, причемпервый вход элемента ИЛИ-НЕ соединен спервым входом элемента ИЛИ с первымвходом элемента И, с первым входом первого блока коммутации и с первой управляющей шиной, второй вход - с вторым входом блока коммутации, с вторым входом элемента И и через первый блок задержки с первой тактовой шиной, выход - с вторым входом элемента ИЛИ, выход которого соединен со счетным входом третьего триггера, выход которого соединен с первым входом второго блока коммутации и с третьим входом первого блока коммутации, четвертый вход которого соединен с выходом первого и триггера, пятый вход - с выходом второго триггера, первый и второй выходы - соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом второго 5 блока коммутации, с входом второго блокавременной задержки и с входом инвертора, выход которого соединен со счетным входом четвертого триггера и с третьим входом второго блока коммутации, четвертый вход 10 которого соединен с выходом второго блокавременной задержки, пятый вход с выходом четвертого триггера, шестой вход - с выходом элемента И, выход - с выходной шиной,.1802402 Фиг,4 Фиг. В Составитель В,НанобашвилиТехред М,Моргентал Корректор Н,Слободяник Редактор Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 101 Заказ 851 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4931458, 22.04.1991

ГРУЗИНСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

НАНОБАШВИЛИ ВИКТОР ВАСИЛЬЕВИЧ, СВАНИДЗЕ РЕВАЗ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: сигналов, формирования, цифровых

Опубликовано: 15.03.1993

Код ссылки

<a href="https://patents.su/5-1802402-ustrojjstvo-dlya-formirovaniya-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования цифровых сигналов</a>

Предыдущий патент: Генератор импульсов со случайной длительностью

Следующий патент: Цифровое устройство для задержки импульсов

Случайный патент: Состав для изготовления угольно-пастового электрода