Дельта-модулятор для передачи речевых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

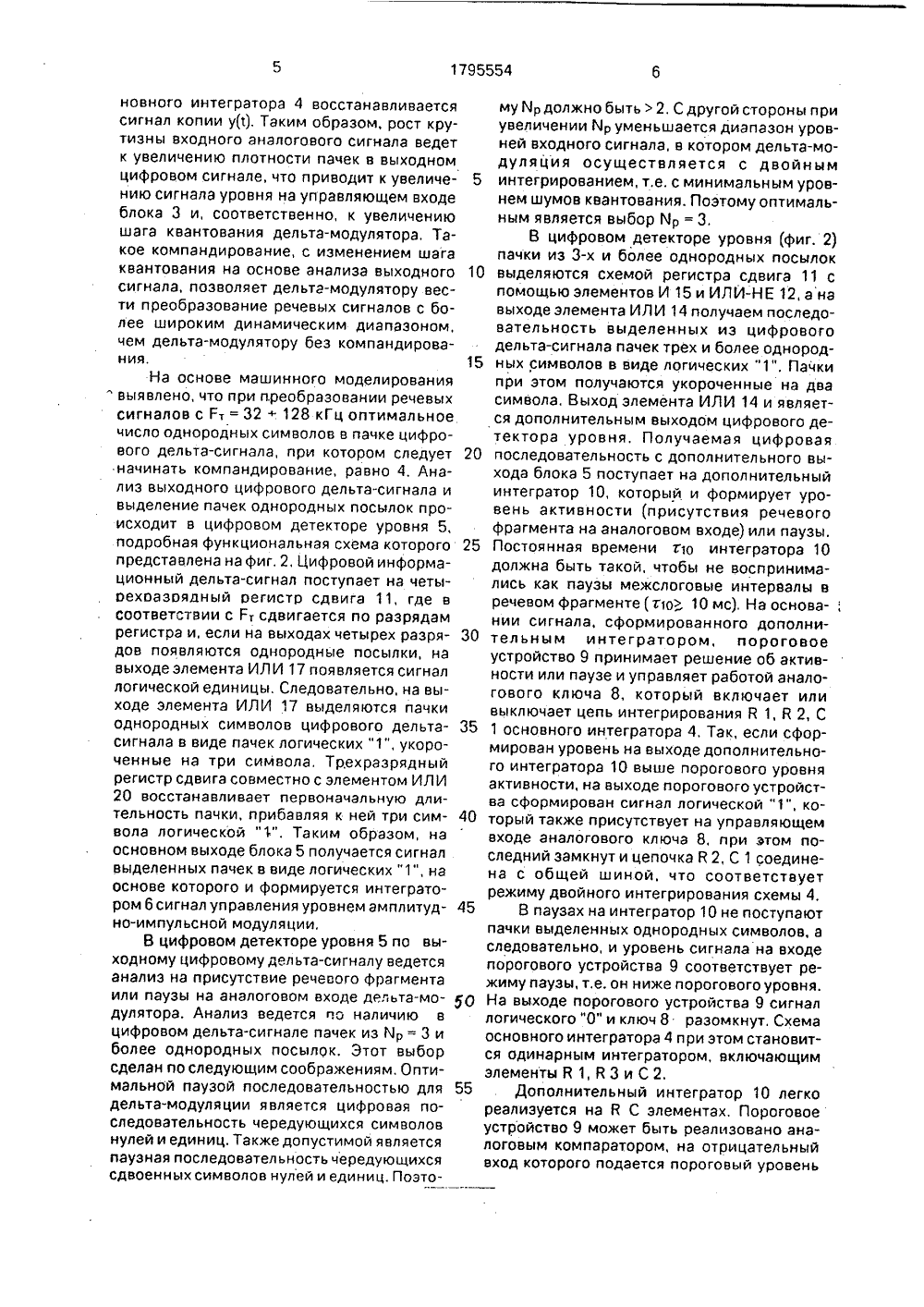

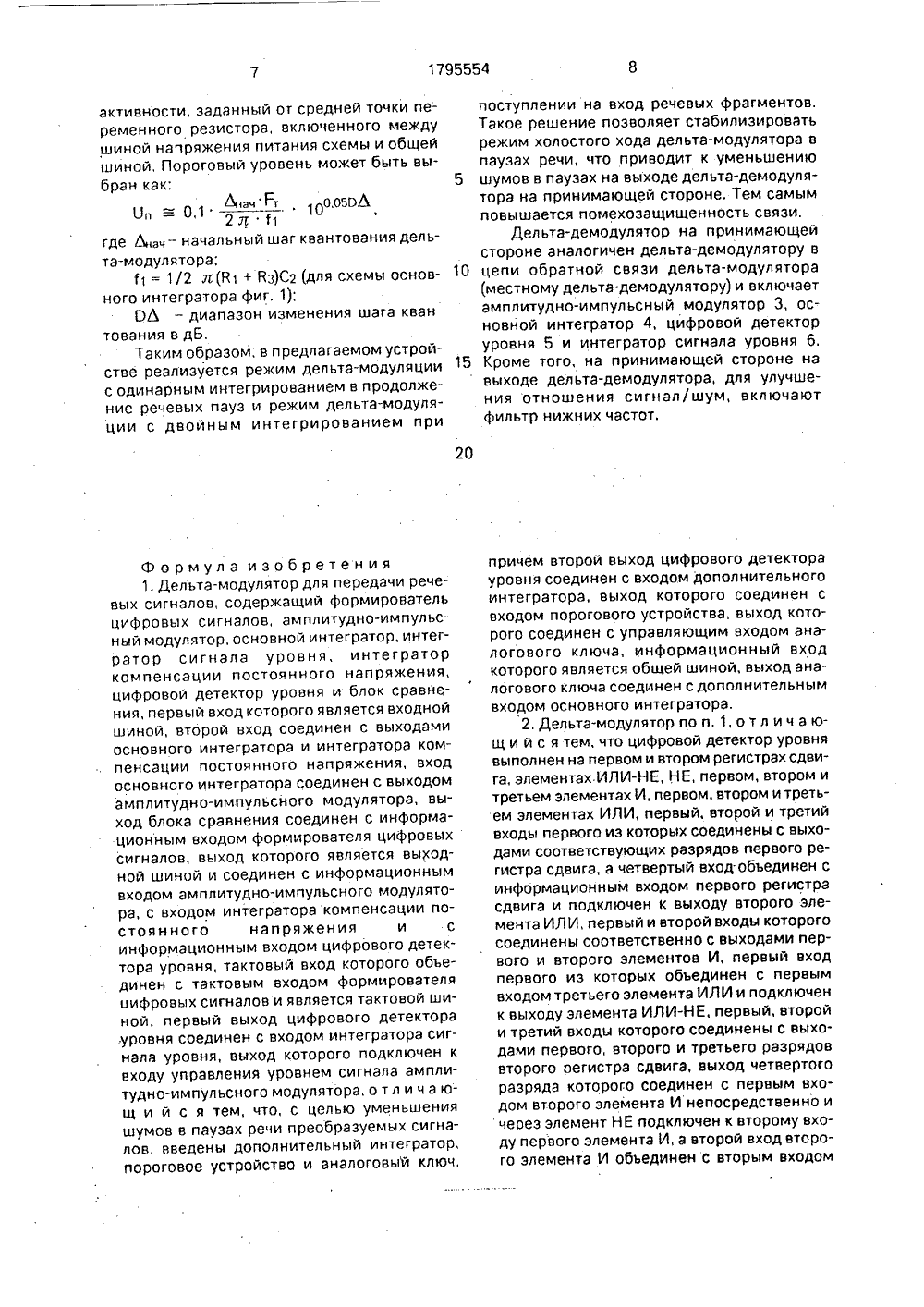

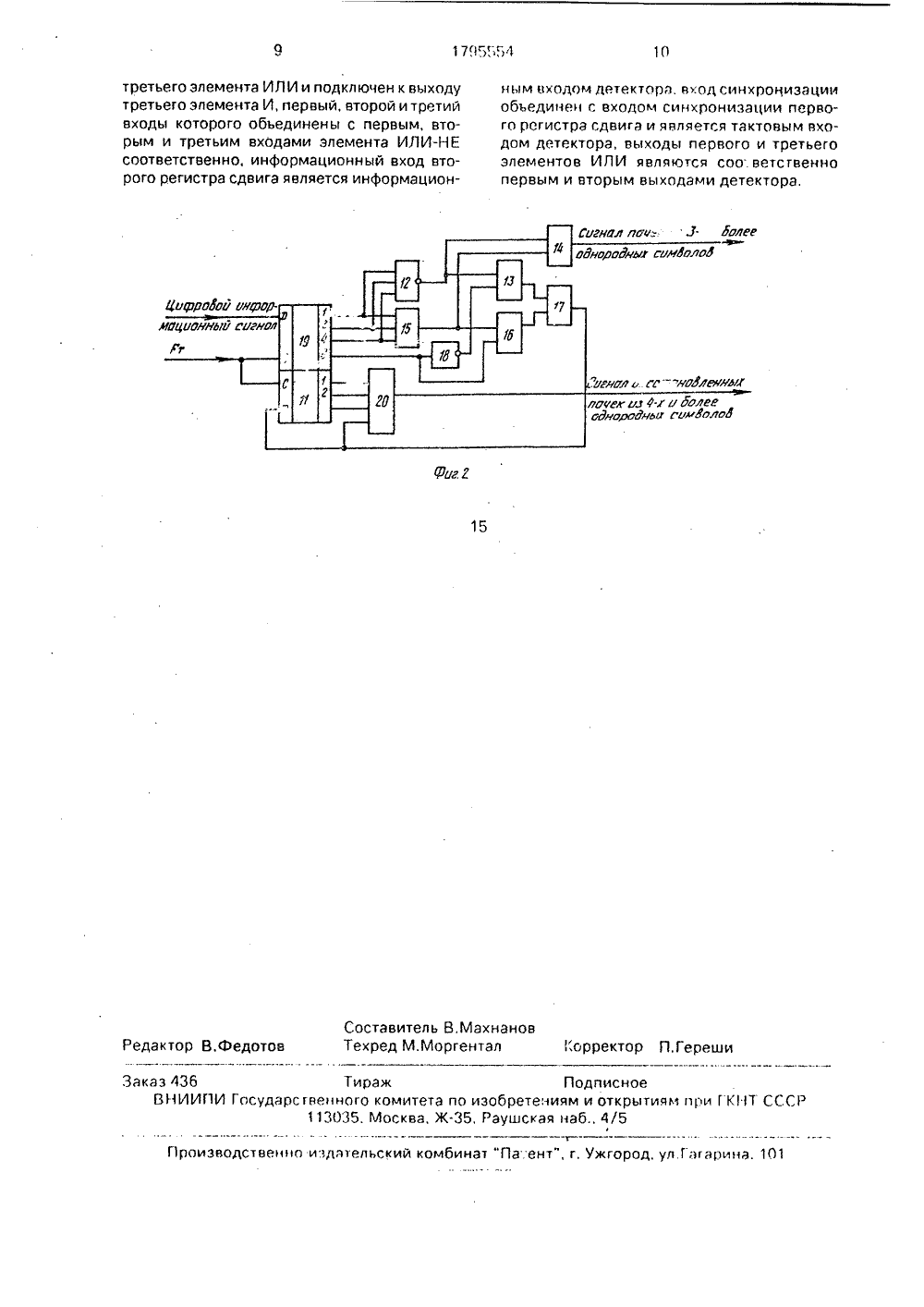

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 795554 А 1 Ф9) (51)5 Н 03 М 3/О ОПИСАНИЕ ИЗОБРЕТЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ М ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(71) Ленинградский электротехнический институт связи им. проф, М,А;Бонч-Бруевича 72) А.Ю.Буханник, Б,Е.Трофимови П,Е.ЩербатыйД 6) Авторское свидетельство СССР М 1429332, кл. Н 04 1 25/49, 1987.Гебергер Г.Х, Аналого-цифВвые преобразователи в канале ТЧ с дельта-модуля.- цией Электросвязь, 1978.(54) ДЕЛЬТА-МОДУЛЯТОР ДЛЯ ПЕРЕДАЧИ РЕЧЕВЫХ СИГНАЛОВ(57) Изобретение относится к электросвязи и может использоваться в цифровых системах передачи речевых сигналов для аналого-цифрового преобразования методом дельта-модуляции. Устройство позволяет в паузах речи увеличивать начальный шаг квантования, что стабилизирует его режим холостого хода и уменьшает шумы в паузах речи при дельта-модуляции. Это достигается тем, что по выходной цифровой информационной последовательности при помощи цифрового детектора уровня 5, дополнительного интегратора 10, порогового устройства 9 ведется анализ на активность и на основе анализа происходит переключение при помощи ключа, основного интегратора 4 на режим работы одинарного интегрирования (речевая пауза) или двойного интегрирования (речевой фрагмент). Это позволяет в дельта-модуляторе, который также включает блок сравнения 1, формирователь цифрового сигнала 2, амплитудно-импульсный модулятор 3, интегратор сигнала уровня 6 и интегратор компенсации постоянного на- я пряжения 7, применять двойное интегрирование при речевых фрагментах, что обеспечивает хорошее соотношение сигнал/шум квантования, а одинарное - при речевых паузах, чтостабилизирует режим холостого хода дельта-модулятора в паузах речи. 1 з.п. ф-лы, 2 ил.5 10 15 20 25 сдвига 19 и элементе ИЛИ 20.иНэ фиг. 1 представлена функциональ- с ная схема дельта-модулятора с компандиро- П ванием, которая в отличие от линейных т 7 дельта-модуляторов обладает рядом изве стнь 1 х преимуществ и находит широкое о практические применение, Однако в режи- у ме холостого хода, т,е. в паузах речи, дель- с та-модуляторы с компандированием р работают в режиме линейной дельта-моду д ляции с постоянным начальным шагом кван- о тования. Поэтому применение двойных н интеграторов в схемах дельта-демодулято- ч ров кэк при линейной, так и при компандируемой дельта- дуляции для увеличения 40 р отношения сигнал/шум квантования копии э у(с) сигнала требует стабилизации режима с холостого хода дельта-модулятора в паузах л речи. Предлагаемое решение может бь 1 ть в использовано как при линейной АД, тэк и 45 у при дельта-модуляции с компандировани- с ем, дРассмотрим работу схемы устройства в ч соответствии с его функциональной схемой фиг. 1 и функциональной схемой реализа и ции цифрового детектора уровня фиг, 2.Входной аналоговый сигнал х(с) посту- у пает на один из двух входов блока сравнения 1, где сравнивается с восстановленной т копией у сигнала, поступающего с цепи 55 з обратной связи местного дельта-модулятора на второй вход, Если х(1)у(т), на выходе т блока сравнения 1 сигнал логической "1", а ф если у(т)х - сигнал логического "0". и Ьлок сравнения реализуется аналоговым ИэгАретоние относится к электросвязиц ке 1 быгь использовано в системах передачи речевых сигналов с дельта-модуляцие й (ДУ),Цель изобретения - уменьшение шумов в паузах речи преобразуемых (дельта-модулированных) сигналов за счет стабилизации режима холостого хода дельта-модуляторов,На Фиг. 1 представлена функциональная схема дельта-модулятора для передачи речевых сигналов; на фиг, 2 - функциональная схема цифрового детектора уровня,Дельта-модулятор включает блок сравнения 1, формирователь 2 цифровь 1 х сигналов, амплитудно-импульсный модулятор 3, основной интегратор 4, цифровой детектор уровня 5, интегратор сигнала уровня б, интегратор компенсации постоянного напряжения 7, аналоговый ключ 8, пороговое устройство 9, дополнительный интегратор 10, а цифровой детектор уровня (фиг. 2) выполнен на регистре сдвига 11, элементе ИЛИ-НЕ 12, элементах И 13, ИЛИ 14, элементах И 15, 16, ИЛИ 17, НЕ 18, регистре компэратором, ширина переходной зоны которого должна бьть в 3-4 раза меньше начального шага квантования дельта-модулятора. Формирователь цифрового сигнала 2 с выходного сигнала блока сравнения 1 формирует, в соответствии с тактовой частотой Г, выходной информационный цифровой сигнал, Формирователь цифровых сигналов может быть реализован синхронным О-триггером. С выхода блока цифровой информационный сигнал поступает на цифровой выход устройства и в цепь обратной связи дельта-модулятора на входы цифрового детектора уровня 5, амплитудно-импульсного модулятора 3 и интегратора 7,Погрешности выполнения узлов схемы служат причинами появления на входе блока сравнения 1 постоянного смещения, которое приводит к преобладанию посылок одного знака. Это может привести как к нарушению режима холостого хода кодека. так и к появлению на входе блока сравнения 1 постоянного смещения, Для устранения указанного явления в состав дельта-модулятора введен интегратор 7, создающий коменсирующее постоянное напряжение в лучае преобладания посылок одного знака.остоянная времени интегратора 7 ) 0,2. 0,5 с.Амплитудно-импульсный модулятор 3, сновной интегратор 4, цифровой детектор ровня 5 и интегратор сигнала уровня б сотавляют схему местного дельта-демодулятоа которая включена в цепь обратной связи ельта-модулятора. 8 дельта-модуляторе на снове анализа структуры цифрового выходого сигнала осуществляется компрессия реевого аналогового сигнала х(с),Практически в рассматриваемом устойстве компрессия осуществляется за счет кспандирования в цепи обратной связи (метном дельта-демодуляторе) при восстановении копии у(с) входного сигнала из ыходного цифрового дельта-сигнала, При величении крутизны входного аналогового игнала в цифровом дельта-сигнале на выхое формирователей 2 появляются пачки из етырех и более однородных символов. Цифровой детектор уровня 5 выделяет пачки из 4 более однородных символов и с его первого выхода они поступают на интегратор сигнала ровня б. Таким образом, формируется сигнал, определяющий уровень сигнала амплиудно-импульсной модуляции. На основе того сигнала уровня и по выходному цифровому сигналу. поступающему на вход амплиудно-импульсного модулятора 3, ормируется амплитудно-модулированный мпульсный сигнал, из которого в схеме ос10 15 20 25 30 35 40 новного интегратора 4 восстанавливается сигнал копии у(1). Таким образом, рост крутизны входного аналогового сигнала ведет к увеличению плотности пачек в выходном цифровом сигнале, что приводит к увеличению сигнала уровня на управляющем входе блока 3 и, соответственно, к увеличению шага квантования дельта-модулятора, Такое компандирование, с изменением шага квантования на основе анализа выходного сигнала, позволяет дельта-модулятору вести преобразование речевых сигналов с более широким динамическим диапазоном, чем дельта-модулятору без компандирования.На основе машинного моделирования "выявлено, что при преобразовании речевых сигналов с Ет = 32128 кГц оптимальное число однородных символов в пачке цифрового дельта-сигнала, при котором следует начинать компандирование, равно 4. Анализ выходного цифрового дельта-сигнала и выделение пачек однородных посылок происходит в цифровом детекторе уровня 5, подробная функциональная схема которого представлена на фиг. 2, Цифровой информационный дельта-сигнал поступает на четыоехоазоядный регистр сдвига 11, где в соответствии с Е сдвигается по разрядам регистра и, если на выходах четырех разрядов появляются однородные посылки, на выходе элемента ИЛИ 17 появляется сигнал логической единицы. Следовательно, на выходе элемента ИЛИ 17 выделяются пачки однородных символов цифрового дельта- сигнала в виде пачек логических "1", укороченные на три символа, Трехразрядный регистр сдвига совместно с элементом ИЛ И 20 восстанавливает первоначальную длительность пачки, прибавляя к ней три символа логической . Таким образом, на основном выходе блока 5 получается сигнал выделенных пачек в виде логических "1", на основе которого и формируется интегратором 6 сигнал управления уровнем амплитудно-импульсной модуляции,В цифровом детекторе уровня 5 по выходному цифровому дельта-сигналу ведется анализ на присутствие речевого фрагмента или паузы на аналоговом входе дельта-модулятора. Анализ ведется по наличию в цифровом дельта-сигнале пачек из Мр = 3 и более однородных посылок. Этот выбор сделан по следующим соображениям. Оптимальной паузой последовательностью для дельта-модуляции является цифровая последовательность чередующихся символов нулей и единиц. Также допустимой является паузная последовательность чередующихся сдвоенных символов нулей и единиц. Поэтому Мр должно быть2. С другой стороны при увеличении йр уменьшается диапазон уровней входного сигнала, в котором дельта-модуляция осуществляется с двойным интегрированием, т.е, с минимальным уровнем шумов квантования. Поэтому оптимальным является выбор Ир = 3,В цифровом детекторе уровня фиг. 2) пачки из 3-х и более однородных посылок выделяются схемой регистра сдвига 11 с помощью элементов И 15 и ИЛИ-НЕ 12, а на выходе элемента ИЛИ 14 получаем последовательность выделенных из цифрового дельта-сигнала пачек трех и более однородных символов в виде логических "1". Пачки при этом получаются укороченные на два символа. Выход элемента ИЛИ 14 и является дополнительным выходом цифрового детектора уровня, Получаемая цифровая последовательность с дополнительного выхода блока 5 поступает на дополнительный интегратор 10, который и формирует уровень активности (присутствия речевого фрагмента на аналоговом входе) или паузы. Постоянная времени тю интегратора 10 должна быть такой, чтобы не воспринимались как паузы межслоговые интервалы вречевом фрагменте (тю 10 мс), На основании сигнала, сформированного дополнительным интегратором, пороговое устройство 9 принимает решение об активности или паузе и управляет работой аналогового ключа 8, который включает или выключает цепь интегрирования В 1, Я 2, С 1 основного интегратора 4, Так, если сформирован уровень на выходе дополнительного интегратора 10 выше порогового уровня активности, на выходе порогового устройства сформирован сигнал логической "1", который также присутствует на управляющем входе аналогового ключа 8, при этом последний замкнут и цепочка В 2, С 1 соединена с общей шиной, что соответствует режиму двойного интегрирования схемы 4,В паузах на интегратор 10 не поступают пачки выделенных однородных символов, а следовательно, и уровень сигнала на входе порогового устройства 9 соответствует режиму паузы, т.е. он ниже порогового уровня. На выходе порогового устройства 9 сигнал логического "0" и ключ 8 разомкнут. Схема основного интегратора 4 при этом становится одинарным интегратором, включающим элементы К 1, В 3 и С 2,Дополнительный интегратор 10 легко реализуется на В С элементах. Пороговое устройство 9 может быть реализовано аналоговым компаратором, на отрицательный вход которого подается пороговый уровеньо Составитель В.МахнановРедактор В,Федотов Техред М,Моргентал г,орректор П. Гере 1 роизеодствен кий комбинат "Па.ент", г, Ужгород, ул.Гагарина, 10 здател третьего элемента ИЛИ и подключен к выходу третьего элемента И, первый, второй и третий входы которого обьединены с первым, вторым и третьим входами элемента ИЛИ-НЕ соответственно, информационный вход второго регистра сдвига является информационказ 436 Тираж ВНИИПИ Государсгвенного комитета по 113035, Москва, Жным входом детекторл. вход синхронизации обьединен с входом синхронизации первого регистра сдвига и является тактовым входом детектора, выходы первого и третьего элементов ИЛИ являются соо ветсгвенно первым и вторым выходами детектора,Подписноеизобретениям и открытиям приКНТ СССР

СмотретьЗаявка

4827608, 21.05.1990

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ПРОФ. М. А. БОНЧ-БРУЕВИЧА

БУХИННИК АЛЕКСАНДР ЮРЬЕВИЧ, ТРОФИМОВ БОРИС ЕВСЕЕВИЧ, ЩЕРБАТЫЙ ПАВЕЛ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-модулятор, передачи, речевых, сигналов

Опубликовано: 15.02.1993

Код ссылки

<a href="https://patents.su/5-1795554-delta-modulyator-dlya-peredachi-rechevykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-модулятор для передачи речевых сигналов</a>

Предыдущий патент: Адаптивный восстанавливающий фильтр в дельта-модуляторе с двойным интегрированием

Следующий патент: Устройство для декодирования импульсно-временных кодов

Случайный патент: Устройство для срезания сучьев с поваленных деревьев