Устройство для деления чисел на константу типа 2 + 1

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

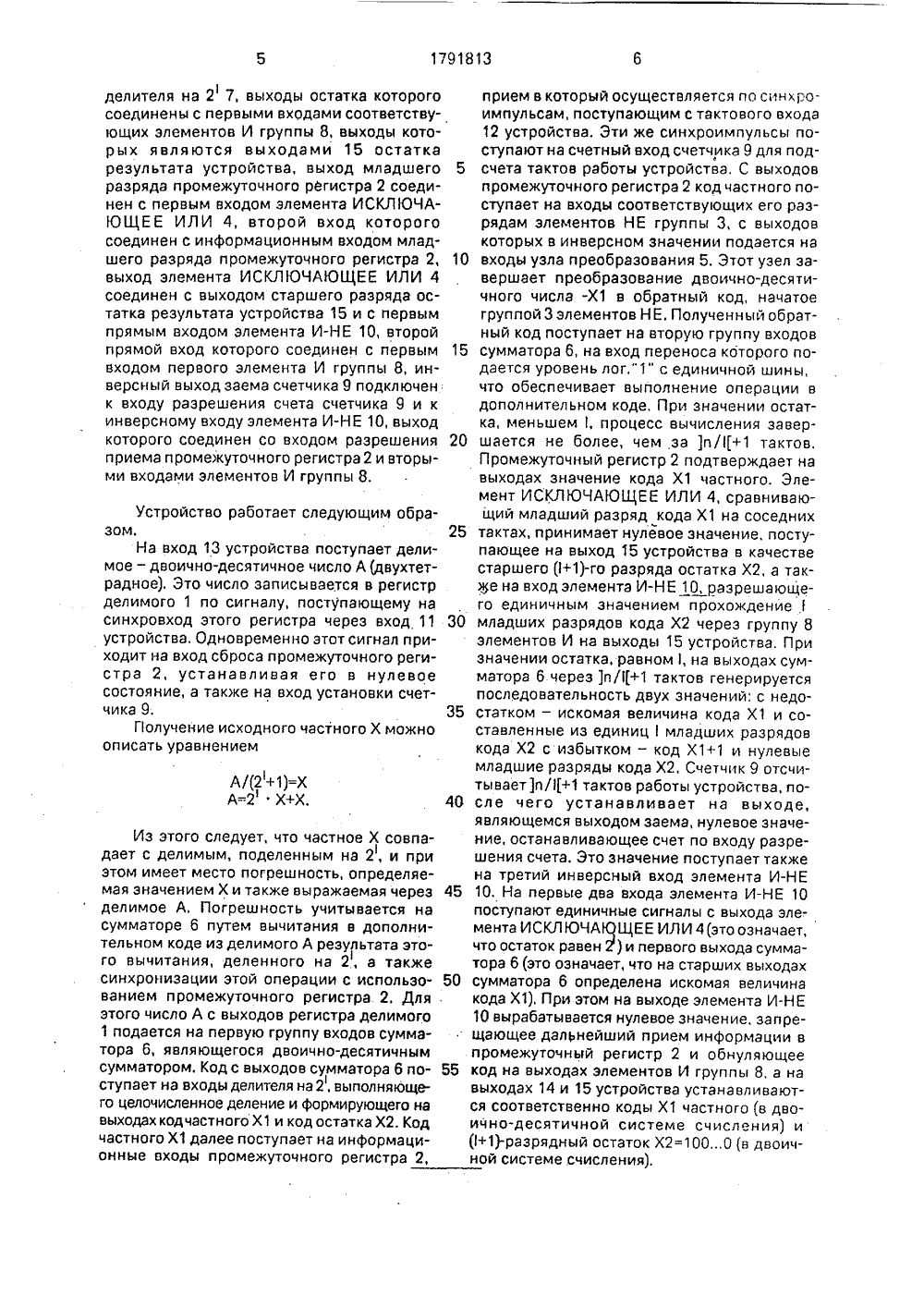

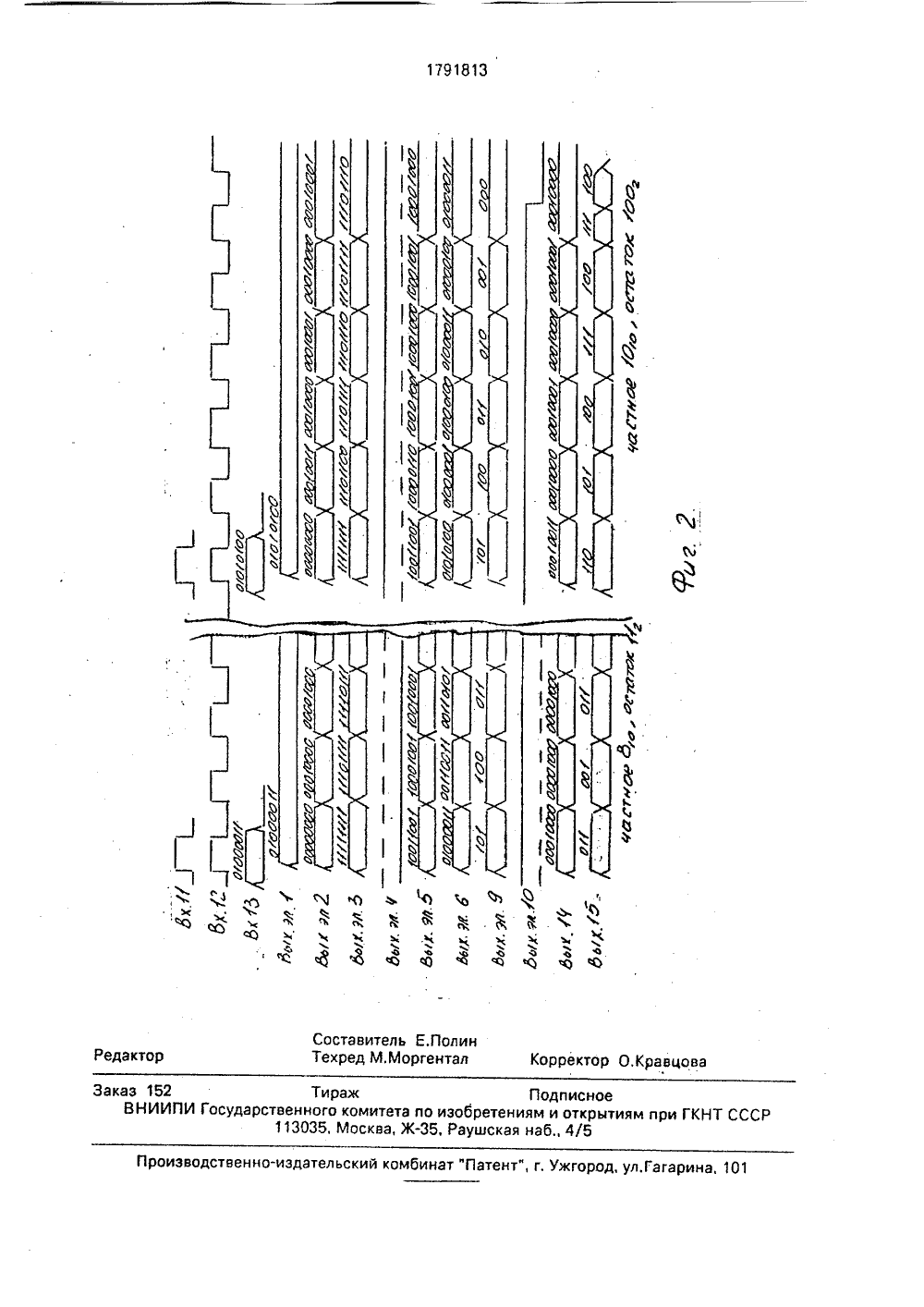

(5)5 6 06 Г 7/52 К АВТОРСКОМ ИДЕТЕЛ ЬСТВ ий институтЕ,Т. Кузнецов во ССС, 1989. О СУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ И ГКНТ СССР(54) УСТРОЙСТВО ДЛЯ ЦЕЛЕНИЯ ЧИСЕЛ НА КОНСТАНТУ ТИПА 2.+1(57) Изобретение относится к вычислительной технике, может быть использовано в арифметических блоках ЭВМ и позволяет делить числа на константу типа 2+1 в двоич,но-десятичной системе счисления. Целью изобретения является расширение области применения за счет возможности выполнения операции деления на константу (2+1) Изобретение относится к вычислительной технике и может быть использовано в арифметических блоках ЭВМ.Известно устройство для деления на константу типа 2-1, содержащее сумматор, регистр делимого, элемент НЕ, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, две группы элементов И, промежуточный регистр и элемент И.Недостатком устройства являются ограниченные функциональные возможности.Известно устройство для деления на константу типа 2 +1, выбранное в качествепрототипа и содержащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент Идвоична-десятичных чисел. Устройство содержит регистр делимого, сумматор, выполняющий сложение в двоичко-десятичной системе счисления в дополнительном коде с результатом сложения, деленным с помощью блока деления на 2, задержанным на промежуточном регистре, взятом со знаком "-" и преобразованным в обратный код на элементах НЕ группы и блока преобразования обратного кода в дополнительный, Вычисления выполкяотея итерационно за несколько тактов, отсчитываемых счетчиком, по истечекии )и/(+1 тактов вычислительный процесс останавливается, если остаток не равен 2. Частное и остаток поступают с выхода делителя на выходы устройства, В противном случае вырабатывается последовательность чередующихся значений результата с недостатком, где вычисляется правильное частное и остаток, равный 2-1, и с избытком. 2 ил.НЕ, элементы НЕ группы, элементы И группы, причем и-разрядный информационный О вход регистра делимого является входом делимого устройства, а выходы и разрядов СО регистра делимого соединены с соответст- ф вующими входами первой группы входов (Д сумматора, входы с (и-+2)-го по п-й второй группы входов сумматора и вход переноса ф сумматора соединены с единичной шиной, младших выходов сумматора соединены с первыми входами соответствующих элементов И группы, выходы которых и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами остатка устройства, вход сброса промежуточного регистра объединен со входом установки счетчика и синхровходом ре 1791813гистра делимого и является входом запуска устройства, синхровход промежуточного регистра объединен с вычитающим входом счетчика и является тактовым входом устройства, выходы промежуточного регистра соединены с соответствующими входами элементов НЕ группы, выходы которых соединены с соответствующими входами второй группы входов сумматора, выходы +1, +2, , сумматора являются выходами частного устройства и соединены с информационными входами промежуточного регистра, выход +1 сумматора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход промежуточного регистра соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом элемента И-НЕ, первь.й выход сумматора соединен совторым входом элемента И-НЕ, выход которого соединен со входом разрешения приема и ромежуточно го регистра, а также со вторыми входами элементов И группы, выход счетчика соединен со входом разрешения счета счетчика, а также с третьим входом элемента И-НЕ инверсььььм),Недостатком устройства являются ограниченные функциональные возможности, обусловленные невозможностью его рабаты в двоична-десятичнай системе счисления,Целььо изобретения является расширение области применения устройства,Цель достигается тем, что в устройство для деления на константу типа 2+1, содерьжащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элементы НЕ групцы, элементы И группы, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, выходы разрядов котарага соедьлнены с первой группой входов сумматора, вход переноса которого подключен к единичной шине, информационные входы промежуточного регистра объединены с соответствующими вььходами частного результата устройства, а выходы промежуточного регистра подключены ко входам соответствующих элементов НЕ группы, выход первого разряда сумматора и информационный вход первого разряда промежуточного регистра соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом старшего разряда остатка устройства и соединен с первым прямым входом элемента И-НЕ, второй прямой вход которого объединен с первым входом первого элемента И группы, а выходэлемента И-НЕ соединен со входом разрешения приема промежуточного регистра ивторыми входами элементов И группы, вход5 запуска устройства соединен с входом сброса промежуточного регистра, с синхровходом регистра делимого и входом установкисчетчика, синхровход которого соединен ссинхровходом промежуточного регистра и с10 тактовым входом устройства, инверсныйвыход заема счетчика соединен с входомразрешения счета счетчика и инверснымвходом элемента И-НЕ, выход элемента Игруппы является выходами младших разря 15 дов остатка результата устройства, введеныузел преобразования и делитель на 2, причем входы узлы преобразования подкльочены к выходам соответствуьощих элементовНЕ группы, а выходы - к соответствующим20 входам второй группы входов сумматора,выходы которого подключены к соответствующим входам делителя на 2, выходы част 1ного которого являются выходами частногорезультата устройства, а выходы остатка со 25 единены с первыми входами элементов Игруппы.На чертеже показана схема устройствадля случая двухтетрадного делимого; нафиг, 2 - временные диаграммы, иллюстри 30 рующие работу устройства,Устройство содержит регистр делимого1, промежуточный регистр 2, элементы НЕ3.1 - 3.7 группы, элемент ИСКЛЮЧАЮЩЕЕИЛИ 4, узел преобразования 5, сумматор 6,35 делитель на 2 7, элементы И 8.1 - 8 Л группы,счетчик 9, элемент И-НЕ 10, причем вход 11запуска устройства подключен к входу сброса промежуточного регистра 2, синхровходурегистра делимого 1 и входу установки счет 40 чика 9, синхровход которого соединен с синхровходам промежуточного регистра 2 иявляется тактовым входом 12 устройства,входы 13 делимого устройства соединены синформационными входами соответствую 45 щих разрядов регистра делимого 1, выходыразрядов которого соединены с соответствуьощими входами первой группы входов сумматора 6, вход переноса которого подключенк единичной шине, а входы второй группы50 входов подключены ксоатветствующим выходам узла преобразования 5, входы которогосоединены с выходами соответствующихэлементов НЕ группы 3, входы которых подключены к выходам соответствующих разрядов и ро 55 межуточнога регистра 2, информационные входыразрядов которого соединены соответственна с выходами частнога делителя на 2 7 иявляются выходами 14 частного результатаустройства, выходы разрядов сумматора 6соединены с соответствующими входами1791813 10 15 20 А/(2 +1)=Х А=-2 Х+Х. 45 50 55 делителя на 2 7, выходы остатка которогосоединены с первыми входами соответствующих элементов И группы 8, выходы которых являются выходами 15 остатка результата устройства, выход младшего разряда промежуточного регистра 2 соединен с первым входом элемента ИСКЛОЧАЮЩЕЕ ИЛИ 4, второй вход которого соединен с информационным входом млад- щего разряда промежуточного регистра 2, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен с выходом старшего разряда остатка результата устройства 15 и с первым прямым входом элемента И-НЕ 10, второй прямой вход которого соединен с первым входом первого элемента И группы 8, инверсный выход заема счетчика 9 подключен к входу разрешения счета счетчика 9 и к инверсному входу элемента И-НЕ 10, выход которого соединен со входом разрешения приема промежуточного регистра 2 и вторыми входами элементов И группы 8. Устройство работает следующим образом.На вход 13 устройства поступает делимое - двоично-десятичное число А (двухтетрадное). Это число записывается в регистр делимого 1 по сигналу, поступающему на синхровход этого регистра через вход 11 устройства, Одновременно этот сигнал приходит на вход сброса промежуточного регистра 2, устанавливая его в нулевое состояние, а также на вход установки счетчика 9.Получение исходного частного Х можно описать уравнением Из этого следует, что частное Х совпадает с делимым, поделенным на 2, и приэтом имеет место погрешность, определяемая значением Х и также выражаемая через дел имое А. Погреш ность учитывается на сумматоре 6 путем вычитания в дополнительном коде из делимого А результата этого вычитания, деленного на 2, а такжесинхронизации этой операции с использованием промежуточного регистра 2. Для этого число А с выходов регистра делимого 1 подается на первую группу входов сумматора 6, являющегося двоично-десятичным сумматором, Код с выходов сумматора 6 поступает на входы делителя на 2, выполняют го целочисленное деление и формирующего на выходах кодчастного Х 1 и код остатка Х 2. Код частного Х 1 далее поступает на информационные входы промежуточного регистра 2,25 30 35 40 прием в который осуществляется по синхроимпульсам, поступающим с тактового входа 12 устройства, Эти же синхроимпульсы поступают на счетный вход счетчика 9 для подсчета тактов работы устройства. С выходов промежуточного регистра 2 код частного поступает на входы соответствующих его разрядам элементов НЕ группы 3, с выходов которых в инверсном значении подается на входы узла преобразования 5. Этот узел завершает преобразование двоично-десятичного числа -Х 1 в обратный код, начатое группой 3 элементов НЕ. Полученный обратный код поступает на вторую группу входов сумматора 6, на вход переноса которого подается уровень лог,"1" с единичной шины, что обеспечивает выполнение операции в дополнительном коде. При значении остатка, меньшем , процесс вычисления завершается не более, чем за )и/+1 тактов,Промежуточный регистр 2 подтверждает на выходах значение кода Х 1 частного, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, сравнивающий младший разряд кода Х 1 на соседних тактах, принимает нулевое значение, поступающее на выход 15 устройства в качестве старшего (+1)-го разряда остатка Х 2, а также на вход элемента И-НЕ 10, разрешающего единичным значением прохождениемладших разрядов кода Х 2 через группу В элементов И на выходы 15 устройства. При значении остатка, равном , на выходах сумматора 6 через )пЯ+1 тактов генерируется последовательность двух значений, с недостатком - искомая величина кода Х 1 и составленные из единицмладших разрядов кода Х 2 с избытком - код Х 1+1 и нулевые младшие разряды кода Х 2, Счетчик 9 отсчитываетп/+1 тактов работы устройства, после чего устанавливает на выходе,являющемся выходом заема, нулевое значение, останавливающее счет по входу разрешения счета, Это значение поступает также на третий инверсный вход элемента И-НЕ 10. На первые два входа элемента И-НЕ 10 поступают единичные сигналы с выхода элемента ИСКЛ ЮЧАК.ЩЕЕ ИЛИ 4(это означает, что остаток равен 2) и первого выхода сумматора 6 (это означает, что на старших выходах сумматора 6 определена искомая величина кода Х 1), При этом на выходе элемента И-НЕ 10 вырабатывается нулевое значение, запрещающее дальнейший прием информации в промежуточный регистр 2 и обнуляющее код на выходах элементов И группы 8, а на выходах 14 и 15 устройства устанавливаются соответственно коды Х 1 частного (в двоично-десятичной системе счисления) иРегистры 1 и 2 выполняются на микросхе 1 лах К 155 ИР 13, сумматор б - на микросхемах К 155 ИМЗ, счетчик 9 выполнен на микросхеме К 155 И Е 7, Его уста новочны й вход соединен с входом приема информации через инвертор, информационные входы микросхемы подключены к двоичной константе)п 11+1, вычитающий вход и вход разрешения счета подключены ко входам -1 и +1 соответственно. Узел преобразования выполняется на микросхемах К 155 ИМЗ, На этих микросхемах каждая тетрада ,предварительно проинвертированная) увеличивается на код 101 о=10102 с потерей переноса в пятый разряд. Это обеспечивает получение обратного кода двоична-десятичного числа, Делитель на 2 составлен из делителей на 2. Делитель на 2 выполняется на сумматоре (микросхема К 155 ИМЗ),По сравнению с прототипом предложенное устройство позволяет выполнять деление на константу вида 2+1 в двоичнодесятичной системе счисления, что расширяет функциональные возможности устройств подобного вида. Формула изобретения Устройство для деления чисел на константутипа 2+1, содержащее регистр делимого, промежуточный регистр, сумматор, счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элементы НЕ группы, элементы И группы, причем входы разрядов делимого устройства соединены с информационными входами соответствующих разрядов регистра делимого, выходы разрядов которого соединены с входали первой группы сумматора, вход переноса которого соединен с входом логической единицы, выходы частного устройства соединень с информационными входами промежуточно 101520 го регистра, выходы разрядов которого соединены с входами элементов НЕ группы,выходы младшего разряда частного устройства и младшего разряда промежуточного регистра соединены с первым и вторым входами соответственно элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с выходом старшего разряда остатка устройства и первым прямым входом элемента ИНЕ, выход которого соединен с входом оазрешения записи промежуточного регистра и первыми входами элементов И группы, выходы которых соединены с выходами младших разрядов остатка устройства, второй вход первого элемента И группы соединен с вторым прямым входом элемента И-НЕ, инверсный вход которого соединен с инверсным выходом заема и входом разрешения счета счетчика, установочный вход которого соединен с входом запуска устройства, синхровходом регистра делимого и входом сброса промежуточного регистра, синхровход которого соединен с синхровходом счетчика и тактовым входом устройства,25 о т л и ч а ю щ е е с я. тем, что, с цельюрасширения области применения путем обеспечения возможности выполнения операции деления на константу 2+1) двоичнодесятичных чисел, устройство содержит 30 блок деления на 2 и блок преобразованияобратного кода в дополнительный, входы которого соединены с выходами элементов НЕ группы, выходы блока преобразования обратного кода в дополнительный 35 соединены с входами второй группы сумматора, выходы которого соединены с входами блока деления на 2, выходы частногокоторого соединены с выходами частного устройства, выходы остатка блока деления 40 на 2 соединены с вторыми входами элементов И группы.каз 152 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 1 созсъ ьь.ъ,

СмотретьЗаявка

4890113, 10.12.1990

ОДЕССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПОЛИН ЕВГЕНИЙ ЛЕОНИДОВИЧ, ДРОЗД АЛЕКСАНДР ВАЛЕНТИНОВИЧ, КУЗНЕЦОВА ЕКАТЕРИНА ТЕОДОРОВНА, ДРОЗД ЮЛИЯ ВЛАДИМИРОВНА

МПК / Метки

МПК: G06F 7/52

Метки: деления, константу, типа, чисел

Опубликовано: 30.01.1993

Код ссылки

<a href="https://patents.su/5-1791813-ustrojjstvo-dlya-deleniya-chisel-na-konstantu-tipa-2-1.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления чисел на константу типа 2 + 1</a>

Предыдущий патент: Устройство для сортировки чисел

Следующий патент: Устройство для сравнения нечетных величин

Случайный патент: Способ добычи нефти