Мультиплексор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1780185

Авторы: Авгуль, Костеневич, Супрун, Фурашов

Текст

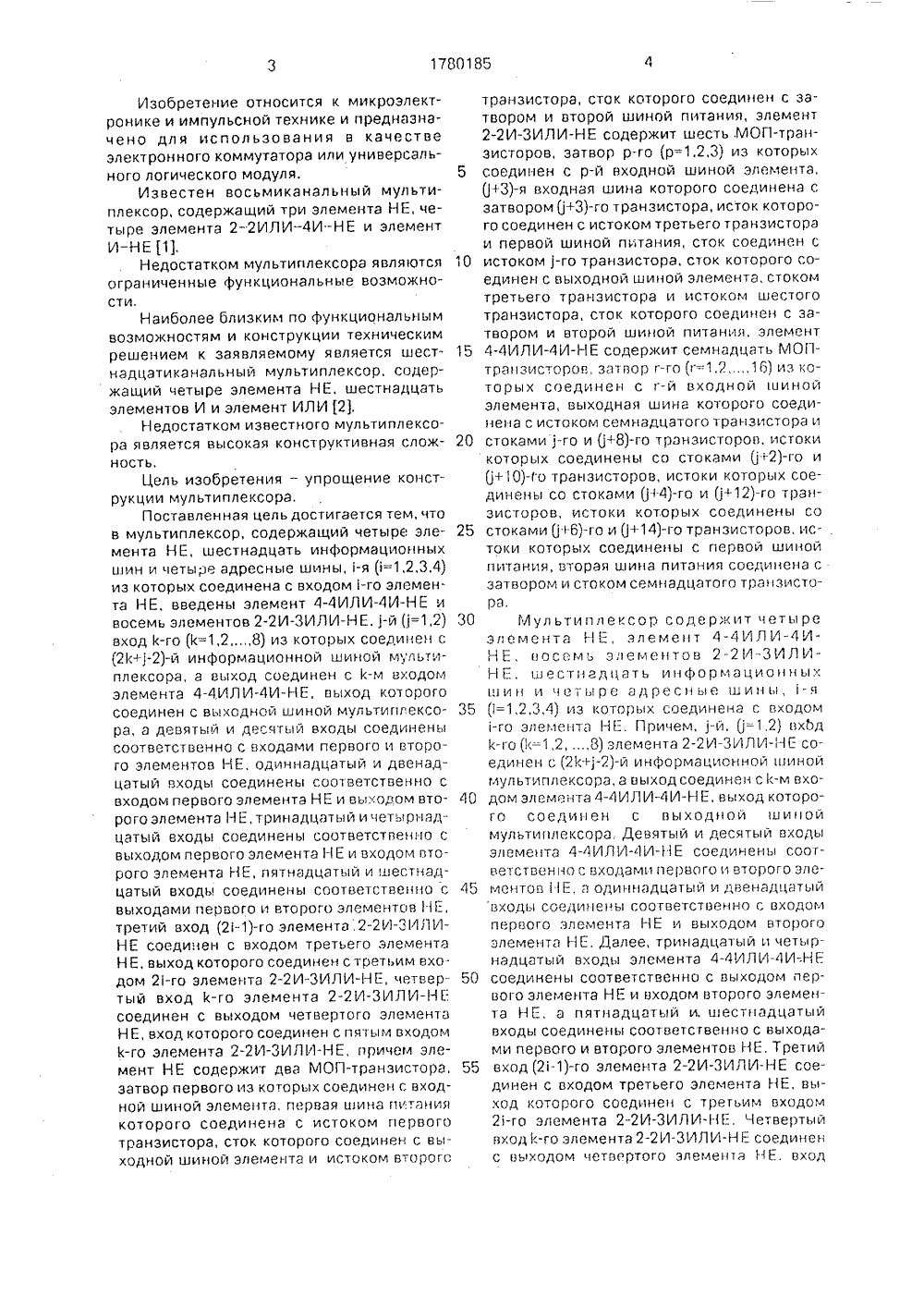

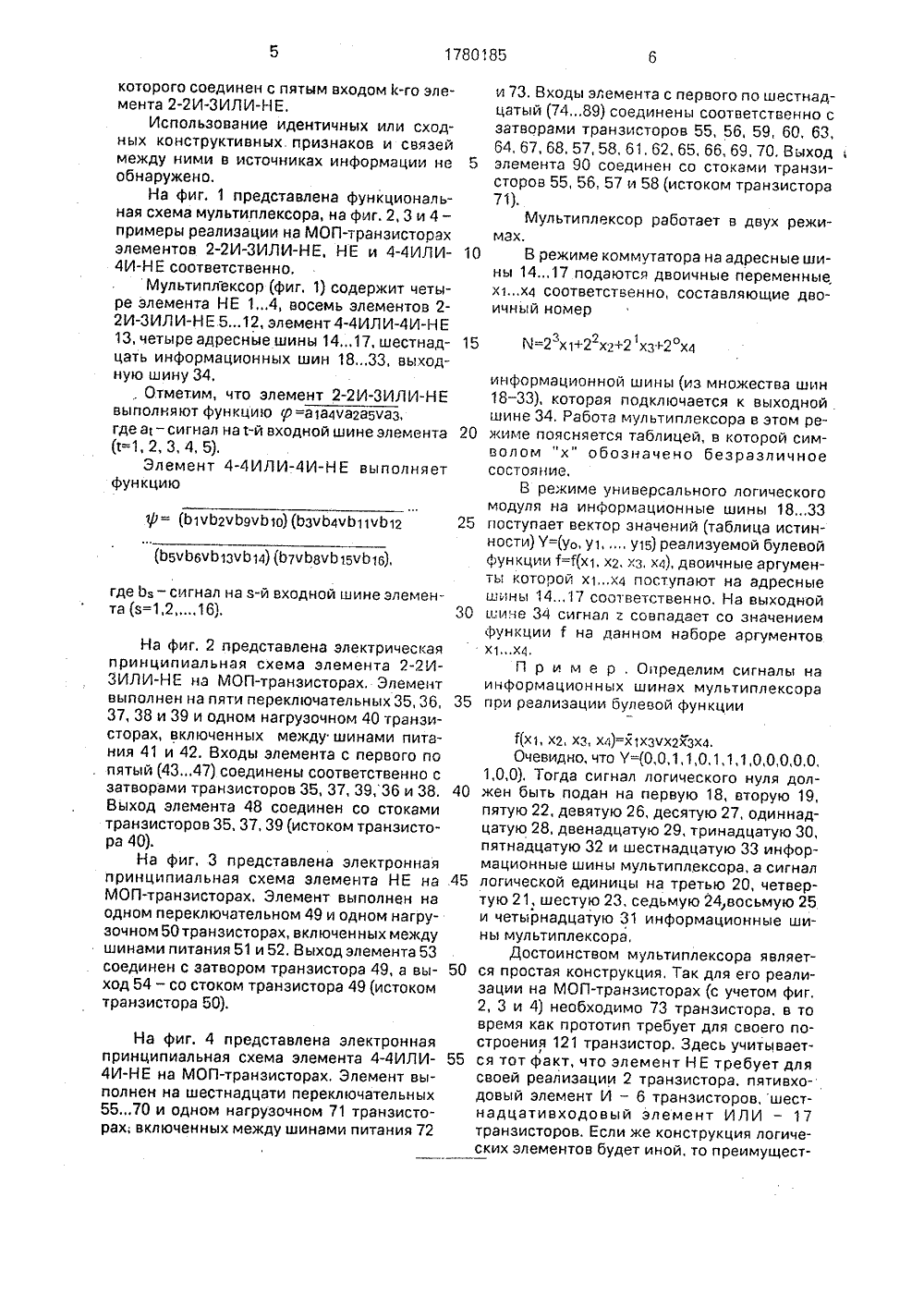

(5)5 Н 03 К 19/094 ПИСАНИЕ ИЗОБРЕТ ИЯ,54) МУЛ ЬТИ ПЛ Е КСО Р СО Уи ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(56) Авторское свидетельство СССРМ 1538248, кл. Н 03 К 19/094, 1988.Интегральные микросхемы: Справочник (под ред. Б. В. Тарабарина - М.: Радиои связь, 1984 - с. 68(прототип).(57) Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора или универсального логического модуля. Сущность изобретения: поставленная цель достигается тем, что 16-канальный мультиплексор содержит четыре элемента НЕ 1-4. восемь элементов 2 - 2 И - 3 ИЛИ - НЕ 5 - 12, элемент 4 - 4 ИЛИ - 4 И-НЕ 13, четыре адресные шины 14 - 17, шестнадцать информационных шин 18 - 33 и выходную шину 34. Сложность мультиплексора по числу МОП-транзисторов равна 73, 4 ил.Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора или универсального логического модуля.Известен восьмиканальный мультиплексор, содержащий три элемента НЕ, четыре элемента 2-2 ИЛИИ-НЕ и элемент И - НЕ (11,Недостатком мультиплексора являются ограниченные функциональные возможности.Наиболее близким по функциональным возможностям и конструкции техническим решением к заявляемому является шестнадцатикэнальный мультиплексор, содержащий четыре элемента НЕ, шестнадцать элементов И и элемент ИЛИ (2),Недостатком известного мультиплексора является высокая конструктивная сложность,Цель изобретения - упрощение конструкции мультиплексора.Поставленная цель достигается тем, что в мультиплексор, содержащий четыре элемента НЕ, шестнадцать информационных шин и четыре адресные шины, -я (1=1,2,3,4) из которых соединена с входом 1-го элемента НЕ, введены элемент 4-4 ИЛИИ-НЕ л восемь элементов 2-2 И-ЗИЛИ-НЕ, )-й =1,2) вход М-го (1=1,2,8) из которых соединен с (2 Р+1-2)-й информационной шиной мультиплексора, а выход соединен с 1-м входом элемента 4-4 ИЛИИ-НЕ, выход которого соединен с выходной шиной мультиплексора, д девятый и десятыл входы соединены соответственно с входами первого и второго элементов НЕ, одиннадцатый л двенадцатый входы соединены соответственно с входом первого элемента НЕ и выходом второго элемента НЕ, тринадцатый и четырнадцатый входы соединены соответственно с выходом первого элемента НЕ и входом второго элемента НЕ, пятнадцатый и шестнадцатый входы соединены соответственно с выходами первого и второго элементов НЕ, третий вход (21-1)-го элемента,2-2 И-ЗИЛИНЕ соединен с входом третьего элемента НЕ, выход которого соединен с третьим входом 21-го элемента 2-2 И-ЗИЛИ-НЕ, четвертый вход 1-го элемента 2-2 И-ЗИЛИ-НЕ соединен с выходом четвертого элемента НЕ, вход которого соединен с пятым входом М-го элемента 2-2 И-ЗИЛИ-НЕ, причем элемент НЕ содержит два МОП-транзистора, затвор первого из которых соединен с входной шиной элемента, первая шина питания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго 5 10 15 20 25 30 35 40 45 50 транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2-2 И-ЗИЛИ-НЕ содержит шесть МОГ 1-транзисторов, затвор р-га (р=1,2,3) из которых соединен с р-й входной шиной элемента, +3)-я входная шина которого соединена с затвором Д+3)-го транзистора, исток которого соединен с истоком третьего транзистора и первой шиной питания, сток соединен с истоком 1-го транзистора, сток которого соединен с выходной шиной элемента, стоком третьего транзистора и истоком шестого транзистора, сток которого соединен с затвором и второй шиной питания, элемент 4-4 ИЛИИ-НЕ содержит семнадцать МОП- транзисторов, затвор г-го(г=1,2, ,16) из которых соединен с г-й входной шиной элемента, выходная шина которого соединена с истоком семнадцатого транзистора и стоками )-го и +8)-го трднзисторов, истоки которых соединены са стоками +2)-го и +10)-го транзисторов, истоки которых соединены со стоками +4)-га и Ц)-го транзисторов, истоки которых соединены со стоками1 8)-го и +14)-го транзисторов, ис- . токи которых соединены с первой шиной питания, вторая шина питания соединена с затвором и стоком семнадцатого транзистора,Мультиплексор содержит четыре элемента Н Е, элемент 4-4 ИЛИИНЕ, восемь элементов 2-2 И-ЗИЛИНЕ, шестнадцать информационных шин и четыре адресные шины, 1-я (1=1,2,3,4) из которых соединена с входом 1-га элемента НЕ. Причем, 1-й, (1=1,2) вхбд к-га (1 - -1,2, 8) элемента 2-2 И-ЗИЛИ-НЕ соединен с (21:+)-2)-й информационной шиной мультиплексора, а выхадсаединен с 1-м входом элемента 4-4 ИЛИИ-Н Е, выход которого соединен с выходной шиной мультиплексора Девятый и десятый входы элемента 4-4 ИЛИИ-НЕ соединены соответственно с входами первого и второго элементов НЕ. д одиннадцатый и двенадцатый входы соединены соответственно с входам первого элемента НЕ и выходом второго элементд НЕ, Далее, тринадцатый и четырнадцатый входы элемента 4-4 ИЛИИ-,НЕ соединены соответственно с выходом первого элемента НЕ и входам второго элемента НЕ, а пятнадцатый и, шестнадцатый входы соединены соответственно с выходами первого и второго элементов НЕ. Третий вход(21-1)-го элемента 2-2 И-ЗИЛИ-НЕ соединен с входом третьего элемента НЕ, выход которого соединен с третьим входом 21-го элемента 2-2 И-ЗИЛИ-НЕ. Четвертый вход 1.-га элемента 2-2 И-ЗИЛИ-Н Е соединен с вьходом четвертого элемента НЕ. входкоторого соединен с пятым входом -го элемента 2-2 И-ЗИЛИ-НЕ.Использование идентичных или сходных конструктивных. признаков и связеймежду ними в источниках информации не 5обнаружено,Ка фиг. 1 представлена функциональная схема мультиплексора, на фиг. 2, 3 и 4 -примеры реализации на МОП-транзисторахэлементов 2-2 И-ЗИЛИ-НЕ, НЕ и 4-4 ИЛИ4 И-НЕ соответственно,Мультиплексор (фиг. 1) содержит четыре элемента НЕ 14, восемь элементов 22 И-ЗИЛ И-Н Е 512, элемент 4-4 ИЛ ИИ-Н Е13, четыре адресные шины 14.17, шестнадцать информационных шин 1833, выходную шину 34., Отметим, что элемент 2-2 И-ЗИЛИ-НЕвыполняют функцию гр =а 1 аача 2 а 5 чаз,где а 1- сигнал на 1-й входной шине элемента 20(Ь 5 ч Ьбч Ь 1 зч Ь 14) 1 Ь 7 ч Ь 8 ч Ь 15 ч Ь 16),где Ь - сигнал на з-й входной шине элемента (э=1,2 16). 30На фиг. 2 представлена электрическая принципиальная схема элемента 2-2 ИЗИЛИ-НЕ на МОП-транзисторах, Элемент выполнен на пяти переключательных 35, 36, 35 37, 38 и 39 и одном нагрузочном 40 транзисторах, включенных между шинами питания 41 и 42. Входы элемента с первого по пятый (4347) соединены соответственно с затворами транзисторов 35, 37, 39,36 и 38. 40 Выход элемента 48 соединен со стоками транзисторов 35, 37, 39 истоком транзистора 40).На фиг. 3 представлена электронная принципиальная схема элемента НЕ на 45 МОП-транзисторах. Элемент выполнен на одном переключательном 49 и одном нагрузочном 50 транзисторах, включенных между шинами питания 51 и 52. Выход элемента 53 соединен с затвором транзистора 49, а вы ход 54 - со стоком транзистора 49 (истоком транзистора 50).На фиг. 4 представлена электронная принципиальная схема элемента 4-4 ИЛИ 4 И-НЕ на МОП-транзисторах, Элемент выполнен на шестнадцати переключательных 5570 и одном нагрузочном 71 транзисторах; включенных между шинами питания 72 и 73. Входы элемента с первого по шестнадцатый (7489) соединены соответственно с затворами транзисторов 55, 56, 59, 60, 63, 64,67,68,57,58, 61,62. 65,66, 69,70. Выход элемента 90 соединен со стоками транзисторов 55, 56, 57 и 58 (истоком транзистора 71).Мультиплексор работает в двух режимах,В режиме коммутатора на адресные шины 1417 подаются двоичные переменные х 1 ха соответственно, составляющие двоичный номерК=2 х 1+2 х 2+2 хз+2 х 4информационной шины из множества шин 18 - ЗЗ), которая подключается к выходной шине 34. Работа мультиплексора в этом режиме поясняется таблицей, в которой символом "х" обозначено безразличное состояние,В режиме универсального логического модуля на информационные шины 1833 поступает вектор значений (таблица истинности) У=(у 0, у 1, у 15) реализуемой булевой функции 1=г(х 1. х 2, хз, ха), двоичные аргументы которой х 1 ха поступают на адресные шины 14,17 соответственно. На выходной шине 34 сигнал г совпадает со значением функции 1 на данном наборе аргументов х 1.ха.П р и м е р . Определим сигналы на информационных шинах мультиплексора при реализации булевой функции1(х 1, х 2, хЗ, ха)=х 1 хЗчх 2 хЗха.Очевидно, что У=0,0,1,1,0,1,1,1,0,0,0,0,0, 1,0,0). Тогда сигнал логического нуля должен быть подан на первую 18, вторую 19, пятую 22, девятую 26, десятую 27, одиннадцатую 28, двенадцатую 29, тринадцатую 30, пятнадцатую 32 и шестнадцатую 33 информационные шины мультиплексора, а сигнал логической единицы на третью 20, четвертую 21, шестую 23, седьмую 24,восьмую 25 и четырнадцатую 31 информационные шины мультиплексора,Достоинством мультиплексора является простая конструкция, Так для его реализации на МОП-транзисторах с учетом фиг, 2, 3 и 4) необходимо 73 транзистора. в то время как прототип требует для своего построения 121 транзистор. Здесь учитывается тот факт, что элемент НЕ требует для своей реализации 2 транзистора. пятивходовый элемент И - 6 транзисторов,шестнадцативходовый элемент ИЛИ - 17 транзисторов. Если же конструкция логических элементов будет иной, то преимущест 1780185во в простоте построения предлагаемого мультиплексора сохранится, хотя абсолютные цифры,например, количество транзисторов) могут измениться, Это обусловлено тем, что мультиплексор имеет также и наи меньшую сложность по числу входов логических элементов среди известных шестнадцатиканальных мультиплексоров, что является одним из основных факторов, определяющих сложность принципиальной 10 схемы устройства на уровне транзисторов.формула изобретенияМультиплексор, содержащий четыре элемента НЕ, шестнадцать информационных шин и четыре адресные шины, 1-я 15 (=1,2,3,4) из которых соединена с входом -го элемента НЕ, о т л и ч а ю щ и й с я тем, что, с целью упрощения, содержит элемент 4-4 ИЛИИ-НЕ и восемь элементов 2-2 И-ЗИЛИ-НЕ,)-й Д=1,2) вход К-го (И,2,8) из 20 которых соединен с (2 К+)-2)-й информационной шиной мультиплексора, а выход соединен с 1-м входом элемента 4-4 ИЛИИ-НЕ, выход которого соединен с выходной шиной мультиплексора, а девятый и десятый входы 25 соединены соответственно с входами первого и второго элементов Н Е, одиннадцатый и двенадцатый входы соединены соответственно с входом первого элемента НЕ и выходом второго элемента Н Е, тринадцаты й и 30 четырнадцатый входы соединены соответственно с выходом первого элемента НЕ и входом второго элемента НЕ, пятнадцатый и шестнадцатый входы соединены соответственно с выходами первого и второго эле ментов НЕ, третий вход (21-1)-го элемента 2-2 И-ЗИЛИ-НЕ соединен с входом третьего элемента НЕ, выход которого соединен с третьим входом 21-го элемента 2-2 И-ЗИЛИНЕ, четвертый вход 1-го элемента 2-2 ИЗИЛИ-НЕ соединен с выходом четвертого элемента Н Е, вход которого соединен с пятым входом М-го элемента 2-2 И-ЗИЛИ-НЕ, причем элемент НЕ содержит два МОП- транзистора, затвор первого из которых соединен с входной шиной элемента, первая шина питания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2-2 И-ЗИЛИ-НЕ: содержит шесть МОП-транзисторов, затвор р-го р=1,2,3) из которых соединен с р-й входной шиной элемента, Я+3)-я входная шина которого соединена с затвором +3)-го транзистора, исток которого соединен с истоком транзистора и первой шиной питания, сток соединен с истоком)-го транзистора, сток которого соединен с выходной шиной элемента, стоком третьего транзистора и истоком шестого транзистора, сток которого соединен с затвором и второй шиной питания, элемент 4-4 ИЛИИ-НЕ содержит семнадцать МОП-транзисторов, затвор г-го (г,2,.,16) из которых соединен с г-й, входной шиной элемента, выходная шина которого соединена с истоком семнадцатого транзистора и стоками )-го Ц+8)-го транзисторов, истоки которых соединены со стоками Д+2)- и +10)-го транзисторов, истоки которых соединены со стоками Д+4)- и Ц+12)-го трагисторов, истоки которых соединены со стоками Я+6)- и Я+14)-го транзисторов, истоки которых соединены с первой шиной питания, вторая шина питания соединеа с затвором и стоком семнадцатого тразистора.1730 Я 5 7 б Л Ви. Составитель В,СупрунТехред М.Моргентал Корректор М.Дем едактор С.Кулак каз 4441 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раущская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 10

СмотретьЗаявка

4882255, 11.11.1990

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ, БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, СУПРУН ВАЛЕРИЙ ПАВЛОВИЧ, ФУРАШОВ НИКОЛАЙ ВЛАДИМИРОВИЧ, КОСТЕНЕВИЧ ВАЛЕРИЙ ИВАНОВИЧ

МПК / Метки

МПК: H03K 19/094

Метки: мультиплексор

Опубликовано: 07.12.1992

Код ссылки

<a href="https://patents.su/5-1780185-multipleksor.html" target="_blank" rel="follow" title="База патентов СССР">Мультиплексор</a>

Предыдущий патент: Мдп-инвертор

Следующий патент: Формирователь импульсов с регулируемой частотой следования

Случайный патент: Устройство для стабилизации сварочной дуги переменного тока