Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

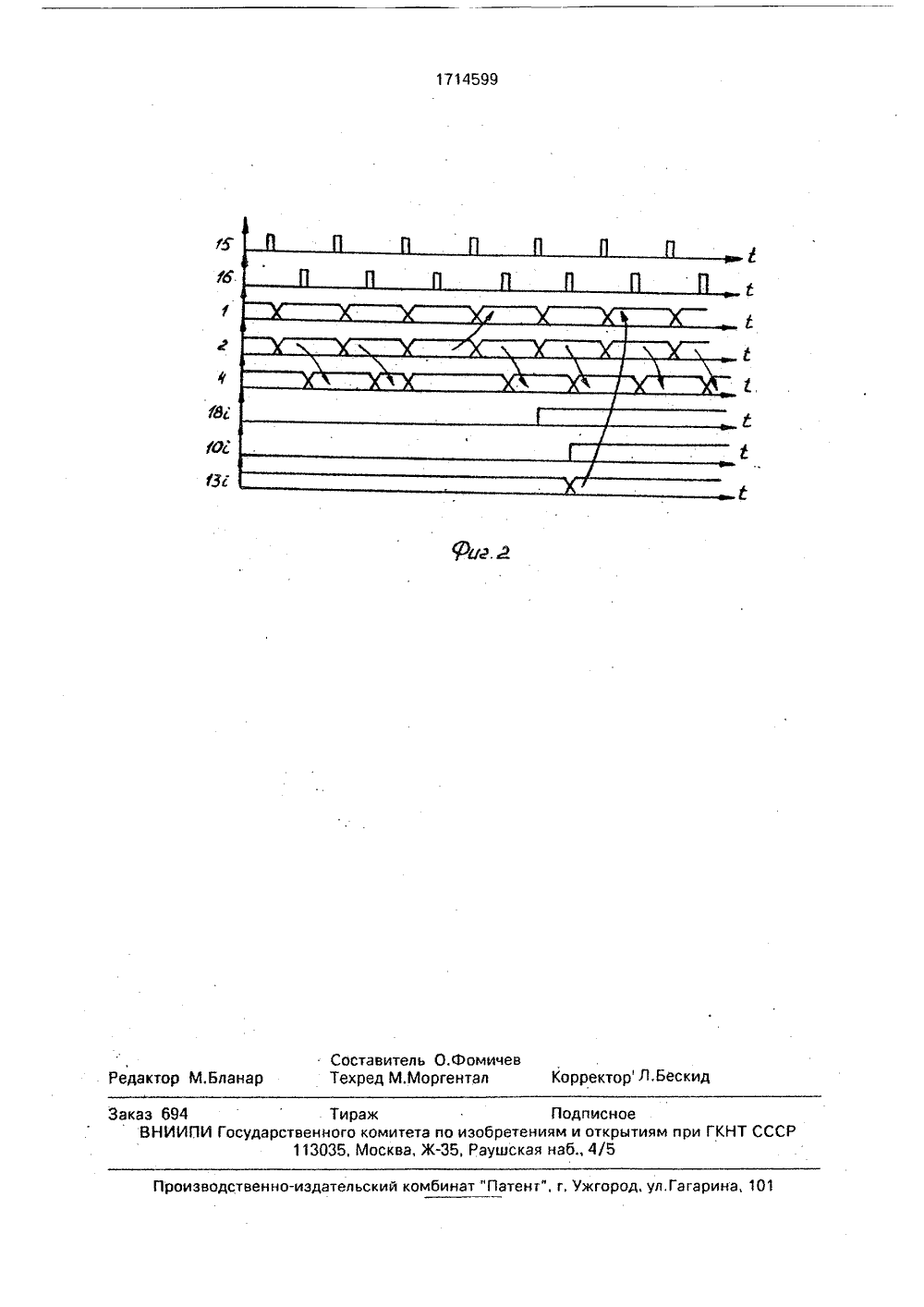

(9 06 Е 9/22 САНИЕ ИЗОБРЕТЕНИ ИДЕТЕЛ ЬСТВУ К АВТОРСКОМ(54) ПРОГРАММИРУЕМЫЙ КОНТР (57) Изобретение относится к автом вычислительной технике и может б пользовано в системах автоматичес равления технологическими проц Цель изобретения - повышение быс ствия контроллера путем организац рывания выполнения подпрогра любом этапе ее выполнения при изм значения приоритетного логическ ройства. Программируемый контрол держит счетчик адреса 1, блок пос ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР(56) Авторское свидетельство СССР Ь 1310776, кл. 6 05 В 19/08, 1987.Харченко В,С. и др. Основы построения микроконтроллеров АСКУ, МО СССР, 1989. ОЛЛЕР атике и ыть иского упессами. тродейии преммы на енении ого устлер сотоян ной1714599 памяти микропрограмм 2, мультиплексор 3, регистр 4, элемент И 5, коммутатор 6, элемент ИЛИ 7, приоритетный элемент 8, группу блоков контроля датчиков 9. Счетчик адреса 1 обеспечивает выбор соответствующей микрокоманды из блока постоянной памяти микропрограмм 2 в соответствии с Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах автоматического управления технологическими процессами,Известно устройство для программного управления циклическими процессами, содержащее генератор импульсов, делитель частоты, первый времязадающий блок, блок набора программ, блок испытаний органов, блок сигнализации, блок обнуления, блок датчиков окончания операций, блок сравнения, счетчик адреса, шифратор, дешифратор, второй и первый ВБ-триггеры, блок элементов ИЛИ,Недостатком данного устройства является узкая область применения и низкое быстродействие,Наиболее близким к предлагаемому является контроллер, содержащий счетчик, блок памяти, мультиплексор, регистр, элемент И, причем первый вход синхронизации контроллера соединен с входом счетчика, выход которого соединен с адресным входом блока памяти, первая группа выходов которого соединена с первым входом элемента И и инверсным Ч-входом регистра. Вторая группа выходов блока памяти соединена с адресным входом мультиплексОра и первой группой О-входов регистра, третья группа выходов блока памяти соединена с второй группой выходов регистра и О-входами счетчика, входы логических условий устройства соединены с О-входами мультиплексора, выход которого соединен со вторым входом .элемента И, выход которого соединен с Ч-входом счетчика, второй вход синхронизации контроллера соединен с С- входом регистра, выход которого является выходом микроопераций контроллера,Недостатком этого контроллера является низкая область применения, обусловленная невозможностью использования алгоритмов, содержащих приоритетные логические устройства. Цель изобретения - повышение быстродействия путем организации прерывания выполнения подпрограммы на любом этапе алгоритмом работы контроллера. Приоритетный элемент 8 обеспечивает выбор адреса перехода к подпрограмме в зависимости от приоритета проверяемого логического условия при одновременном изменении нескольких приоритетных логических условий. 2 ил. ее выполнения при изменении значения приоритетного логического условия,На фиг.1 представлена функциональнаясхема программируемого контроллера; на 5 фиг.2 - временная диаграмма функционирования программируемого контроллера.Программируемый контроллер (фиг.1)содержит счетчик 1 адреса, блок 2 постоянной памяти микропрограмм, мультиплексор 10 3, регистр 4, элемент И 5, коммутатор 6.элемент ИЛИ 7, приоритетный элемент 8, группу блоков 9 контроля датчиков, каждый из которых содержит триггер 10, йервый 11 и второй 12 одновибраторы, шифратор 13, 15 элемент ИЛИ 14, первый вход 15 синхронизации устройства, второй вход 16 синхронизации, вход 17 логических условий, вход 18 приоритетных логических условий, выход 19 микроопераций.20 Счетчик 1 адреса предназначен дляобеспечения выбора соответствующей микрокоманды из блока 2 постоянной памяти микропрограмм в соответствии с алгоритмом работы программируемого контролле ра.Блок 2 постоянной памяти микропрограмм предназначен для хранения микропрограммреализуемых данным контроллером. В нем хранятся микрокоман ды двух типов: линейные микрокоманды имикрокоманды ветвления. Каждая микрокоманда состоит из трех частей: микрооперационная (адресная) часть, поле метки и поле логических условий.35 Линейные микрокоманды содержатмикрооперационную часть, а в полях метки и логических условий записаны нули,Микрокоманды ветвления содержат адрес микрокоманды, к которой происходит 40 переход микропрограммы в случае равенства проверяемого логического условия "1", причем этот адрес расположен там же, где и микрооперационная часть в линейной микрокоманде, в поле логических условий 45 записан код адреса проверяемых логических условий, а в поле метки записана "1",Мультиплексор 3 предназначен для выбора проверяемого логического условия вны нулю,Таким образом, на адресном входе блока 2 постоянной памяти микропрограмм находится адрес, содержащий только нули,считываЮтся данные из ячейки блока 2 постоянной памяти микропрограмм с нулевымадресом.По заднему фронту первого актовогоимпульса, поступающего на первый вход 15синхронизации устройства, соединенный сС-входом счетчика 1 адреса, последний переходит в очередное состояние, происходитобращение к очередной (первой) ячейкеблока 2 постоянной памяти микропрограмм, в которой записан начальный адрес 45микрокоманды. По заднему фронту первоготактового импульса, поступающему на вто- срой вход 16 синхронизации контроллера,микрооперационная часть данной микроко- иманды записывается в регистр 4, поступая 50 тна выход 19 микроопераций контроллера ((фиг.2). По второму тактовому импульсу, по- нступающему на первый вход 15 синхрониза- Вции контроллера, счетчик 1 адреса тпереходит в очередное состояние, обраща иясь к следующей ячейке блока 2 постоянной . нпамяти микропрограмм. По второму тактовому импульсу, поступающему на второйвход 16 синхронизации контроллера, мик- грооперэционная часть очередной микроко- р зависимости от управляющих сигналов, поступивших на его адресный вход.Регистр 4 предназначен для временного хранения микрооперационной части считываемой микрокоманды и выдачи ее на выход 19 микроопераций контроллера.Элемент И 5, коммутатор 6, элемент ИЛИ 7 предназначены для управления счетчиком 1 адреса.Приоритетный элемент 8 предназначен для организации выбора адреса перехода к подпрограмме в зависимости от приоритета проверяемого приоритетного логического условия при одновременном изменении нескольких приоритетных логических условий.Блок 9 контроля датчиков 9 ( = 1, и) предназначен для формирования адреса перехода к соответствующей части подпрограммы.при изменении 1-го приоритет ного логического условия, а также для формирования сигнала, управляющего счетчиком 1 адреса,Программируемый контроллер работает следующим образом,В исходном состоянии триггеры 10 всехблоков контроля датчиков, счетчик 1 адреса,регистр 4 находятся в нулевом состоянииВсе приоритетные логические условия рав- З 0 манды записывается в регистр 4 и поступаетна выход 19 микроопераций контроллера,Далее контроллер работает аналогичнымобразом до тех пор, пока не считана микрокоманда ветвления, в поле метки которойзаписана единица, в отличие от линейноймикрокоманды, в поле метки которой записан ноль,Как только на выходе блока 2 постоянной памяти микропрограмм появляетсямикрокоманда ветвления, единица из ее поля метки обнуляет регистр 4 (фиг.2) и поступает на второй вход элемента И 5 и (и+1)-йвход коммутатора 6. В поле микрооперациймикрокоманд ветвления записан адрес микрокоманды перехода, к которой происходитпереход к микропрограмме в случае выполнения проверяемых логических условий, кодадреса которых записан в поле логическихусловий данной микрокоманды ветвления.Мультиплексор 3 коммутирует проверяемоелогическое условие, поступающее на его01-вход с входов 17 логических и входов 18приоритетных логических условий контроллера. Если проверяемое логическое условиеравно "1", то элемент И 5 открывается иединица с его выхода через элемент ИЛИ 7поступает на Ч-вход счетчика 1 адреса, переводя его в режим записи,По очередному тактовому импульсу, поступающему нэ первый вход 15 синхронизации контроллера (фиг.2), адрес очередноймикрокоманды, к которой происходит переход, проходя через (и+1)" вход коммутатора6, записывается в счетчик 1 адреса. Далееконтроллер работает аналогично.В случае, когда проверяемое логическоеусловие равно нулю, а элемент И 5 закрыт исчетчик 1 адреса по очередному таковомуимпульсу, поступающему с первого входа 15синхронизации контроллера, переходит вочередное состояние.В случае изменения 1-го приоритетногологического условия ( = Гп) контроллер работает следующим образом.По очередному тактовому импульсу, потупающему с второго входа 16 синхронизации контроллера после изменения 1-гориоритетного логического условия (фиг,2),риггер 10 1-го блока 9 контроля датчиков1 = 1, и) переходит в единичное состояние,а его прямом выходе появляется единица.результате на выходе первого одновибраора 11 1-го блока контроля датчиков ( =- 1,) появляется единичный импульс, длительость которого удовлетворяет условию1и Тимп - П,2де и - период следования импульсов синхонизации контроллера.Этот импульс, пройдя через элемент ИЛИ 14 1-го блока 9 контроля датчиков(1 =1, и), поступает на 1-й вход приоритетного элемента 8, на 1-й вход элемента ИЛИ 7. На 1-м входе приоритетного элемента 8 появляется единичный потенциал открывающий 1-й вход коммутатора 6 ( = 1, и), на О-вход счетчика 1 поступает адрес микрокоманды, к которой должен осуществиться переход микропрограммы при переходе в единицу 5 10 1-го приоритетного логического условия, Этот адрес поступает с выхода шиФратора 13 1-го блока 9 контроля датчиков (1 - 1, и). Данный шифратор 13 вырабатывает два адреса в зависимости от состояния 1-го при оритетного логического условия (1 1, и).Единичный импульс, проходя через элемент ИЛИ 7 на Ч-вход счетчика 1 адреса, переводит последний в режим записи, и по20очередному тактовому импульсу, поступающему на первый вход 15 синхронизацииконтроллера, адрес с выхода шифратора 131-го блока 9 контроля датчиков (1 - 1, и),пройдя через коммутатор 6, записывается всчетчик 1, Таким образом, происходитпереход к соответствующей части микрокоманды, записанной в блоке 2 постояннойпамяти микропрограмм.В случае, когда по одному тактовомуимпульсу, поступающему с второго входа 16 30синхронизации контроллера, происходитизменение состояния триггера 10 более чемв одном блоке 9 контроля датчиков, контроллер работает следующим образом.Допустим, произошло изменение состояния триггера 10 в 1 и ) блоках 9 контролядатчиков (1 = 1 и), ( - 1.и), причем 1),Тогда одновременно единичный импульспоявится на выходе элемента ИЛИ 14 1-го и)-го блоков контроля датчиков. Эти импульсы поступают на 1-й и )-й входы приоритетного элемента 8, Но иэ его и выходовединичный импульс появляется только на1"м выходе.Таким образом, открыт только 1-й 0- 45е вход коммутатора 6, смещения адресов непроисходит,Далее контроллер работает аналогично,Ф о р мул э изобретен ияПрограммируемый контроллер, содержащий счетчик адреса, блок постоянной памяти микропрограмм, мультиплексор,регистр и элемент И, причем синхровходсчетчика адреса является первым входомсинхронизации контроллера, а выходы счетчика адреса соединены с адресными входами блока постоянной памяти микропрограмм, микрооперационные выходы блока постоянной памяти микропрограмм - с информационными входами регистра, выходы которого являются выходами микроопераций контроллера, выход метки блока постоянной памяти микропрограмм соединен с входом сброса регистра и первым входом элемента И, выходы логических условий блока постоянной памяти микропрограмм соединены с адресными входами мультиплексора, выход которого соединен с вторым входом элемента И, первая группа информационных входов мультиплексора является группой входов логических условий контроллера, синхровход регистра соединен с вторым входом синхронизации контроллера, о тл и ч э ю щи й с я тем, что, с целью повышения быстродействия контроллера, в него введены коммутатор, элемент ИЛИ, приоритетный элемент и группа блоков контроля датчиков, каждый из которых содержит триггер, первый и второй одновибраторы, шифратор и элемент ИЛИ, причем микрооперационные выходы и выход метки блока постоянной памяти микропрограмм соединены соответственно с информационными входами и входом разрешения коммутатора, выходы которого соединены с информационными входами счетчика адреса, группа входов приоритетных логических условий контроллера соединена с второй группой входов мультиплексора, а 1-й разряд группы входов приоритетных логических условий контроллера соединен с информационным входом триггера 1-го ( " Г и) блока контроля датчиков группы, прямой и инверсный выходы которого соединены с соответствующими входами шифратора и соответственно с входами первого и второго одновибраторов, выходы которых соединены с соответствующими входами элемента ИЛИ 1-го блока контроля датчиков группы, выход элемента ИЛИ 1-го блока контроля датчиков группы соединен с 1-м (1 - 1, и) входом элемента ИЛИ и приоритетного элемента, выходы которого соединены соответственно с группой входов разрешения коммутатора, выход элемента И соединен с (и+1).м входом элемента ИЛИ, выход которого соединен с входом разрешения счетчика адреса, входы синхронизации триггеров блоков контроля датчиков группы объединены и соединены с вторым входом синхрони.зации контроллера, группа выходов шифратора 1-го блока контроля датчиков группы соединена с группой информационных входов коммутатора,1714599 ГОсСоставитель О.Фомичеведактор М,Бланар Техред М.Моргентал Корректор Л,Бе Заказ 694Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб., 4/5оизводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 10

СмотретьЗаявка

4841583, 03.05.1990

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

КЛЕПАНДА АЛЕКСАНДР СЕРГЕЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БУЦКИЙ АНДРЕЙ ЕВГЕНЬЕВИЧ, ЛИТВИНЕНКО ВАДИМ ГЕОРГИЕВИЧ, ПЕТРЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: контроллер, программируемый

Опубликовано: 23.02.1992

Код ссылки

<a href="https://patents.su/5-1714599-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Устройство пакетной коммутации

Случайный патент: Способ получения незамещенных ci-пиперлзнно-кетонов