Устройство формирования сигнала отсчета для дифференциального кодера изображений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1653178

Авторы: Копылов, Райхельсон

Текст

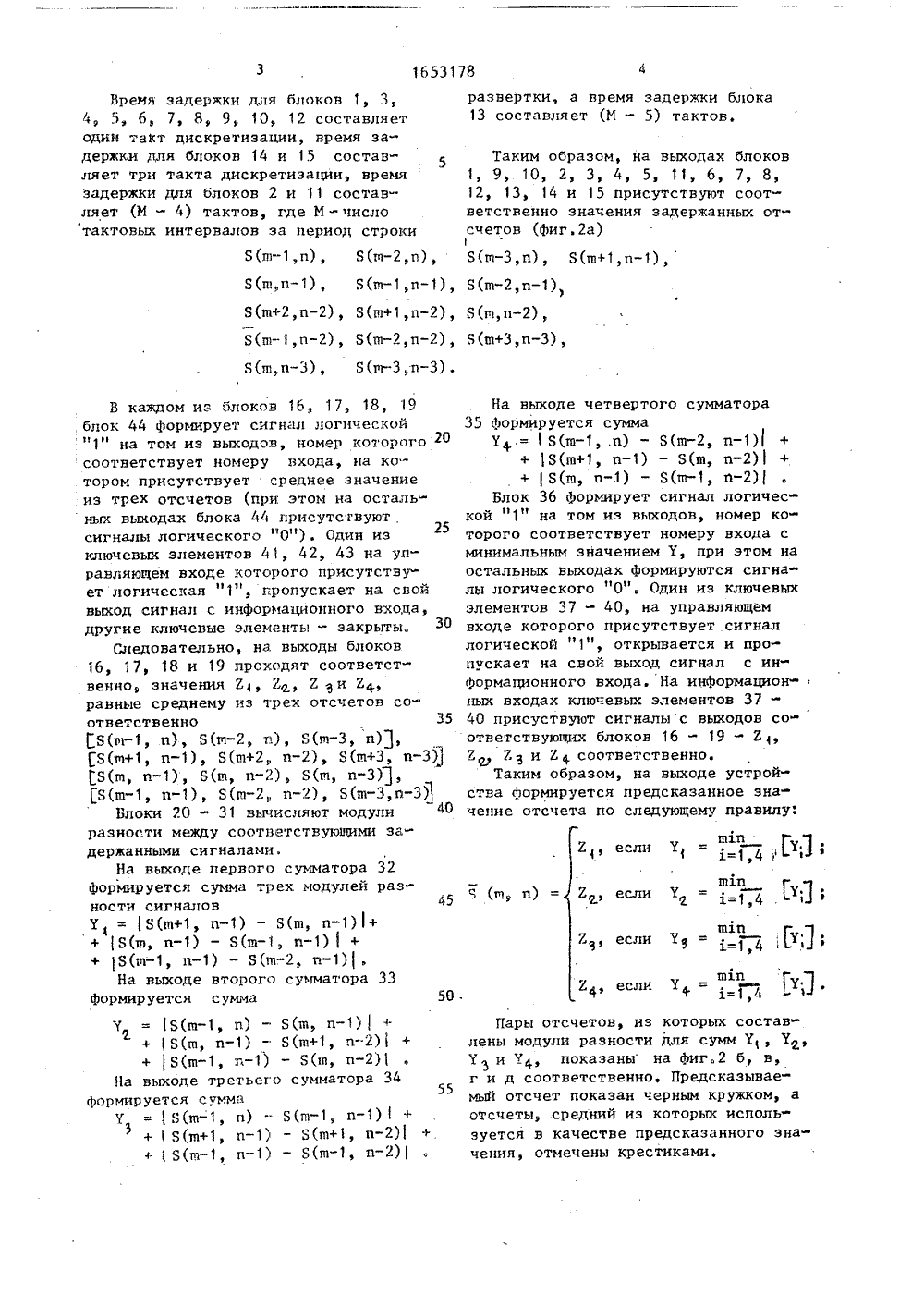

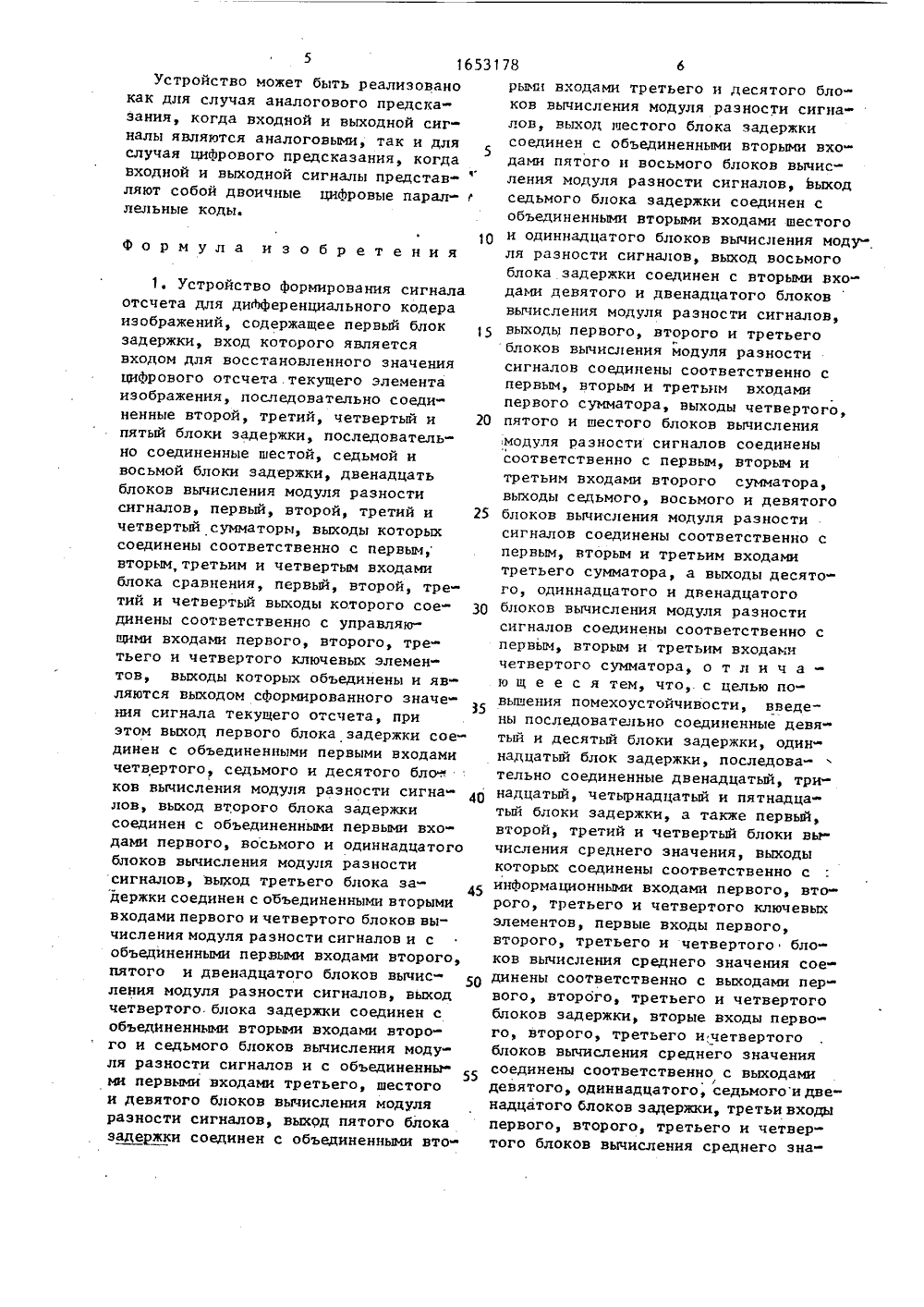

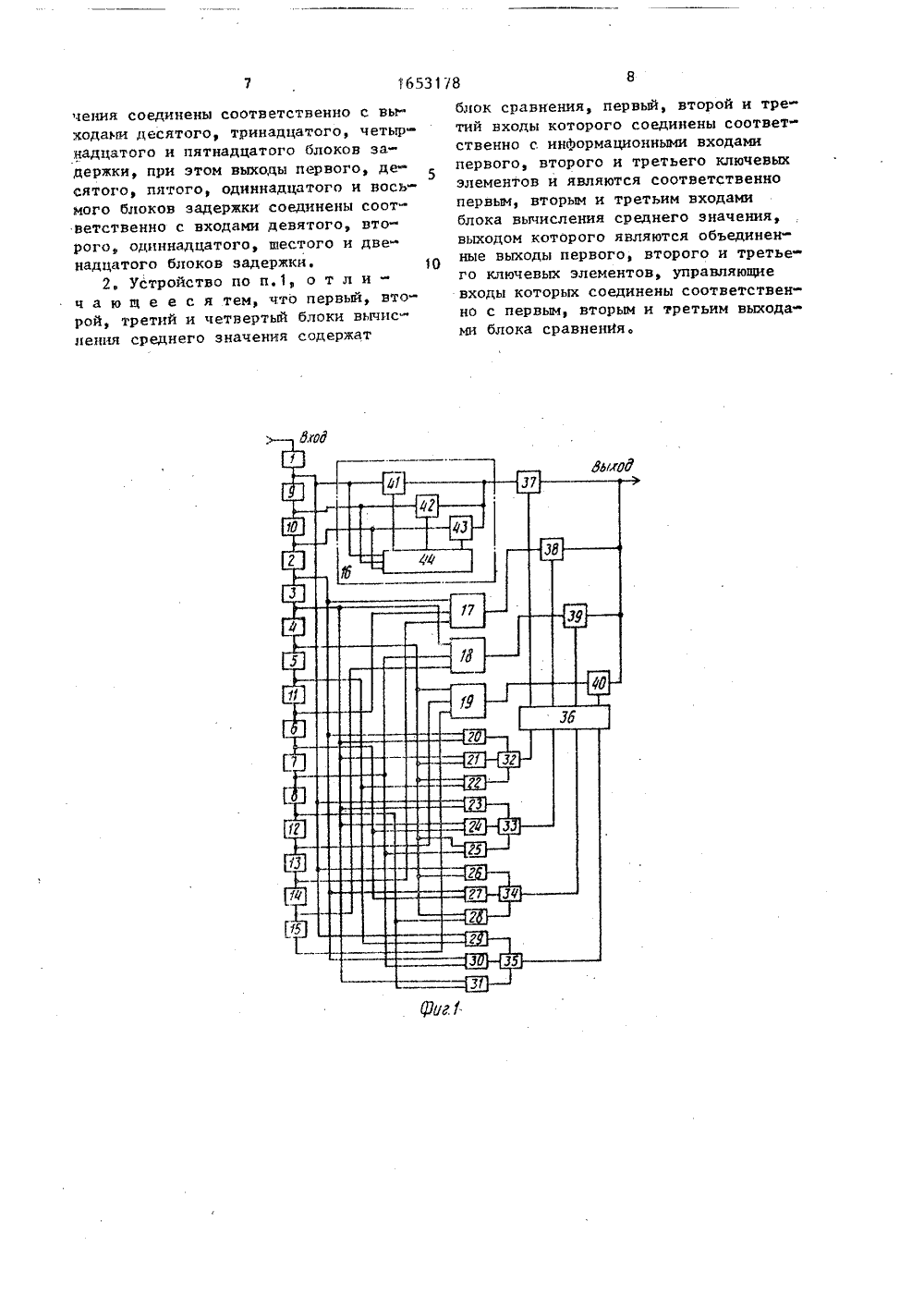

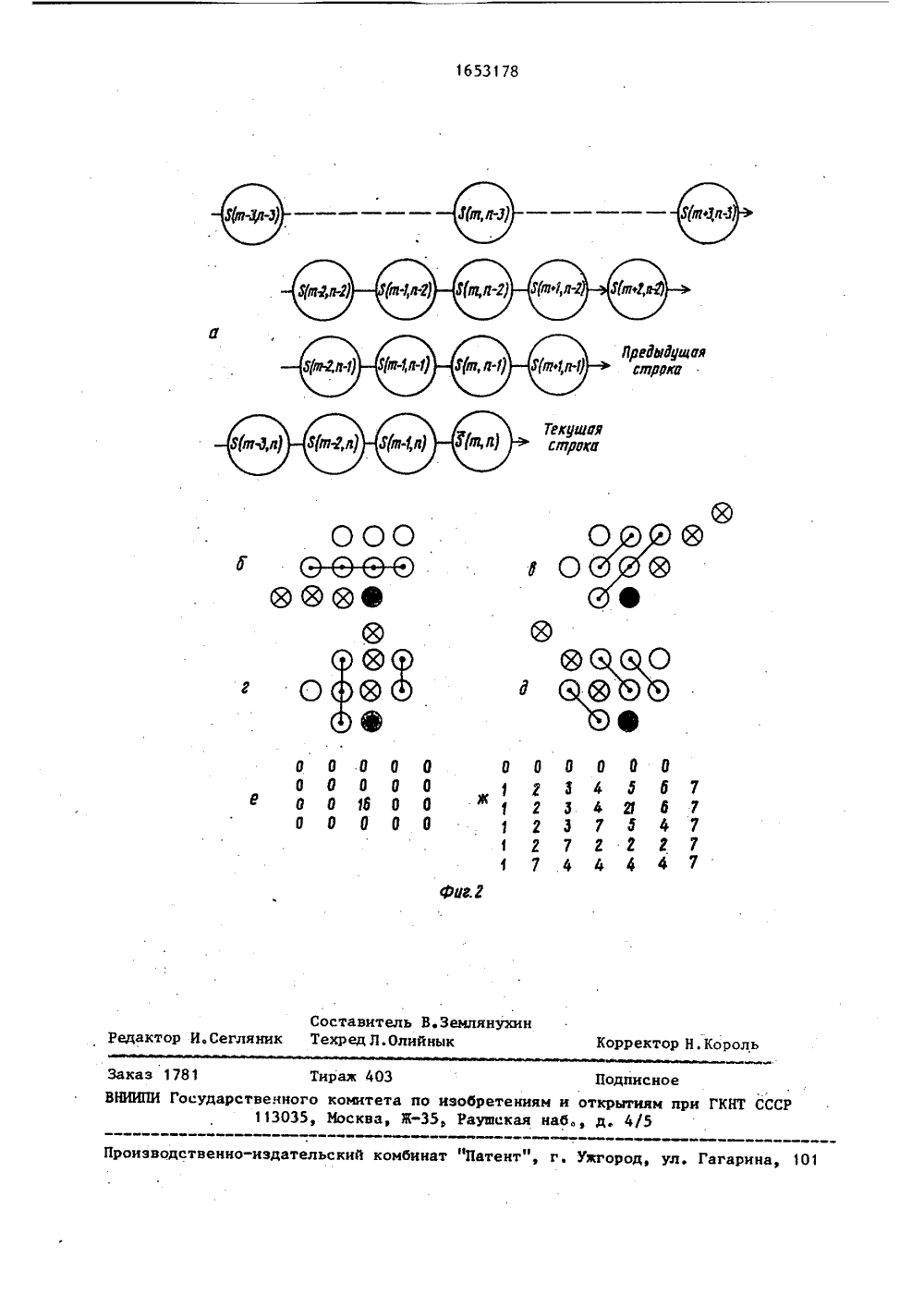

,), Н 04 д 7/13 ИЗОБРЕ ОПИСАН ЕНИЯ НИЯ СИГНАЛА НОГО КОДЕРА ФОРИИРОЕРЕНЦИАЛЪ(54) УСТРОЙСТВООТСЧЕТА ДЛЯ ДИФфИЗОБРАЖЕНИЙ(57) Изобретенидению, Цель изопомехоустойчиворования сигналациального кодер ся к телеви - повьппениеоиство Формидля дифференений содере относибретениясти. Устотсчетаа изобра вычисления модупервый, второй умматорь 1.32. - 35 первый, второй, ключевой элеменкаждый из бпоего значения рой и третий-43 ибл т следую азом устройства и нные значени тупаютотсчет вхо тановле и), гд ражения ки изо во8 е ш - номер элеме в строке, и - н ражения.ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГКНТ СССР ВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Ленинградский электротехнический институт связи им, проф. Х.А.БоБруевича(56) Авторское свидетельство СССРИф 906033, кл. Н 04 М 7/13, 1982. Изобретение относится к телевидению и может быть использовано для цифровой передачи изображений методом диФференциальной импульсно-кодовой модуляции,Цель изобретения - повьппение помехоустойчивости.На Фиг.1 представлена структурная электрическая схема устройства; на Фиг.2 - расположение элементов изображения, используемых для формирования сигнала отсчета.Устройство содержит (фиг.1) первый по пятнадцатый блоки 1 - 15 задержки, первьй второй, третий и четвертый блоки 16 - 19 вычисления среднего значения, первый по двенаджит блоки 1 - 15 задержки, блоки16 - 19 вычисления среднего значения,блоки 20 - 31 вычисления модуля разности сигналов, сумматоры 32 - 35,блок 36 сравнения и ключевые элементы 37 - 40. Цель достигается за счетобеспечения формирования предсказанного значения отсчета по заданному правилу. При этом устройство может бытьреализовано для случаев аналоговогои цифрового предсказания, когда входной и выходной сигналы являются, соответственно, аналоговыми сигналамиили двоичными цифровыми параллельнымикодажт. Устройство по п.2 Формулыотличается вьполнением блоков 1619, каждый из которых состоит из ключевых элементов 41 - 43 и блока 44сравнения. 1 з.п. Ф-лы, 2 ил. цатый блоки 20 - 31ля разности сигналовтретий и четвертый сблок 36 сравнения итретий и четвертый кюты 37 - 40; при этомков вычисления средисодержит первый, втоключевой элементы 4144 сравнения,Устройство работа1653178 Б (в, п),Я (щ,п),тп 1 п 1=1 4 1.Я (щ, и) Время задержки для блоков 1, 3, 4, 5, 6 7, 8, 9, 10, 12 составляет один такт дискретизации, время задержки для блоков 14 и 15 составляет три такта дискретизации время задержки для блоков 2 и 11 составляет (М - 4) тактов, где М - число тактовых интервалов за период строки Я(щп) 1 Б(щ,п),Б(щ+2,п), Б(щ+1,п),Б(щ,п), Б(щ,п),Я(в 1 п-З), Б(тч-З,п-З). В каждом иэ блоков 16, 17, 18, 19блок 44 Формирует сигнал логической"1" на том из выходов, номер которого 20соответствует номеру входа, на котором присутствует среднее значениеиз трех отсчетов (при этом на осталь ных выходах блока 44 присутствуют,сигналы логического О ), Один из11 11 25ключевых элементов 41, 42, 43 на управляющем входе которого присутствует логическая "1", гропускает на свойвыход сигнал с инФормационного входа,другие ключевые элементы - эакрьгтьт,Спедовательно, на. выходы блоков16, 17, 18 и 19 проходят соответственно, значения 21, 22, Е и 2,1.,равные среднему из трех отсчетов соответственно 35Б(т 1 т, п), Б(щ, п), Я(щ-З, и) 1,Я(щ+1, п), Б(тп+2., п), Б(щ+3, п Я (в, п), Б (щ, п), Б (щ 1 и" 3),Б(в, п), Я(вп-), Я(в-З,п-З)Блоки 20 - 31 вычиспяют модули тОразности между соответствующими задержанными сигналами.Иа выходе первого сумматора 32Формируется сумма трех модулей разности сигналовУ=Б(щ+1, и) - Б(в, п)1++ Б(щ, п) - Б(в, и).На выходе второго сумматора 33Формируется сумма 50.Я(щ 1 ф и) Б(в 1 и 1)++Б(тп, и) - Я(в, п)1На выходе третьего сумматора 3455Формируется суммаУ =Я(щ, и) - Б(щ, и)++Я(щ+1, и) - Я(в+1, тт) ь1 Я(в, п) - Я(в, и) развертки а время задержки блока13 составляет (М - 5) тактов. Таким образом, на выходах блоков1, 9, 1 О, 2, 3, 4, 5, 11 6, 7, 8,12, 13, 14 и 15 присутствуют соответственно значения задержанных отсчетов (фиг.2 а)1Я (в-З, и), Б (в+1, п),Я(вп)Я(щ 1 п),Ч(в+3 и) На выходе четвертого сумматора 35 Формируется суммаУ,1.=Б(щп) - Я(щ, п) ++ 1 Б(в+1, п) - Б(щ, и) + +Б(щ, и) - Б(щ, и)Блок 36 Формирует сигнал логической "1" на том из выходов, номер которого соответствует номеру входа с минимальным значением 7, при этом на остальных выходах Формируются сигналы логического "0". Один из ключевых элементов 37 - 40, на управляющем входе которого присутствует сигнал логической "1", открывается и пропускает на свой выход сигнал с инФормационного входа. На инФормационных входах ключевых элементов 37- 40 присуствуют сигналы с выходов соответствующих блоков 16 - 19 - Е , Е Е и Е соответственно.Таким образом, на выходе устройства Формируется предсказанное значение отсчета по следующему правилу: щ 1 п1 у 1-1 41.1 11 вт.пфФ ф х 1 4т 1 Пары отсчетов, из которых составлены модули разности для сумм Ут, У, У 3 и У, показаны на Фиг. 2 б, в, г и д соответственно. Предсказываемый отсчет показан черным кружком, а отсчеты, средний иэ которых используется в качестве предсказанного значения, отмечены крестиками.5 1653Устройство может быть реализовано как для случая аналогового предсказания, когда входной и выходной сигналы являются аналоговыми так и дляЭ 5 случая цифрового предсказания, когда входной и выходной сигналы представ-ляют собой двоичные цифровые парал- г лельные коды.10Формула изобретения 1Устройство формирования сигнала отсчета для дифференциального кодера иэображений, содержащее первый блок задержки, вход которого является входом для восстановленного значения цифрового отсчета. текущего элемента изображения, последовательно соединенные второй, третий, четвертый и 20 пятый блоки задержки, последовательно соединенные шестой, седьмой и восьмой блоки задержки, двенадцать блоков вычисления модуля разности сигналов, первый, второй, третий и 25 четвертый сумматоры, выходы которых соединены соответственно с первым; вторым, третьим и четвертым входами блока сравнения, первый, второй, третий и четвертый выходы которого сое динены соответственно с управляющими входами первого, второго, третьего и четвертого ключевых элементов, выходы которых объединены и являются выходом сформированного значения сигнала текущего отсчета, при35 этом выход первого блока задержки соединен с объединенными первыми входами четвертого, седьмого и десятого бло ков вычисления модуля разности сигна лов, выход второго блока задержки соединен с объединенными первыми входами первого, восьмого и одиннадцатого блоков вычисления модуля разности сигналов, выход третьего блока задержки соединен с объединенными вторыми входами первого и четвертого блоков вычисления модуля разности сигналов и с объединенными первыми входами второго, пятого и двенадцатого блоков вычисления модуля разности сигналов, выход четвертого. блока задержки соединен с объединенными вторыми входами второго и седьмого блоков вычисления модуля разности сигналов и с объединенны 55 ми первыми входами третьего, шестого и девятого блоков вычисления модуля разности сигналов, выход пятого блока задержки соединен с объединенными вторьпп входами третьего и десятого блоков вычисления модуля разности сигна лов, выход шестого блока задержки соединен с объединенными вторыми входами пятого и восьмого блоков вычисления модуля разности сигналов, выход седьмого блока задержки соединен с объединенными вторыми входами шестого и одиннадцатого блоков вычисления модуля разности сигналов, выход восьмого блока задержки соединен с вторыми входами девятого и двенадцатого блоков вычисления модуля разности сигналов, выходы первого, второго и третьего блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами первого сумматора, выходы четвертогоУ пятого и шестого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами второго сумматора, выходы седьмого, восьмого и девятого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами третьего сумматора, а выходы десятого, одиннадцатого и двенадцатого блоков вычисления модуля разности сигналов соединены соответственно с первым, вторым и третьим входами четвертого сумматора, о т л и ч а - ю щ е е с я тем, что,. с целью повышения помехоустойчивости, введены последовательно соединенные девятый и десятый блоки задержки, одиннадцатый блок задержки, последовательно соединенные двенадцатый, тринадцатый, четырнадцатый и пятнадцатый блоки задержки, а также первый, второй, третий и четвертый блоки вы" числения среднего значения, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого ключевых элементов, первые входы первого, второго, третьего и четвертого блоков вычисления среднего значения соединены соответственно с выходами первого, вторбго, третьего и четвертого блоков задержки, вторые входы первого, второго, третьего и;четвертого блоков вычисления среднего значения соединены соответственно с выходами девятого, одиннадцатого, седьмогои двенадцатого блоков задержки, третьи входы первого, второго, третьего и четвертого блоков вычисления среднего зна 1653178чения соединены соответственно с выходами десятого, тринадцатого, четырнадцатого и пятнадцатого блоков задержки, при этом выходы первого, десятого, пятого, одиннадцатого и восьмого блоков задержки соединены соответственно с входами девятого, вто-" рого, одиннадцатого, шестого и двенадцатого блоков задержки, 102 Устройство по п.1 о т л ич а ю щ е е с я тем, что первый, второй, третий и четвертый блоки вычис ления среднего значения содержат блок сравнения, первый, второй и третий входы которого соединены соответственна с. информационными входами первого, второго и третьего ключевых элементов и являются соответственнопервым, вторым и третьим входами блока вычисления среднего значения, выходом которого являются обьединенные выходы первого, второго и третьего ключевых элементов, управляющие входы которых соединены соответственно с первым, вторым и третьим выходами блока сравнення.Текущи стра О 0 0 0 0 0 0 1 б 0 0 аг. оставитель В.ЗемлянехредЛ.Олийнык Корректор Н.Корол едактор И.Сегля енно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1 оизводс Заказ 1781 Тираж 40 ВНИИПИ Государственного комите 113035, Иосква0 1 2 3 4 0 ф 1 г З 4 0 1 2 Э 71 2 7 21 4 4 Подписноеизобретениям и открытиям при ГКНТ СССР5, Раущская наб., д, 4/5

СмотретьЗаявка

4693816, 18.05.1989

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

КОПЫЛОВ ДМИТРИЙ АНДРЕЕВИЧ, РАЙХЕЛЬСОН МИХАИЛ КУСЕВИЧ

МПК / Метки

МПК: H04N 7/137

Метки: дифференциального, изображений, кодера, отсчета, сигнала, формирования

Опубликовано: 30.05.1991

Код ссылки

<a href="https://patents.su/5-1653178-ustrojjstvo-formirovaniya-signala-otscheta-dlya-differencialnogo-kodera-izobrazhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство формирования сигнала отсчета для дифференциального кодера изображений</a>