Калибратор фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

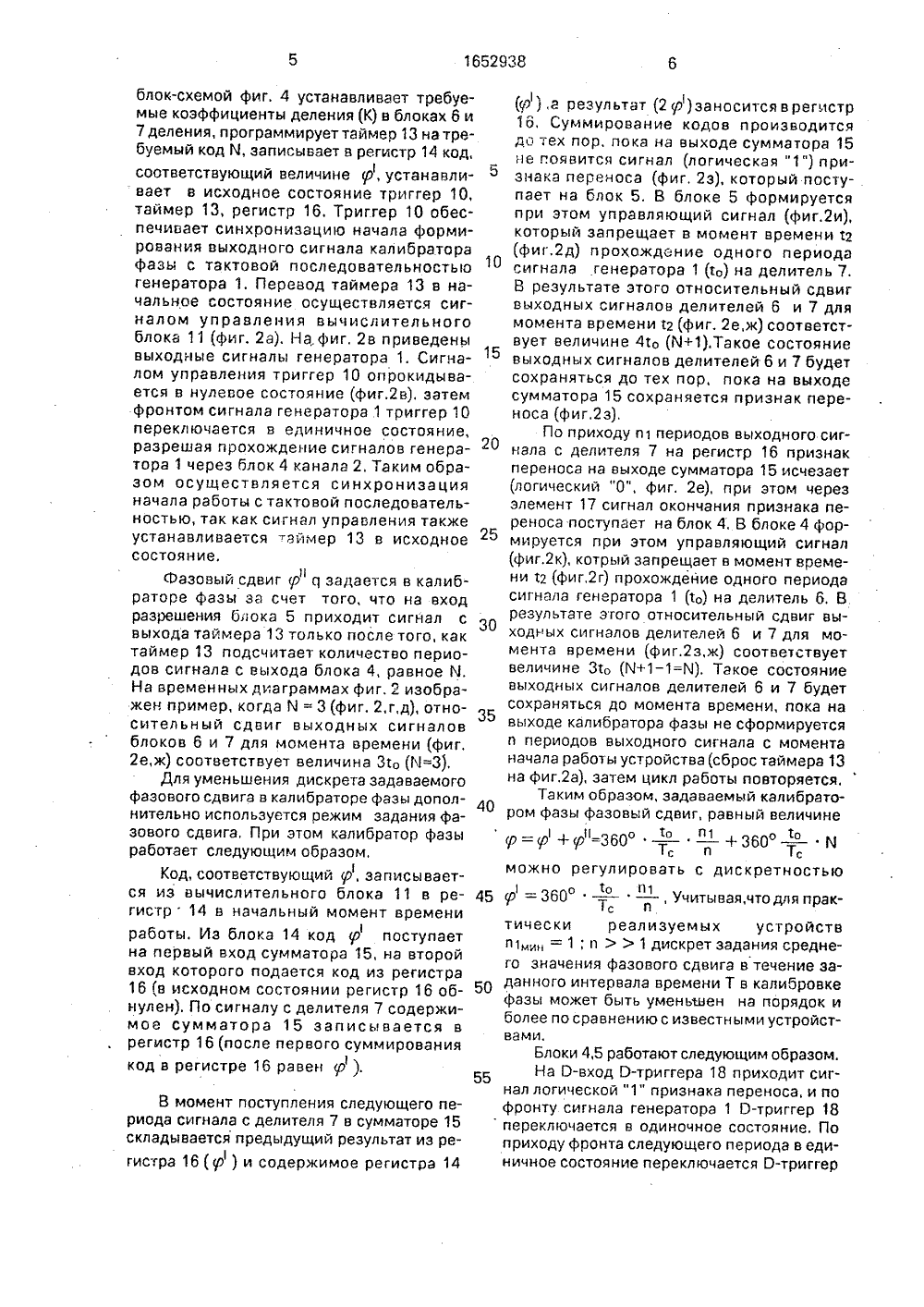

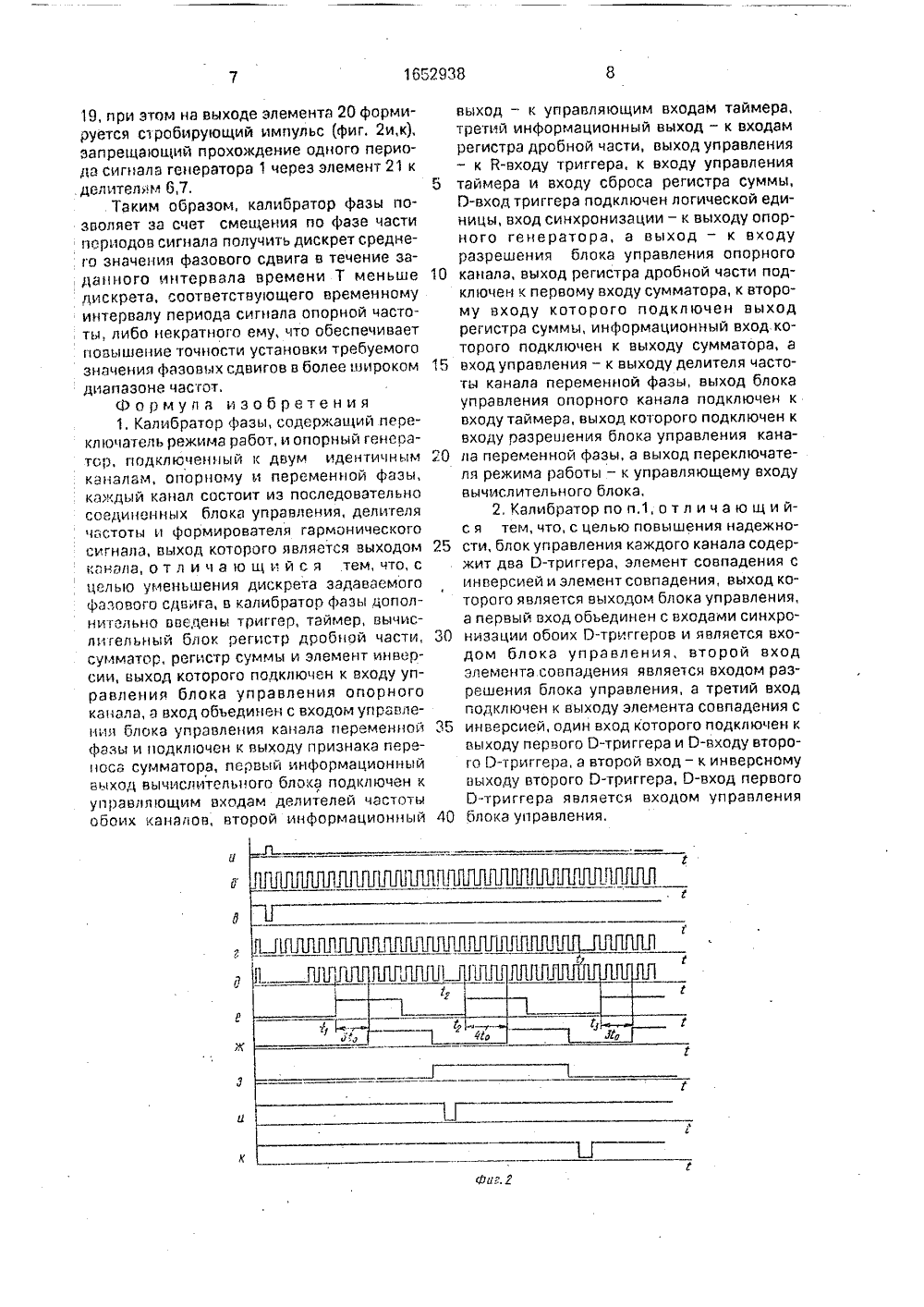

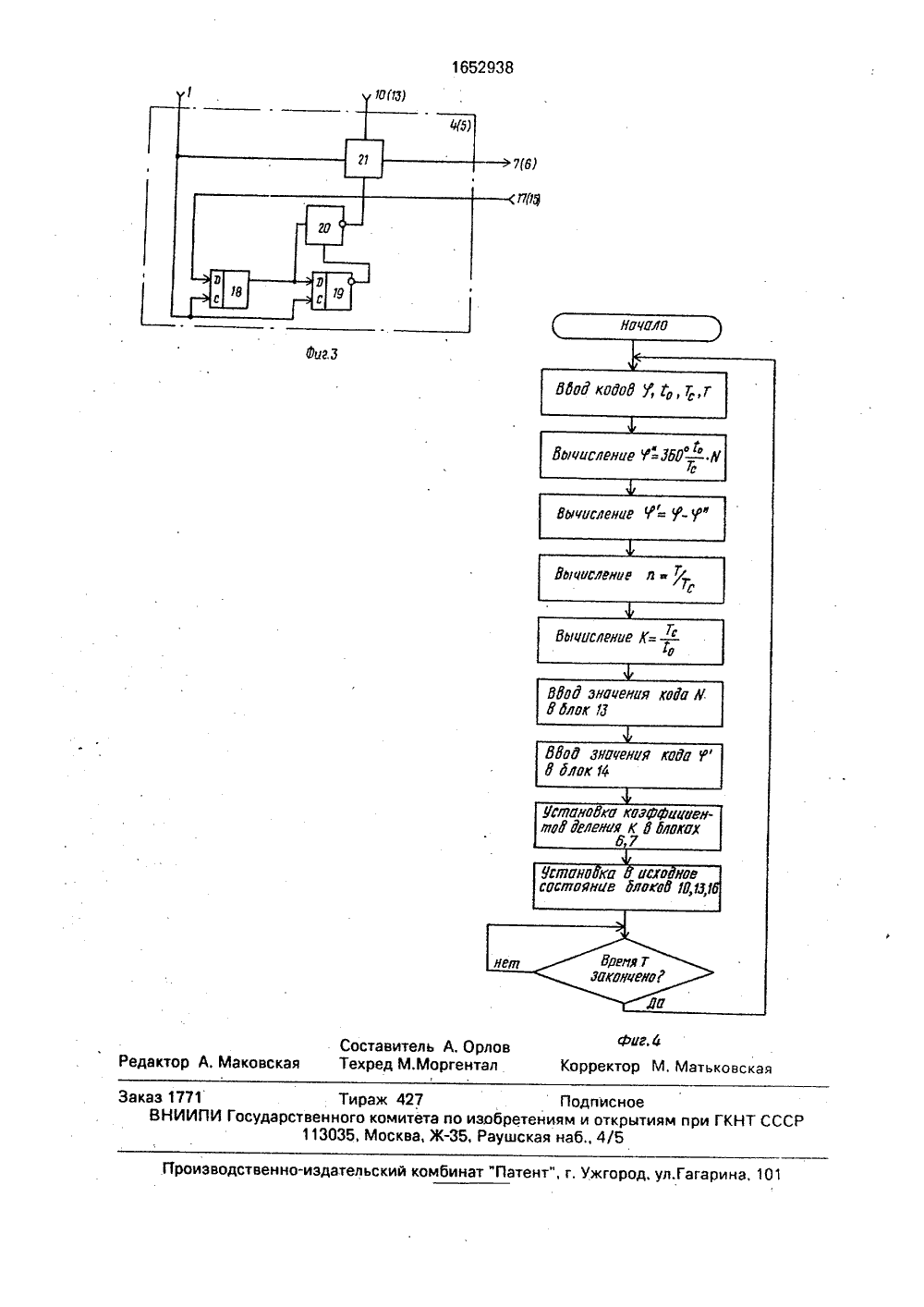

(51) 5 6 01 Я 25/ ИСАНИЕ ИЗОБРЕТЕНИ ное обье и Красн нение ск, С.В,Ч аучное приборо исследований1 - 213. ери- эовагов с е ча- дисига,иГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Изобретение относится к фазоизм тельной технике и может быть исполь но для воспроизведения фазовых сдви малым дискретом в широком диапазон стот. Цель изобретения - уменьшение крета задаваемого фазового сдв Калибратор содержит опорный генерат опорный канал 2, состоящий из блока равления, делителя 6 частоты и формирователя 8 гармонического сигнала, канал 3 переменной фазы, состоящий из блока 5 управления, делителя 7 частоты и формирователя 9 гармонического сигнала, и переключатель 12 режима работ. Введение в калибратор триггера 10, вычислительного блока 11, таймера 13, регистра 14 дробной части, сумматора 15, регистра 16 суммы и элемента 17 инверсии, а также выполнение блоков 4 и 5 в виде триггеров, элемента совпадения с инверсией и элемента совпадения позволяет за счет смещения по фазе части периодов сигнала получить дискрет среднего значения фазового сдвига в течение заданного интервала времени Т меньше дискрета, соответствующего временному интервалу периода сигнала опорной частоты, либо некратного ему, что обеспечивает повышение точности установки требуемого. значения фазовых сдвигов в более широком . " диапазоне частот. 1 з,п,ф-лы, 4 ил.Изобретение относится к фазоиэмерительной технике и может быть использовано для воспроизведения фазовых сдвигов с малым дискретом в широком диапазоне частот.Цель изобретения - уменьшение диск- рета задаваемого фазового сдвига.На фиг. 1 приведена структурная схема калибратора фазы; на фиг. 2 - эпюры, поясняющие принцип работы калибратора фазы; на фиг. 3 - схема блоков управления; на фиг. 4 - блок-схема алгоритма работы вычислительного блока. Калибратор фазы (фиг.1) содержит опорный генератор 1, подключенный к двум идентичным каналам - опорному каналу 2 и каналу 3 переменной фазы, в составе каналов 2 и 3 имеются блоки 4 и 5 управления, делители 6 и 7 частоты и формирователи 8 и 9 гармонического сигнала, причем в канале 2 соединенц последовательно блок 4, делитель 6 и формирователь 8, а в канале 3 - . блок 5, делитель 7 и формирователь 9, а также триггер 10 пуска, вход синхронизации которого подключен к выходу опорного генератора 1, О-вход - к потенциалу логической единицы, а. выход триггера 10 подключен к входу разрешения блока канала 2; вычислительный блок 11, выход управления которого подклочен к В-входу триггера 10, первый информационный выход вычислительного блока 11 подключен к управляющим входам делителей 6,7, вход управления -к выходу переключателя 12 режима работ; таймер 13, к входууправления которого. подключен выход вычислительного блока 11, а к информационному входу - второй информационный выход вычислительного блока 11, к счетному входу таймера 13 подключен выход блока 4, а выход таймера.13 подключен к входу разрешения блока 5; регистр 14 дробной части, вход которого подключен к третьему информационному выходу вычислительного блока 11; сумматор 15, к первому входу которого подключен выход регистра 14, а выход признака переноса подключен к входу управления блошка 5; регистр 16 суммы, информационный вход которого подключен к информационному выходу сумматора 15, информационный выход - к второму информационному входу сумматора 15, к входу сброса регистра 16 подкловен выход управления вычислительного блока 11, а к входу управления записью - выход де, лителей 7, и элемент 17 инверсии, вход которого подключен к выходу признака переноса сумматора 15, а выход - к входу управления блока 4, 1020 25ЗО Блоки 4, 5 (фиг,З) содержат два Р-триггера 18, 19, элемент 20 совпадения с инверсией и элемент 21 совпадения, выходкоторого является выходом блока 4 (5), первый вход элемента 21 соединен с синхровходами 0-триггеров 18, 19 и являетсявходом блока 4 (5), второй вход элемента 21 является входом разрешения блока 4 (5), третий вход соединен с выходом элемента 20, один выход которого соединен с инверсным выходом О-триггера 19, а другой - сО-входом О-триггера 19 и выходом О-триггера 18, Р-вход которого является входом управления блока 4(5)Калибратор фазы работает следующим образом.Генератор 1 вырабатывает сигнал прямоугольной формы, поступающий на блоки 4 и 5, которые осуществляют исключениенеобходимого количества импульсов, после чего в делителях. 6 и 7 производится деление частоты сигналов генератора 1, Далее сигналы прямоугольной формы поступают на формирователи 8 и 9, где производится выделение первой гармоники и формированиевыходного синусоидального сигнала. В ы числ ител ьн ый блок 11 осуществляет управление блоками калибратора фазы и выполняет вычислительные операции с целью задания требуемого фазового сдвига в соответствии с алгоритмом, приведенным на фиг,4,Задаваемый устройство фазовый сдвиг р можно представить в виде формулыр= р +р, Фазовый сдвиг р соответствует задержке по времени целого числа периодов сигнала генератора 1 (с 0), определяется выражением рв = 360 М где Тс - пео 1 ориод выходного сигнала калибратора фазы, ч - код таймера 13 и может принимать значение й = О, 1, 2до (Т/Ь - 1); фазовый сдвиг р представляет собой среднее значение фазового сдвига эа несколько периодов выходного сигнала калибратора фазы и определяется выражениемТс и50где и - количество периодов выходного сигнала калибратора фазы Тс, в течение которых задается среднее значение фазового сдвига р (Тс = Т ) и - количество периодов выходного сигнала калибратора фазы, в течение которых задается фазовый сдвиг р.Перед началом работы калибратора фазы переключателем 12 в вычислительный блок 11 вводятся коды значений рТ 0, Т.Вычислительный блок 11 в соответствии сблок-схемой фиг. 4 устанавливает требуемые коэффициенты деления (К) в блоках 6 и 7 деления, программирует таймер 13 на требуемый код й, записывает в регистр 14 код, соответствующий величине р, устанавливает в исходное состояние триггер 10, таймер 13, регистр 16. Триггер 10 обеспечивает синхронизацию начала формирования выходного сигнала калибратора фазы с тактовой последовательностью генератора 1, Перевод таймера 13 в начальное состояние осуществляется сигналом управления вычислительного блока 11 (фиг, 2 а). На,фиг. 2 в приведены выходные сигналы генератора 1. Сигналом управления триггер 10 опрокидывается в нулевое состояние (фиг.2 в). затем фронтом сигнала генератора 1 триггер 10 переключается в единичное состояние, разрешая прохождение сигналов генератора 1 через блок 4 канала 2, Таким образом осуществляется синхронизация начала работы с тактовой последовательностью, так как сигнал управления также устанавливается таймер 13 в исходное состояние.Фазовый сдвиг р ц задается в калибраторе фазы за счет того, что на вход разрешения блока 5 приходит сигнал с выхода таймера 13 только после того, как таймер 13 подсчитает количество периодов сигнала с выхода блока 4, равное К. На временных диаграммах фиг. 2 изображен пример, когда М = 3 (фиг. 2,г,д), относительный сдвиг выходных сигналов блоков 6 и 7 для момента времени (фиг, 2 е,ж) соответствует величина 31 о (И=35,Для уменьшения дискрета задаваемого фазового сдвига в калибраторе фазы дополнительно используется оежим задания фазового сдвига, При этом калибратор фазы работает следующим образом,Код, соответствующий р, записывается из вычислительного блока 11 в регистр 14 в начальный момент времени работы. Из блока 14 код р поступаетна первый вход сумматора 15, на второй вход которого подается код из регистра 16 (в исходном состоянии регистр 16 обнулен). По сигналу с делителя 7 содержимое сумматора 15 записывается в регистр 16 (после первого суммирования код в регистре 16 равен р). В момент поступления следующего периода сигнала с делителя 7 в сумматоре 15 складывается предыдущий результат из регистра 16 ( р ) и содержимое регистра 14(у ),а результат (2 р ) заносится в регистр1 б, Суммирование кодов производитсядо тех пор, пока на выходе сумматора 15не г.оявится сигнал (логическая "1") признака переноса (фиг. 2 з), который поступает на блок 5. В блоке 5 формируетсяпри этом управляющий сигнал (фиг.2 и),который запрещает в момент времени 12(фиг.2 д) прохождение одного периодасигнала генератора 1 (то) на делитель 7.В результате этого относительный сдвигвыходных сигналов делителей 6 и 7 длямомента времени 12 (фиг. 2 е,ж) соответствует величине 4 со (И+1).Такое состояниевыходных сигналов делителей 6 и 7 будетсохраняться до тех пор, пока на выходесумматора 15 сохраняется признак переноса (фиг.2 з),По приходу п 1 периодов выходного сигнала с делителя 7 на регистр 16 признакпереноса на выходе сумматора 15 исчезает(логический "0", фиг. 2 е), при этом черезэлемент 17 сигнал окончания признака переноса поступает на блок 4, В блоке 4 формируется при этом управляющий сигнал(фиг.2 к), котрый запрещает в момент времени т 2 (фиг,2 г) прохождение одного периодасигнала генератора 1 (то) на делитель 6, Врезультате эгого относительный сдвиг выходных сигналов делителей 6 и 7 для момента времени (фиг.2 з,ж) соответствуетвеличине Зто (И+1-1=К). Такое состояниевыходных сигналов делителей 6 и 7 будетсохраняться до момента времени, пока навыходе калибратора фазы не сформируетсяп периодов выходного сигнала с моментаначала работы устройства (сброс таймера 13на фиг,2 а), затем цикл работы повторяется.Таким образом, задаваемый калибратором фазы фазовый сдвиг, равный величине+=360 о о п 1 + 360 о 1 оТ, п Тсможно регулировать с дискретностью45 р =360 - , Учитывая,чтодля прак о, то, П 1То итически реализуемых устройствп 1;= 1; и ) ) 1 дискрет задания среднего значения фазового сдвига в течение за 50 данного интервала времени Т в калибровкефазы может быть уменьшен на порядок иболее по сравнению с известными устройствами.Блоки 4,5 работают следующим образом.На О-вход О-триггера 18 приходит сигнал логической "1" признака переноса, и пофронту сигнала генератора 1 О-триггер 18переключается в одиночное состояние. Поприходу фронта следующего периода в единичное состояние переключается О-триггер1652938 ЬШЛЛЛПЛЛПЛПЛПШ 13 ЛЛПЛШПВБЛЛШЯБШЯ аппйй Ю.ЛЛ 19, при этом на выходе элемента 20 формируется стробирующий импульс фиг. 2 и,к), запрещающий прохождение одного периода сигнала генератора 1 через элемент 21 к делителям 6,7.Таким образом, калибратор фазы позволяет за счет смещения по фазе части периодов сигнала получить дискрет среднего значения фазового сдвига в течение заданного интервала времени Т меньше дискрета, соответствующего временному интервалу периода сигнала опорной частоты, либо некратного ему, что обеспечивает повышение точности установки требуемого значения фазовых сдвигов в более широком диапазоне частот.Формула изобретения 1. Калибратор фазы, содержащий переключательь режима работ, и опорный генератор, подключенный к двум идентичным каналам, опорному и переменной фазы, каждый канал состоит из последовательно соединенных блока управления, делителя частоты и формирователя гармонического сигнала, выход которого является выходом канала, о т л и ч а 1 о щ и й с я тем, что, с целью уменьшения дискрета задаваемого фазового сдвига, в калибратор фазы дополнительно введены триггер, таймер, вычислигельный блок регистр дробной части, сумматор, регистр суммы и элемент инверсии, выход которого подключен к входу управления блока управления опорного канала, а вход обьединен с входом управления блока управления канала переменной фазы и подключен к выходу признака переноса сумматора, первый информационный выход вычислительного блока подключен к управляющим входам делителей частоты обоих каналов, второй информационный выход - к управляющим входам таймера, третий информационный выход - к входам регистра дробной части, выход управления - к Я-входу триггера, к входу управления 5 таймера и входу сброса регистра суммы,О-вход триггера подключен логической единицы, вход синхронизации - к вь 1 ходу опорного генератора, а выход - к входу разрешения блока управления опорного 10 канала, выход регистра дробной части подключен к первому входу сумматора, к второму входу которого подключен выход регистра суммы, информационный вход которого подключен к выходу сумматора, а 15 вход управления - к выходу делителя частоты канала переменной фазы, выход блока управления опорного канала подключен к входу таймера, выход которого подключен к входу разрешения блока управления кана ла переменной фазы. а выход переключателя режима работы - к управляющему входу вычислительного блока.2, Калибратор по п.1, отл ича ю щи йс я тем, что, с целью повышения надежно сти, блок управления каждого канала содержит два О-триггера, элемент совпадения с инверсией и элемент совпадения, выход которого является выходом блока управления, а первый вход объединен с входами синхро низзции обоих О-триггеров и является входом блока управления, второй вход элемента совпадения является входом разрешения блока управления, а третий вход подключен к выходу элемента совпадения с 35 инверсией, один вход которого подключен квыходу первого О-триггера и О-входу второго О-триггера, а второй вход - к инверсному выходу второго О-триггера, О-вход первого О-триггера является входом управления 40 блока управления,. Матьковска Составитель А. ОрловРедактор А. Маковская Техред М.Моргентал ррек 101 оиэводственно-издательский комбинат "Патент", г. Ужгород, ул.Гага аказ 1771 Тираж 427 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4484392, 19.09.1988

НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "СИБЦВЕТМЕТАВТОМАТИКА", КРАСНОЯРСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОКОРИН ВЛАДИМИР ИВАНОВИЧ, КУЧКО ВИКТОР АЛЕКСАНДРОВИЧ, ЧЕПУРНЫХ СЕРГЕЙ ВИКТОРОВИЧ, ЧМЫХ МИХАИЛ КИРИЛЛОВИЧ

МПК / Метки

МПК: G01R 25/04

Метки: калибратор, фазы

Опубликовано: 30.05.1991

Код ссылки

<a href="https://patents.su/5-1652938-kalibrator-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Калибратор фазы</a>