Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

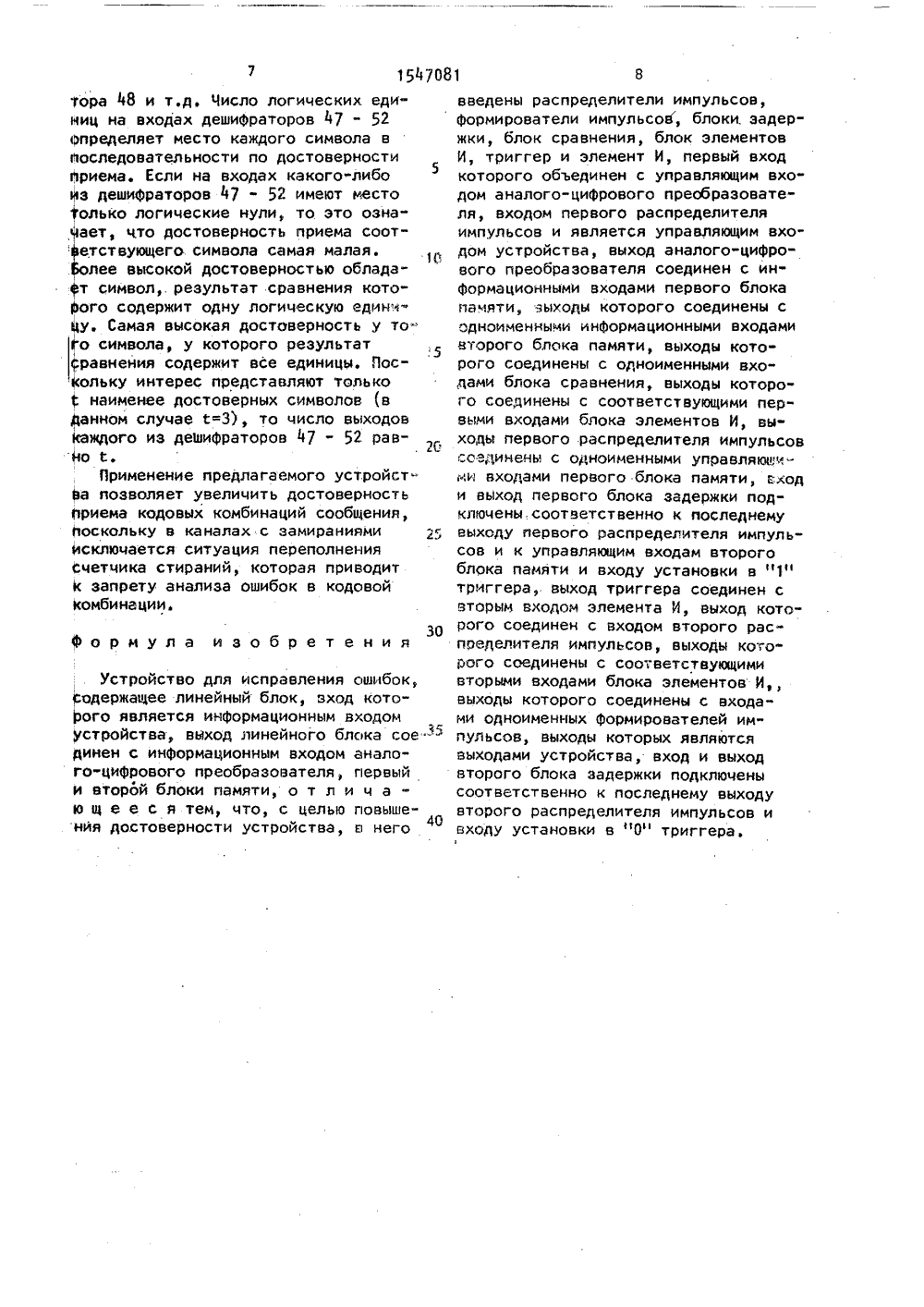

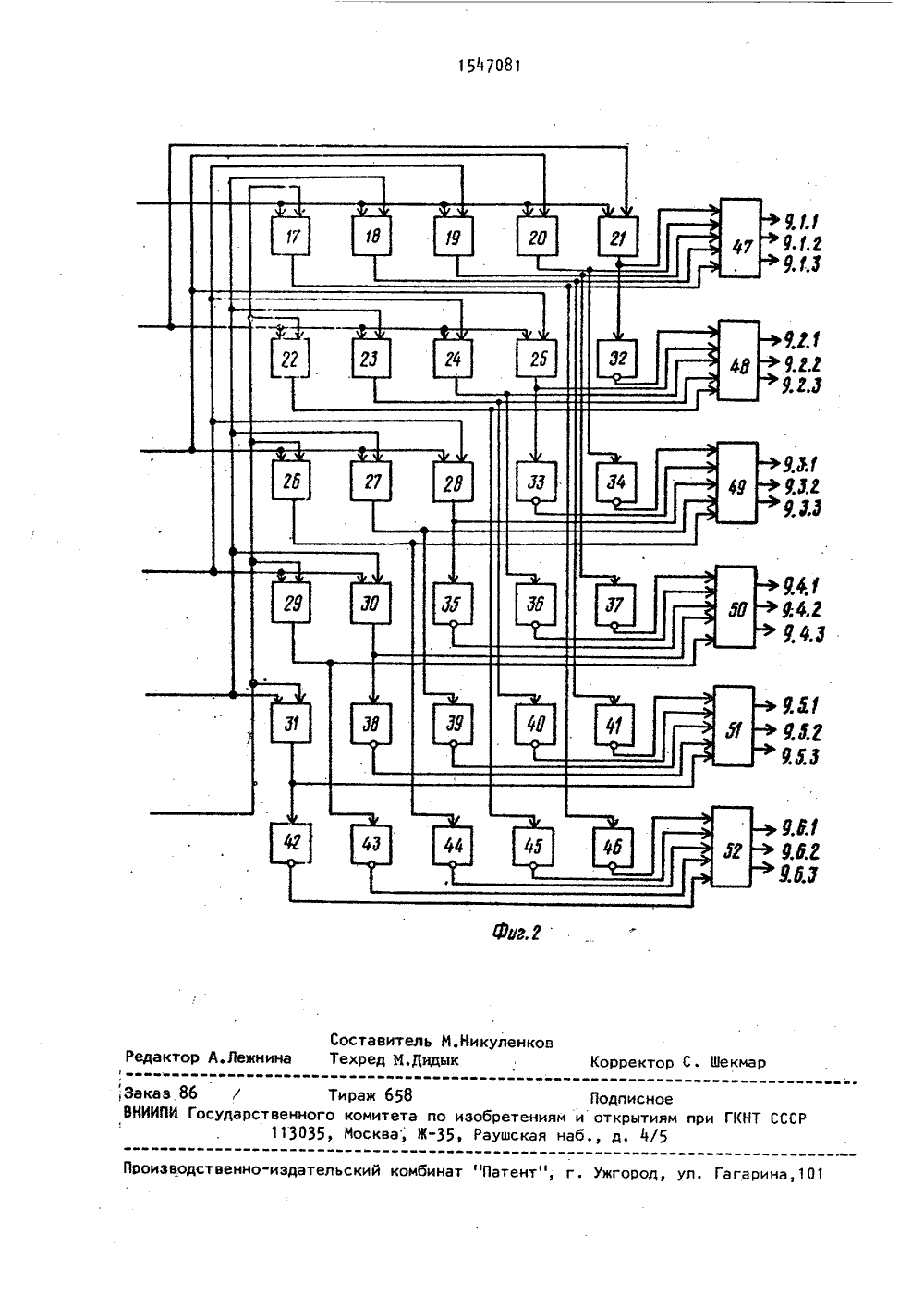

(51) 5 Н 13 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОП 1 РЫТИЯМПРИ ГКНТ СССР ИЗОБРЕТВИДЕТЕЛЬСТВУ(71) Воронежский политехнический институт(56) Авторское свидетельство СССРР 1115086, кл. С 08 С 19/28, 1982.Авторское свидетельство СССРН 976466, кл. С 08 С 19/28, 1981.(54) УстРойство для испРАвлкния оаиБОК(57) Изобретение относится к электН.Емельчев ОПИСАНИ К АВТОРСКОМУ росвязи и может использоваться в системах передачи цифровой информации.Устройство осуществляет выделениеимпульсов принимаемой кодовой комбинации с наименьшей амплитудой (наименее достоверных) для их последующего декодирования, что повышаетдостоверность устройства. Устройствосодержит линейный блок 1, аналогоцифровой преобразователь 2, распределители 3, 12 импульсов, блоки 4, 5памяти, регистры памяти 6. 1 - 6.п и7. 1 - 7.п, блоки 8, 16 задержки,блок 9 сравнения, триггер 10, элеменИ 11 и блок 13 элементов И 14. 2 ил,подаются тактовые импульсы. Тактовыйимпульс, формирующий первый символкодовой комбинации сообщения, поступает на первый выход распределителя3 импульсов. Задний Фронт импульсана первом выходе распределителя 3позволяет записать информацию с выхода преобразователя 2 в регистр 6.1.Тактовый импульс, формирующий второйсимвол комбинации, передним фронтомвоздействует на преобразователь 2,что позволяет на его выходе зафиксировать уровень сигнала, соответствующий моменту действия переднего фронтатактового импульса, а задний фронтвторого тактового импульса, поступившего на второй выход распределителя3, осуществляет запись этой информации в регистр 6,2, Тактовый импульс,Формирующий последний символ комбинации, запишет информацию об уровнепоследнего символа в регистр б.п.Тактовый импульс последнего символаявляется управляющим импульсом записи информации в регистры 7.1 - 7.п.Этот импульс с последнего выхода распределителя 3 задерживается в блоке8 на время, большее длительности тактового импульса, но меньшее периодаследования тактовых импульсов, чтопозволяет переписать информацию изрегистров 6 в регистры 7 до появления тактового импульса, Формирующего первый символ последующей кодовой комбинации сообщения.Значения уровней напряжения символов комбинации, записанные в регистрах 7, поступают на входы блоха 9сравнения, в котором значения уровней сравниваются попарно между собой. На выходах 9.1.1 - 9.1.с формируется информация об относительномзначении уровня, хранящегося в регистре 7.1, на выходах 9.2.1 - 9.2.синформация о значении уровня, хранящегося в регистре 7.2, и т.д. Появление логической единицы на одном иэвыходов 6.1.1, 6.2. 1, , б.п. указывает на самое малое значение уров О ня символа, хранящегося в соответствующем регистре. Сигнал логическойединицы на одном иэ выходов 9. 1,2,9,2.2, , 9.п.2 указывает на второепо малости значение уровня символа, 55 а сигнал логической единицы на выходах 9.1., 9.2.й.9.п.й - нве-е по малости знацение уровня. Так,если имеют место сигналы логической 3 15 ч 7081Изобретение относится к электросвязи и может быть использовано в системах передачи цифровой информации.Целью изобретения является повышение достоверности устройства.На Фиг.1 изображена функциональ" ная схема предлагаемого устройства; на фиг2 - Функциональная схема бло;ка сравнения.Устройство содержит (Фиг,1) линейный блок 1, аналого-циФровой преобразователь 2, первый распределитель 3 импульсов, первый и второй блоки 4 и 5 Памяти, выполненные на регйстрах 6 и 7 памяти, первый блок 8 задержки, блок 9 сравнения, триггер 10, элемент И 11, второй распределитель 12 импульсов, блок (матри ца) 13 элементов И 11, Формирователи 15 импульсов и второй блок 16 задержки.Блок сравнения содержит (Фиг.2) элементы 17 - 31 сравнения (выделения большего числа), элементы НЕ 32- йб дешифраторы 17 - 52.Устройство работает следующим образом.На информационный вход устройства поступает аналоговое напряжение с выхода приемника двоичных сигналов, ,а на управляющий вход устройства по" даются импульсы управления с выхода ,генератора тактовых импульсов первой решающей схемы приемника двоичных сигналов.Аналоговое напряжение поступает на вход блока 1, в котором биполяр" ное напряжение преобразуется в однополярное, после чего с выхода блока 1 попадает на информационный вход преобразователя 2, к управляющему входу которого подключен выход тактового генератора приемника двоичных сигналов. Передний фронт тактового импульса, Формирующего очередной символ кодовой комбинации, воздействуя на управляющий вход преобразователя 2, преобразует аналоговое нап" ряжение в цифровую Форму. Кодовая комбинация соответствующего уровня аналогового сигнала поступает на информационные входы регистров 6, цисло которых равно числу символов кодовой комбинации сообщения, На уп" равляющие входы регистров 6 поступают импульсы с выходов первого распределителя 3 импульсов, на вход которого1547081 единицы на выходах 9.1.2, 9.2,9.п.1, это означает, что в регистре 7.п хранится самое малое значение уровня, а в регистре 7.2 - -епо малости значение уровня.Исходя из положения, цто вероятность регистрации искаженного символа тем больше, чем меньше абсолютноезначение уровня напряжения на выходеприемника двоичных сигналов, выбраналгоритм приоритетного анализа сим"волов в блоке .Формирования полиномаошибок (БФПО) путем анализа символовкодовой комбинации, уровни которыхнаиболее близки к нулевому. Так, еуказанном выше примере в первую строку матрицы памяти ЬФПО должет бытьпомещен последний символ кодовойкомбинации, во вторую строку - первый символ, а в й-ю строку - второйсимвол, цля записи в матрицу памятиБФПО информации в указанной последовательности необходимо, чтобы управляющие импульсы из Формирователей15 в буферный накопитель поступалие той же самой последовательности.В указанном примере сигналы логической единицы имеют место на входах элементов 14.1,п, 14,2,1,14.с.2. Тактовый импульс с последнего выхода распределителя 3 черезблок 8 задержки опрокидывает триггер10, сигнал логической единицы с прямого выхода которого поступает навход элемента И 11. Тактовые импульсы через элемент И 11 подаются навход распределителя 12 импульсов,первый тактовый импульс появляетсяна первом выходе распределителя 12,а следовательно, и на вторых входахэлементов И 14 первой строки матрицы13. Поскольку в данном случае в первой строке матрицы 13 сигнал логической единицы присутствует только навходе элемента И 14.1.п, то импульсс первого выхода распределителя 12Формирует сигнал логической единицына выходе элемента И 14,1.п, которыйвоздействует на и-й Формирователь15, сигнал с выхода которого указывает, что в матрицу памяти БФПО впервую строку должен быть записани-й символ кодовой комбинации сообщения. Тактовый импульс, формирующийвторой символ последующей кодовойкомбинации, поступает на второй выход распределителя 12 импульсов,цто приводит к появлению сигнала 6логической единицы на выходе одногоиз элементов И 14.2.1 второй. строкиматрицы 3, Этот сигнал воздействует на первый формирователь 1, чтоприводит к записи во вторую строкуматрицы памяти БФПО первого символакодовой комбинации сообщения. Импульснапряжения с -го выхода распределителя 12 импульсов Формирует сигналлогической единицы, обеспечивающийзапись в с-ю строку матрицы памятиБФПО второго символа кодовой комбинации сообщения. Поскольку еп, тозапись информации в матрицу памятиБФПО осуществится раньше, чем за"полнится блок 6 памяти значениямисимволов следующей кодовой комбина"ции. Импульс напряжения с последне"20 го выхода распределителя 12 черезблок 16 задержки поступает на входтриггера 10, опрокидывая его и закрывая элемент И 11. Устройство вновьготово.к анализу следующей кодовойкомбинации.На фиг.2 приведена Функциональнаясхема блока 9 сравнения для случаяп=6 и е=З,Знацения уровней символов кодовойЗО комбинации сообщения, хранящиесяв двоичной форме в регистрах 7.17,6, сравниваются между собой. Дляэтого значения уровней символов попарно поступают на входы элементов17 - 31 выделения большего числа,З 5 Если в таких элементах 17 - 31 напервые (левые) входы подать число, А,а на вторые входы (правые) - числоВ, то на их выходах появится сигналлогической единицы при условии АВ.В противном случае на выходе имеетместо логический ноль. В элементах17 - 21 происходит сравнение значения уровня первого символа комбинации со значениями уровней всех осталь.ных символов. В элементах 22 - 25сравниваются уровни второго символас уровнями третьего и т.д. символов.Результат сравнения уровня второго50символа с первым представляет собой инверсию (элемент НЕ 32) результата сравнения уровня первого символа с вторым в элементе 21. Результаты сравнения уровня первого символа комбинации с уровнями остальных5 символов поступают на входы дешифратора 47, результаты сравнения уров"ня второго символа с уровнями остальных символов - на входы дешифра"ора 48 и т.д, Число логических единиц на входах дешифраторов 47 - 52 Фпределяет место каждого символа в последовательности по достоверности Приема. Бсли на входах какого-либо Мз дешифраторов 47 - 52 имеют место двольно логические нули, то это ознаает, что достоверность приема соот етствующего символа самая малая.лее высокой достоверностью обладат символ,. результат сравнения котоого содержит одну логическую единиу. Самая высокая достоверность у тоо символа, у которого результат равнения содержит все единицы, ПосМольку интерес представляют тольконаименее достоверных символов (в анном случае с=Э), то число выходовждого из дешифраторов 47 - 52. равйо С.Применение предлагаемого устройгта позволяет увеличить достоверность приема кодовых комбинаций сообщения, поскольку в каналах с замираниями Исключается ситуация переполнения счетчика стираний, которая приводит Н запрету анализа ошибок в кодовой Номбинации,30формула изобретения Устройство для исправления ошибок, одержащее линейный блок, вход которого является информационнь 1 м входом устройства, выход линейного блока сое 5 динен с информационным входом анало" го-цифрового преобразователя, первый и второй блоки памяти, о т л и ч аю щ е е с я тем, что, с целью повышения достоверности устройства, в него введены распределители импульсов,Формирователи импульсов, блоки. задержки, блок сравнения, блок элементовИ, триггер и элемент И, первый входкоторого обьединен с управляющим вхо"дом аналого-цифрового преобразователя, входом первого распределителяимпульсов и является управляющим входом устройства, выход аналого-цифрового преобразователя соединен с информационными входами первого блокапамяти, выходы которого соединены содноименными информационными входамивторого бпока памяти, выходы которого соединены с одноименными вхо"дачи блока сравнения, выходы которого соединены с соответствующими первыми входами блока элементов И, выходы первого распределителя импульсовсоединены с одноименными упрввляювими входами первого блока памяти, входи выход первого блока задержки подключены,соответственно к последнемувыходу первого распределителя импульсов и к управляющим входам второгоблока памяти и входу установки в "1"триггера, выход триггера соединен свторым входом элемента И, выход которого соединен с входом второго распределителя импульсов, выходы которого соединены с соответствующимивторыми входами блока элементов Ивыходы которого соединены с входами одноименных Формирователей импульсов, выходы которых являютсявыходами устройства, вход и выходвторого блока задержки подключенысоответственно к последнему выходувторого распределителя импульсов ивходу установки в "0" триггера.1Подписноеизобретениям и открытиям при ГКНТ СССР5, Раушская наб., д. 4/5 оизводственно-издательский комбинат "Патент", г. Ужг л. Гагарина, 10;Заказ 86 Тираж б 58 ВНИИПИ Государственного комитета113035, Москва,%И ЯИ 9 Л.З 911 .г КЫ ИЛ КИ 9.И У.О Ю 8 ИЯ Дф

СмотретьЗаявка

4438640, 08.06.1988

ВОРОНЕЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ВАХТИН ОЛЕГ ГЕОРГИЕВИЧ, ЕМЕЛЬЧЕВ СЕРГЕЙ НИКОЛАЕВИЧ, ЧЕРНЕНКО АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 13/23

Метки: исправления, ошибок

Опубликовано: 28.02.1990

Код ссылки

<a href="https://patents.su/5-1547081-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Устройство для декодирования итеративного кода

Следующий патент: Релейный коммутатор

Случайный патент: Компенсационный датчнк давления грунта