Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

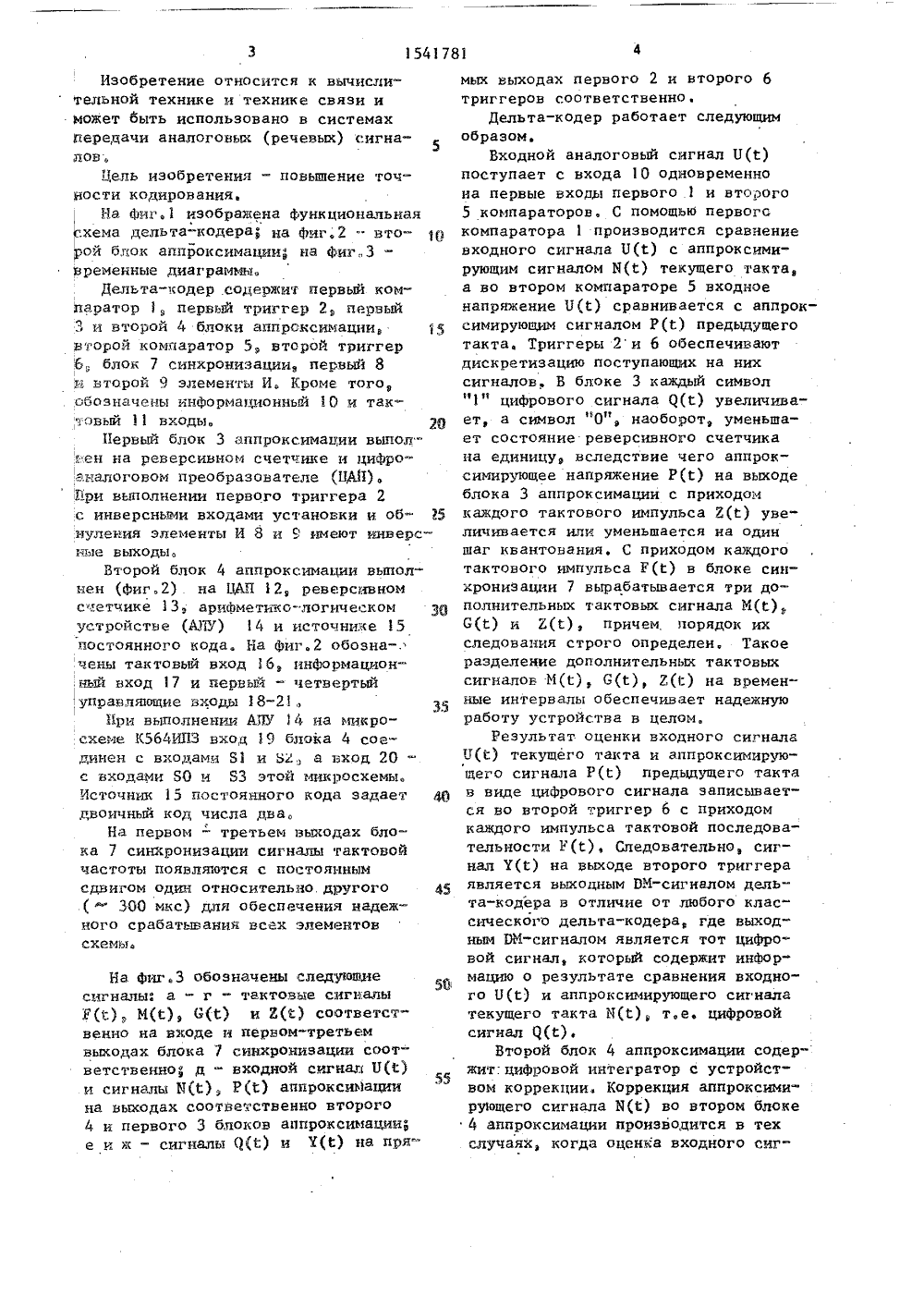

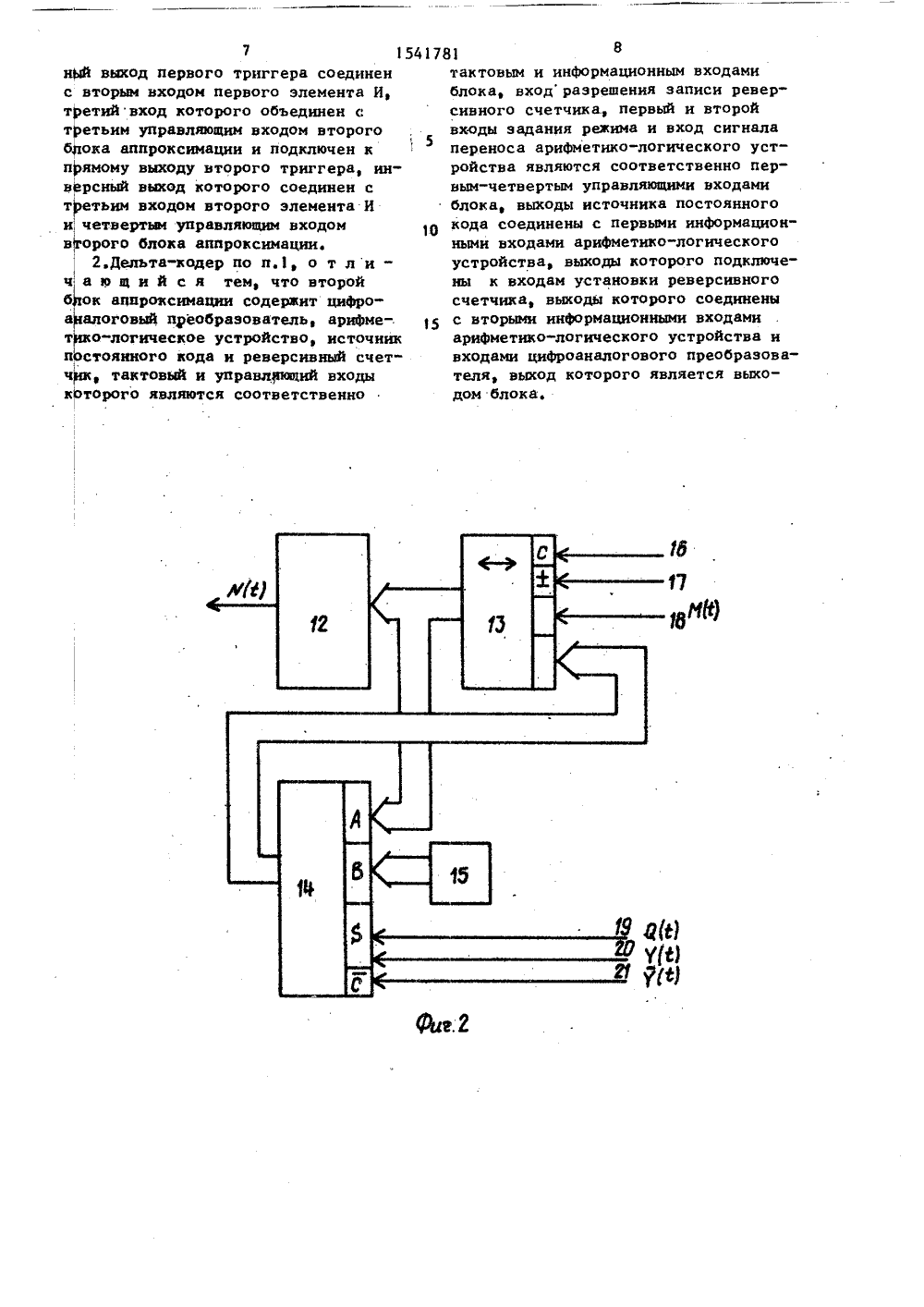

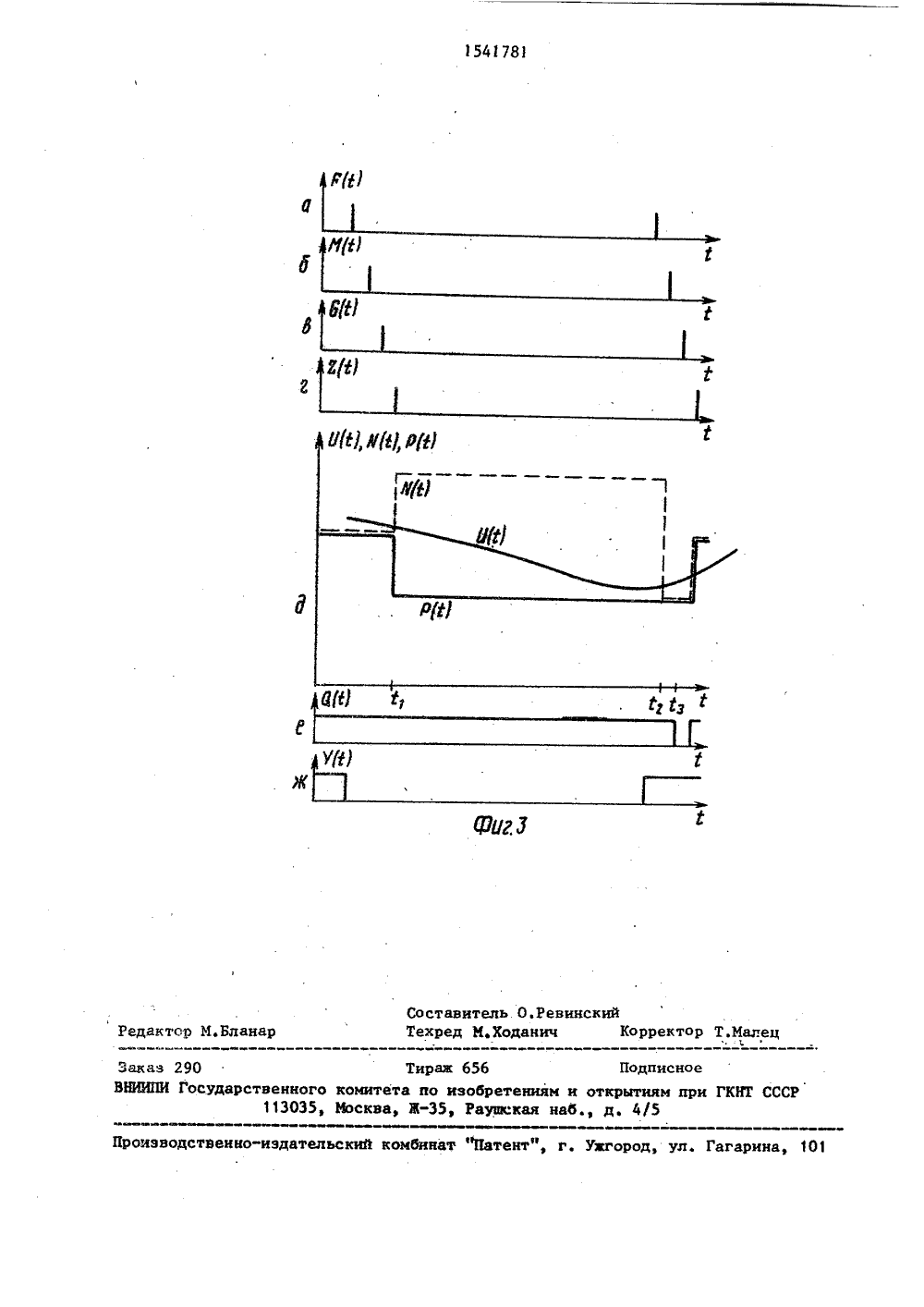

(19 ( А 1)5 Н 03 М 3/02 ГОСУДАРСТВЕННЫЙПО ИЗОБРЕТЕНИЯМ ИПРИ 01 НТ СССР МИТЕТ ОТНРЫТИЯЕНИЯ ПИСАНИЕ ИЗОБРЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(46) 07.02.9 О. Бюл. Я 5 (71) Рижский политехнический инсти тут им. А.Я.Пельше(57) Изобретение относится к вычислительной технике и технике связи.Его использование в системах передачи аналоговых (речевых) сигналовпозволяет повысить точность кодирования, Дельта-кодер содержит компараторы 1, 5, триггеры 2, 6 и блок 3аппроксимации. Благодаря введениюблока 4 аппроксимации, блока 7синхронизации и элементов И 8, 9 вдельта-кодере производится коррекцияаппроксимирующего сигнала в текущемтакте с учетом оценки входного сигнала в том же такте и аппроксимирующего сигнала в предыдущем такте.1 з,п, ф-лы, 3 ип.На Фиг.З обозначены следующие сигналы: а - г - тактовые сигвалы Р(:) М(С), 6(С) и Е(а.) соответственно на входе и первом-третьем выходах блока 7 синхронизации соответственно" д - водной сигнал Б и сигналы Б(С)., Р(С) аппроксимации на выходах соОтВетственно ВторОго ч н первого 3 блоков аппроксимации; е и ж - сигналы Я(С) и У(С) на пря 56 Изобретение относится к вычислительной технике и технике связи и Может быть использовано в системах передачи аналоговых (речевых) сигна 5 лов.Цель изобретения - повышение точности дирования.На фиг.1 изображена функциональная схема дельта-кодерами на фиг.2 - вто О Рой блок аппроксимации; на ФигвЗ - Временные диаграмма.Дельта-кодер .содержит первый компаратор 1, первый триггер 2, первый3 и второй 4 блоки аппроксимации, Второй компаратор 5, второй триггер 6 блок 7 синхронизации, первый 8второй 9 элементы И, Кроме того, обозначены информационный 1 О ч так.Овый 11 входы. 2 ОПервый блок 3 аппроксимации выпол- Г,ен на реВерсивном счетчике и цифрОаналогоВОм преобразователе (ПМЦ айри выполнении первого триггера 2 с инверсными входами установки и об нуления элементы И 8 и с имеют инверсные выходы.Второй блок ч аппроксимации выполнен (Фиг.2) на ЦАП 12, реверсивномс .етчике 13, арифметико"логиче ком ЗО устройстве (ЮЗУ) 1 ч и источнике 15постоянного кода, На Фиг.2 обозна-.чены тактовый вход 16, информационьй вход 17 и первый " четвертый ,управляющие входы 18-21. 35Нри выполнении АПУ ч на микро"схеме К 5 б 4 ИПЗ вход 19 блока 4 соединен с входами Б 1 и Ы, а Вход 2 О -с входами БО и ЯЗ этой микросхемы.Источник 15 постоянного кода задает 4 Одвоичный код числа два.На первом - третьем Выходах блока 7 синхронизации сигналы тактовойчастоты появляются с гостояннымсдвигом одоп относительно. другого 45ЗОО мкс) для обеспечения надежного срабатьвания всех элементовсхемыв мых выходах первого 2 и второго бтриггеров соответственно.Дельта-кодер работает следующимобразом,Входной аналоговый сигнал У(й)поступает с входа 1 О одновременнона первые Входы первого 1 и второго5 компараторов, С помощью первогокомпаратора 1 производится сравнениевходного сигнала 0(й) с аппроксимирующим сигналом И(1) текущего такта,а во втором компараторе 5 входноенапряжение У(С) сравнивается с аппроксимирующим сигналом Р(й) предыдущеготакта, Триггеры 2 и б обеспечиваютдискретизацию поступающих на нихсигналов, В блоке 3 каждый символ"1" цифрового сигнала Я(С) увеличивает, а символ "О", наоборот, уменьшает состояние реверсивного счетчикана единицу, вследствие чего аппроксимирующее напряжение Р на выходеблока 3 аппроксимации с приходомкаждого тактового импульса Е увеличивается или уменьшается на одиншаг квантования. С приходом каждоготактового импульса Р в блоке синхронизации 7 вырабатывается три дополнительных тактовых сигнала М(Е),С и Е(с), причем порядок ихследования строго определен. Такоеразделение дополнительных тактовыхсигналов М(е), С(й), Е(1:) на временные интервалы обеспечивает надежнуюработу устройства в целом,Результат оценки входного сигналаП(1:) текущего такта и аппроксимирующего сигнала Р предыдущего тактаВ виде цифрового сигнала записывается во второй триггер б с приходомкаждого импульса тактовой последовательности Ра Следовательно, сигнал 7(С) на выходе второго триггераявляется выходным ВМ-сигналом дельта-кодера в отличие от любого классического дельта-кодера, где выходным ВМ-сигналом является тот цифровой сигнал, который содержит информацию о результате сравнения входного П(С) и аппроксимирующего сигналатекущего такта 11(С), т.е. цифровойсигнал 11(й)аВторой блок 4 аппроксимации содержит: цифровой интегратор с устройством коррекции. Коррекция аппроксимирующего сигнала И(й) во втором блоке4 аппроксимации произвоцится в техслучаях, когда оценка входного сиг5 154 нала Б(С) и аппроксимирующего сигнала текущего такта И(с) не совпадает с оценкой входного сигнала У(С) и аппроксимирующего сигнала Р(й) преды. дущего такта, т.е. если цифровые сигналы Ц(й) и У(1) не совпадают, то следует производить коррекцию как аппроксимирующего напряжения Я(С)так и сигнала Я(С). В момент времени(фиг.Э) во втором блоке 4 аппроксимации произведена ошибочная аппроксимация Н(С), которая устраняется . в момент времени с . В данном случае ошибка устраняется путем вычитания из значения аппроксимирующего напряжения Ю(й) значения 21, Таким образом, сигнал Я приравнивается сигналу Р(С), Описанная операция коррекции в видеН = К + 23или И(е)Н(й) - 28реализуется с помощью АЛУ 14 во втором блоке 4 аппроксимации следующим образом.В зависимости от значений цифровых сигналов Я, У и 7 во втором блоке 4 аппроксимации производится коррекция сигнала Б(1) в соответствии с табл.). 1781 Таблица 1 я(е) я Н(е)Б(с)+23Н(с) -23ИИЭ О О 1 1 О 1 О 1 Следовательно, коррекция я тактируется цифровым сигналом М, который подается на вход разрешения записи реверсивного счетчика 13,Для коррекции сигнала Я на входы элементов И 8 и 9 подаются прямые и инверсные значения сигналов Ц(Е) и У(й) так, чтобы сформировать сигналы 8 и К установки для первого триггера 2 согласно табл.2. 0 1 О 1 О О 1 1 0 О 1 О О 1 О О Таблица 2Г Т Т0 К 3 20 25 30 35 40 45 50 55 В данном случае используется тактирование с помощью цифрового сигнала С(Т), вследствие чего в каждом такте РМ-сигнала происходит приравнивание сигнала Ц(1) сигналу У.Таким образом, за счет использования оценки входного сигнала текущего такта и аппроксимирующего напряжения предыдущего такта производится коррекция айпроксимации в текущем такте, что в конечном итоге приводит к увеличению отношения сигнал/шум, Формула 1.Дельта-кодер, содержащий первый компаратор, первый вход которого является информационным входом дельта-кодера, а выход соединен с информационным входом первого триггера, первый блок аппроксимации, второй компаратор, выход которого подключен к информационному входу второго триггера, прямой выход которого является выходом дельта-кодера, о т - л и ч а ю щ и й с я тем, что, с целью повышения точности кодирования, в дельта-кодер введены второй блок аппроксимации, элементы И и блок синхронизации, вход которого объединен с тактовым входом второго триггера и является тактовым входом дельта-кодера, первый выход блока синхронизации соединен с тактовыми входами первого триггера и блоков аппроксимации, информационный вход второго блока аппроксимации подключен к выходу первого компаратора, первый вход второго компаратора подключен к информационному входу дельта-кодера, второй выход блока синхронизации соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к установочному входу и входу обнуления первого триггера, третий выход блока синхронизации соединен с первым управляющим входом второго блока аппроксимации, выход которого подключен к второму входу первого компаратора, прямой выход первого триггера соединен с вторым входом второго элемента И, вторым управляющим входом второго блока аппроксимации и информационным входом первого блока аппроксимации, выход которого подключен к второму входу второго компаратора, инверс7 1 науй выход первого триггера соединен с вторым входом первого элемента И, третийвход которого объединен с третьим управляющим входом второго бЛока аппроксимации и подключен к п ямому выходу второго триггера, инв рсный выход которого соединен с т етьим входом второго элемента И и четвертым управляющим входом в орого блока аппроксимации.2,Дельта-кодер по п.1, о т л и - ч а ю щ и й с я тем, что второй б ок аппроксимации содержит цифроа алоговый преобразователь, арифме-. т о-логическое устройство, источник постоянного кода и реверсивный счетчтактовый и управюцпащий входы к, торого являются соответственно 541781втактовым и информационным входамиблока, вход разрешения записи реверсивного счетчика., первый и второйвходы задания режима и вход сигналапереноса арнфметико-логического устройства являются соответственно первым-четвертым управляющими входамиблока, выходы источника постоянногокода соединены с первыми информационными входами арифметико-логическогоустройства, выходы которого подключены к входам установки реверсивногосчетчика, выходы которого соединеныс вторыми информационными входамиарифметико-логнческого устройства ивходами цифроаналогового преобразователя, выход которого является выхоока.1541782 оставитель О.Ревинскийехред И.Ходанич Ко тор Т.Малец ана Тираж б 56 ета по иэобрете а, Ж, Раушск о и и открытия наб., д. 4/5 роиэводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1 Заказ 290ВНИИПИ Государственного комит113035, Иос исноем при ГКНТ ССС

СмотретьЗаявка

4434497, 31.05.1988

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ПУНДУРС АРМАНД АНТОНОВИЧ, ХОФМАРКС ВАЛДИС ВОЛДЕМАРОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/5-1541781-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Преобразователь угол-код

Следующий патент: Устройство для преобразования кодов

Случайный патент: Газовая горелка с защитой от обратного удара