Функциональный цифроаналоговый преобразователь двоично десятичного кода для следящих систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

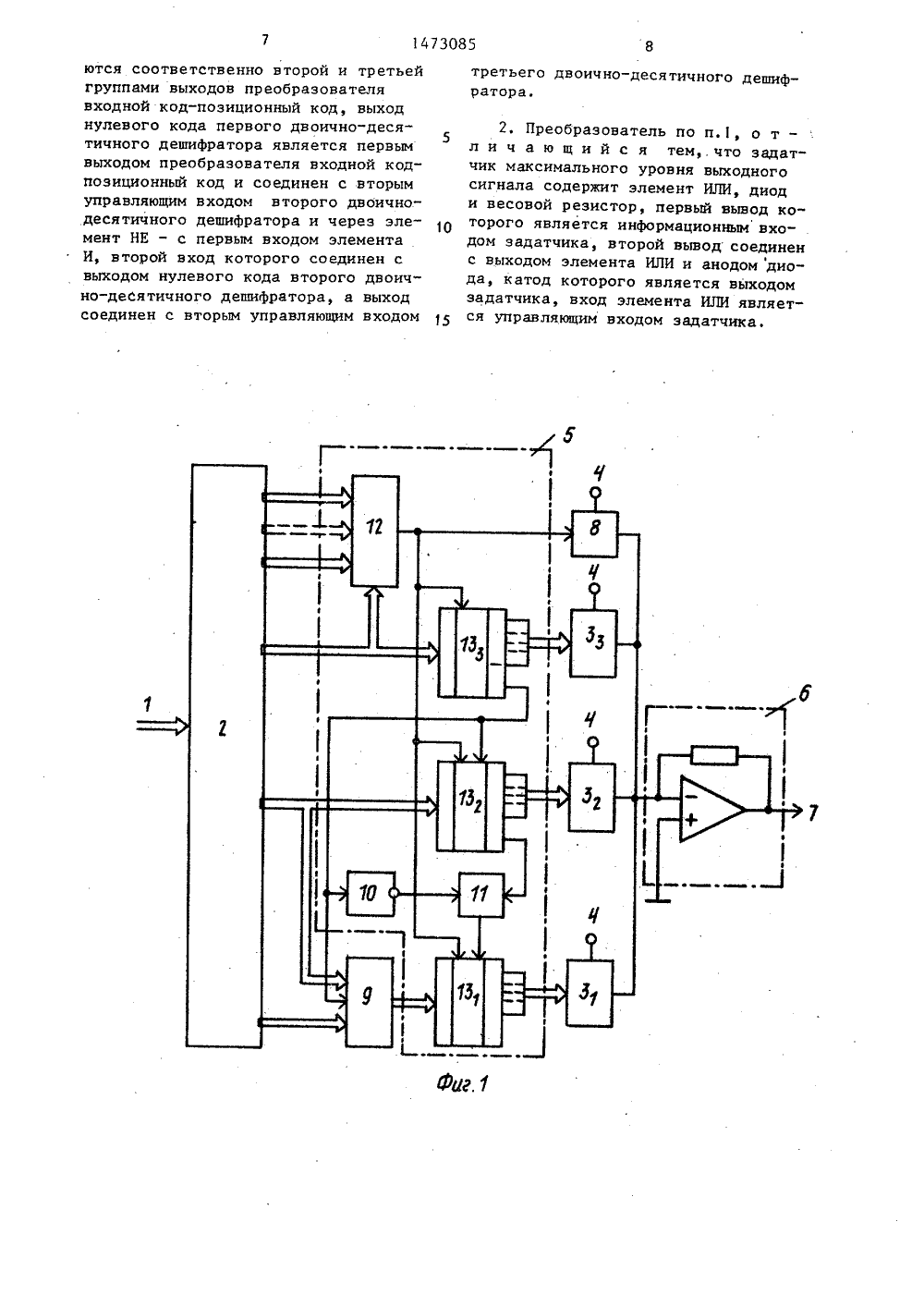

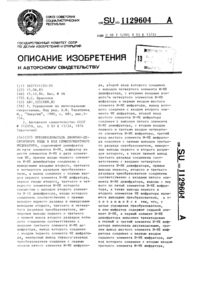

-десятичньЗадатчик го уровня т весовой нала содержиэлемент ИЛИво работае одного сигистор 14,Устройстазам. 1 о 15 идиследую по ходной кододы регист Дво о-десятичнь о шине 1 н де старших ля, на вых ступает разрядов, отлич де элемента ИЛИ диничный сигнал При ом отустанавливается т ОСУДАРСТЭЕННЫЙ КОМИТЕО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯРИ ГКНТ СССР ОПИСАНИЕ К АВТОРСКОМУ СВ(54) ФУНКЦИОНАЛЬНЫЙ ЦИФРОАНАЛПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯКОДА ДЛЯ СЛЕДЯЩИХ СИСТЕМ(57) Изобретение относится клительной технике и может быпользовано в следящих систем ФИзобретение относится к вычислительной технике и может быть использовано в следящих системах, в частности, в позиционных устройствах числового программного управления.Цель изобретения - повышение точности преобразования малых значений входного кода.На фиг.1 представлена функциональная схема устройства; на фиг.2 - пример реализации задатчика максимального уровня выходного сигнала.Устройство содержит входную шину 1, входной регистр 2, кодоуправляемые матрицы 3,-3 весовых резисторов, шину 4 опорного напряжения, преобразователь 5 входной код - позиционный код, преобразователь 6 ток - напряже, ние, выходную шину 7, задатчик 8 максимального уровня выходного сигнала, цифровой коммутатор 9, элемент НЕ. 10,частности в позиционных устройствахчислового программного управления.Преобразователь обеспечивает формирование выходного аналогового сигна- фла, изменяющегося по закону монотонной функции, с максимальной точностьюпреобразования малых значений входного кода, что позволяет обеспечитьнеобходимое для управления сервоприводами позиционных механизмов возрастание точности преобразования кода в аналоговый сигнал по мере приближения к заданной координате и снижения скорости перемещения. 1 з.п. оступает на первые управды двоично-десятичных де 13 - 13 и управляющий вхо 8 максимального уровня выгнала. Единичные сигналы ющих входах дешифраторов их работу и вызывают появичных сигналов на их выхо" ляющие вхошифраторовэадатчикаходного сина управляз апр ещаютление единдах, которые, в свою очередь, запре 1473085и 13В процессе изменения входного кода в диапазоне от 799 до 100 его десятичного эквивалента на выходе нулевого кода дешифратора 13 сохраняется единичный сигнал, а на остальных выходах (кроме выхода единичного кода в данном случае) последовательно возникает нулевой сигнал, управляющий соответствующим последовательным .- включением весовых резисторов кодоу 5 и 55 равляемои матрицы 3 . Единичныи сиг нал с выхода нулевого кода дешифратора 13 запрещает работу дешифрато ра 13 по его второму управляющему входу, разрешает прохождение на вых щают формирование токовых сигналов на выходах кодоуправляемых матриц 3-3. Единичный сигнал, поступающий на управляющий вход задатчика 8, раз. решает прохождение тока с шины 4 с опорного напряжения через весовой ре-, зистор 14 и диод 16 на инвертирующий вход преобразователя 6, в результате чего на шине 7 формируется максималь ный уровень выходного аналогового сигнала.Минимальное значение входного двоично"десятичного кода, вызывающего появление на выходе элемента И 12 15 единичного сигнала, а на шине 7 устройства - максимального уровня аналогового сигнала, задается подключением к входу элемента ИЛИ 12 отдельных разрядов четвертой группы входов преУобразователя 5 с большими весами передаваемых по ним сигналов, например с весами 800 или 800 и 400 и т.д.При подключении к входу, элемента ИЛИ 12 разряда с весом передаваемого 25 кода, равным 800 устройство работает следующим образом.В процессе уменьшения входного двоично-десятичного кода до значения его десятичного эквивалента, равного ЗО 800, на выходе 7 устройства поддерживается максимальный уровень аналогового сигнала. Дальнейшее уменьшение входного кода сопровождается появлением на выходе элемента ИЛИ 12 нулевого сигнала, который через элемент ИЛИ 15 шунтирует ток, проходящий через весовой резистор 14, и запрещает поступление тока с выхода задатчика 8 сигнала на вход преобразователя 6; 40 разрешает работу дешифратора 13, снимает запрет работы по первым управляющим входам дешифраторов 13, коммутатора 9 кода второй декадымладших разрядов регистра 2 и черезэлемент НЕ 1 О совместно с единичнымсигналом на втором входе элемента И11 снимает запрет работы по второмууправляющему входу с дешифратора 13,который формирует,на выходах, соответствующих значениям кода второйдекады младших разрядов регистра 2,нулевой сигнал, управляющий величиной тока, поступающего на инвертирую"щий вход преобразователя 6 с выходакодоуправляемой матрицы 3,. Т.е, впреобразовании входного кода в диапазоне от 799 до 100 его десятичногоэквивалента одновременно участвуютдешифраторы 13, и 1 Зз, в результатечего устройство реализует преобразование вида У = 1 с( ГА 1 ОГВ),которое позволяет аппроксимироватьпреобразование видау = 1(АВС = К словии, что Ко 10 Весятичные экви в входного код гдеА, В,младших р1=1:,2,ра в кодо алент ря 9 - но управля то р весово и мои матрице,зр яда;ер матрицы,ление ь-го ре го я с млад 1 с=1, 2опрот сцы. Последующее уменьшение входного . кода сопровождается появлением нулевого кода третьей декады младших разрядов регистра 2, что вызывает появление на выходе нулевого кода дешифратора 13 нулевого сигнала, который разрешает работу дешифратора 13 по его второму управляющему входу, переключает на выход коммутатора 9 код первой декады младших разрядов регистра 2; через элемент НЕ 10 и элемент И 11, на втором входе которого присутствует единичный сигнал с выхода нулевого кода дешифратора 13, запрещает работу дешифратора 13При изменении входного кода в пределах от 99 до 10 его десятичного эквивалента дешифратор 13 последовательно формирует на своих выходах нулевой сигнал, который управляет вклю5 1473085чением весовых резисторов матрицы 3 .Устройство при этом реализует преоб- сраэование вида у=К В 1 О 30 35 40 45 50 55 При ненулевом коде только первой декады младших разрядов регистра 2 на управляющих входах дешифратора13 присутствуют нулевые сигналы, разрешающие его работу. Дешифратор 13, управляет при этом поочередным включением весовых резисторов матрицы 3 в результате чего устройство реализует преобразование видау = 1 с -А. Рассмотренный вариант реализации устройства предназначен для использования в позиционных устройствах числового программного управления, от которых требуется обеспечить перемещение при больших рассогласованиях на максимальной постоянной скорости, а при позиционировании в точку - движение с постоянным ускорением. При этом максимальная абсолютная точность преобразования необходима при подходе к заданной координате, а в начале торможения достаточно обеспечить небольшую величину относительной погрешности преобразования. Формула из обр етения 1. Функциональный цифроаналоговый преобразователь двоично-десятичного кода для следящих систем, содержащий шину опорного напряжения, входной регистр, входы которого являются вход- ной шиной, а выходы декад старших разрядов соединены соответственно с первой группой входов преобразователя входной код - позиционный код, выходы первой группы которого соединены соответственно с управляющими входами первой кодоуправляемой матрицы ве" совых резисторов, о т л и ч а ющ и й с я тем, что, с целью повьппения точности преобразования малых значений входного кода, в него введены две кодоуправляемые матрицы весовых реэистеров, преобразователь ток - напряжение, задатчик максимального уровня выходного сигнала и цифровой коммутатор, информационные входы первой группы которого соединены с выходами первой декады младших разрядов входного регистра, информацион 5 10 15 20 25 ные входы второй группы объединены оответственно с одноименными входами второй группы преобразователя . входной код-позиционный код и подключены соответственно к выходам второй декады младших разрядов входного регистра, управляющий вход и выход цифрового коммутатора соединены с первым выходом и соответствующими входами третьей группы преобразователя входной код-позиционный код соответственно, входы четвертой группы которого подключены к соответствующим выходам третьей декады младших разрядов входного регистра, второй выход преобразователя входной кодпоэиционный код соединен с управляющим входом задатчика максимального уровня выходного сигнала, выходы вто-. ройи третьей групп соединены соответственно с управляющими входами второй и третьей кодоуправляемых мат-. риц весовых резисторов, выходы которых, выход первой кодоуправляемой мат. матрицы весовых резисторов и выходэадатчика максимального уровня выходного сигнала объединены и соединеныс инвертирующим входом преобразовате"ля ток-напряжение, неинвертирующий вход которого подключен к шине нулевого потенциала, а выход являетсявыходной шиной, информационные входыпервой, второй и третьей кодоуправляемых матриц весовых резисторов и задатчика максимального уровня выходного сигнала подключены к шине опор"ного напряжения, при этом преобразователь входной код-позиционный кодвыполнен на трех двоично-десятичных дешифраторах, элементе И, элементе НЕи элементе ИЛИ, п групп входов которого являются первой группой входовпреобразователя, входной код-позиционный код, (и+1)-я группа входов иинформационные входы первого двоично-десятичного дешифратора являютсячетвертой группой входов преобразователя входной код-позиционный код, выход элемента ИЛИ является вторым вы"ходом преобразователя входной кодпозиционный код и срединен с первымиуправляющими входами первого, второго и третьего двоично-десятичных дешифраторов, информационные входы второго и третьего из которых являютсясоответственно второй и третьей группами входов преобразователя входнойкод-позиционный код, а выходы явля 1473085ются соответственно второй и третьейгруппами выходов преобразователявходной код-позиционный код, выходнулевого кода первого двоично-десятичного дешифратора является первымвыходом преобразователя входной кодпозиционный код и соединен с вторымуправляющим входом второго двоичнодесятичного дешифратора и через элемент НЕ - с первым входом элементаИ, второй вход которого соединен свыходом нулевого кода второго двоично-десятичного дешифратора, а выходсоединен с вторым управляющим входом третьего двоично-десятичного дешифратора,52. Преобразователь по п.1 о т -ул и ч а ю щ и й с я тем,. что задатчик максимального уровня выходногосигнала содержит элемент ИЛИ, диоди весовой резистор, первый вывод которого является информационным входом задатчика, второй вывод соединенс выходом элемента ИЛИ и анодом диода, катод которого является выходомзадатчика, вход элемента ИЛИ является управляющим входом задатчика.473085 Составитель З,Моисеенкобченко Техред А,Кравчук Корректор Л.Зайцев дакт Тираж 88 Подписи Производственно-издательский комбинат Патент", г. Ужгород, ул. Гагар Заказ 1728/57ВНИИПИ Госуда енного коми 13035, Моск та по изобре Ж, Рауш ениям и открькая наб д. ям при ГКНТ ССС5

СмотретьЗаявка

4050567, 07.04.1986

ПРЕДПРИЯТИЕ ПЯ Р-6115

НОВИКОВ ЛЕОНИД ЯКОВЛЕВИЧ, БОБРОВ ВИКТОР ФЕДОРОВИЧ, ИВАНОВА ГАЛИНА СЕРГЕЕВНА

МПК / Метки

МПК: H03M 1/82

Метки: двоично, десятичного, кода, систем, следящих, функциональный, цифроаналоговый

Опубликовано: 15.04.1989

Код ссылки

<a href="https://patents.su/5-1473085-funkcionalnyjj-cifroanalogovyjj-preobrazovatel-dvoichno-desyatichnogo-koda-dlya-sledyashhikh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Функциональный цифроаналоговый преобразователь двоично десятичного кода для следящих систем</a>

Предыдущий патент: Цифроаналоговый преобразователь

Следующий патент: Преобразователь кода во временной интервал

Случайный патент: Устройство для обработки тонкостенных цилиндрических деталей