Преобразователь коэффициента амплитудной модуляции в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1429055

Автор: Максимов

Текст

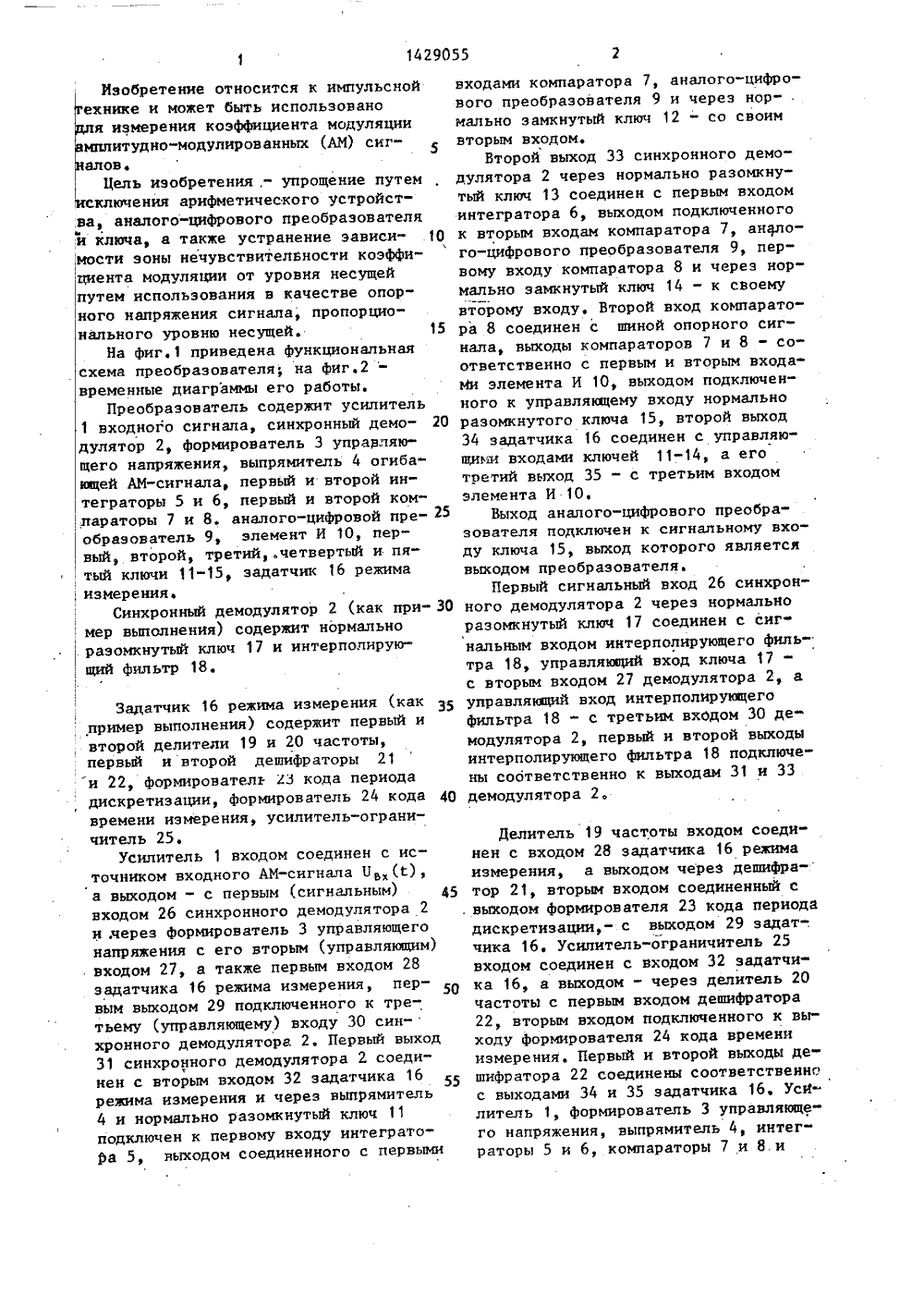

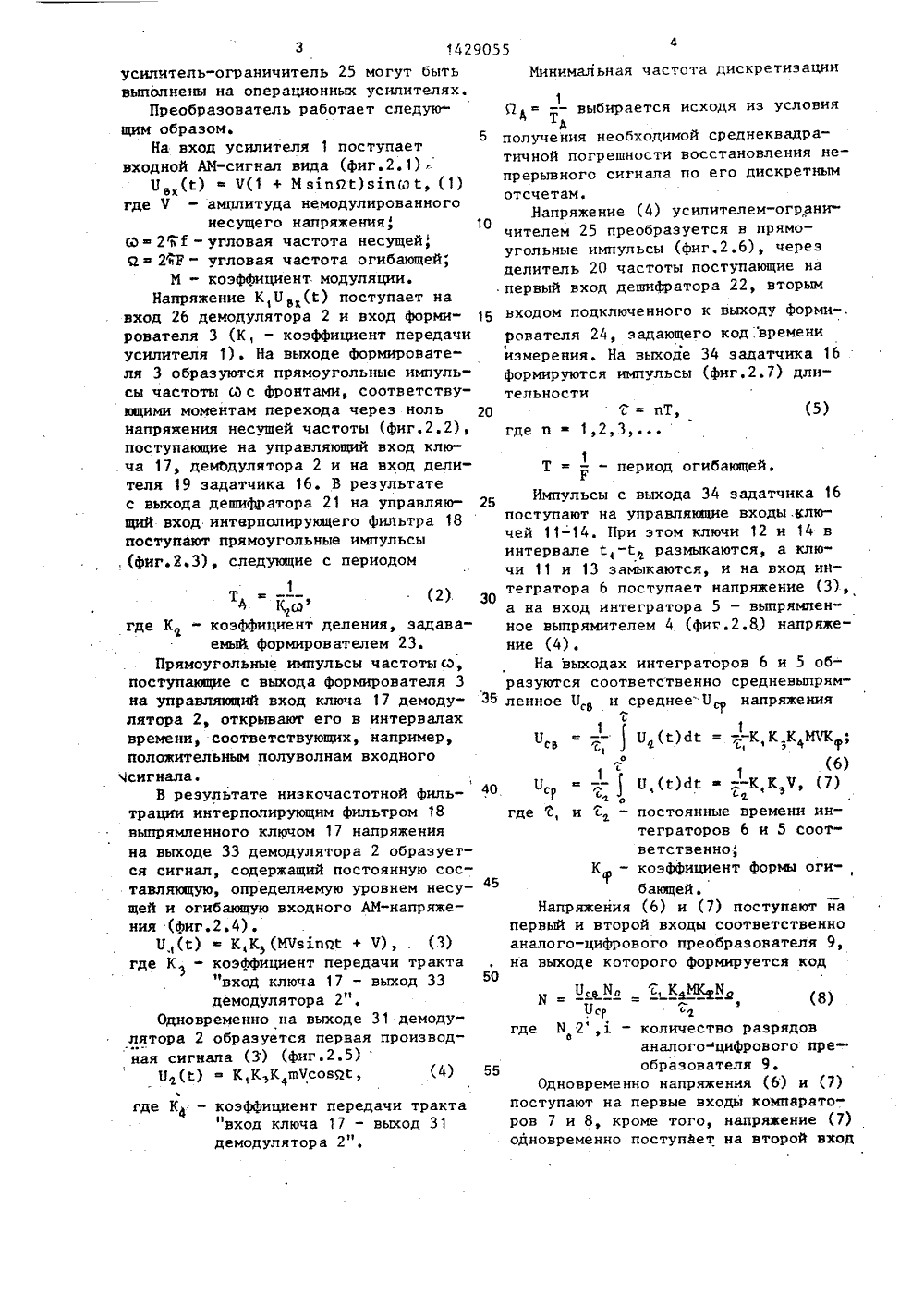

СОЮЗ СО 8 ЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН ИЯ ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ ИЗОБ Н АВТОРСКОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетельство СССРВ 1337830, кл. С 01 К 29/06, 1986.(54) ПРЕОБРАЗОВАТЕЛЬ КОЭФФИЦИЕНТААМПЛИТУДНОЙ МОДУЛЯЦИИ В КОД(57) Изобретение относится к импульсной технике и может быть использовано для измерения коэффициента модуляции амплитудно-модулированных сигналов. Цель изобретения - упрощение иустранение зависимости зоны нечувствительности коэффициента модуляцииот уровня несущей - достигается тем,что в преобразователе коэффициентаамплитудной модуляции в код, содержа,80429055 А 1 щем усилитель 1 входного сигнала,синхронный демодулятор 2, формирователь 3 управляющего напряжения, эадатчик 16 режима измерения, выпрямитель 4, ключи 11-15, интеграторы 5,6, компараторы 7, 8, аналого-циФровой .преобразователь 9, элемент И 10, выходинтегратора 5 соединен с первымвходом аналого-цифрового преобразователя 9, выход интегратора 6 - с втбрым входом аналого-цифрового преобразователя 9 и с вторым входом компаратора 8, третий выход задатчика 16режима измерения соединен с третьимвходом элемента И 10, выход аналого"цифрового преобразователя 9 - с сигСнальным входом ключа 15, выход которого являетсявыходом преобразователя. 2 ил.С:входами компаратора 7, аналого-цифрового преобразователя 9 и через нор- .мально замкнутый ключ 12 - со своимвторым входом.Второй выход 33 синхронного демодулятора 2 через нормально разомкнутый ключ 13 соединен с первым входоминтегратора 6, выходом подключенного к вторым входам компаратора 7, аналого-цифрового преобразователя 9, первому входу компаратора 8 и через нормально замкнутый ключ 14 - к своемувторому входу. Второй вход компаратора 8 соединен с шиной опорного сигнала, вьжоды компараторов 7 и 8 - соответственно с первым и вторым входами элемента И 10, выходом подключенного к управляющему входу нормально разомкнутого ключа 15, второй выход34 задатчика 16 соединен с управляющими входами ключей 11-14, а еготретий вьжод 35 - с третьим входом элемента И 10Выход аналого-цифрового преобразователя подключен к сигнальному входу ключа 15, выход которого являетсявыходом преобразователя.Первый сигнапьный вход 26 синхронного демодулятора 2 через нормально разомкнутый ключ 17 соединен с сигнальным входом интерполирующего фильтра 18, управляющий вход ключа 17- с вторым входом 27 демодулятора 2, а управляющий вход интерполирующего фильтра 18 - с третьим входом 30 демодулятора 2, первый и второй выходы интерполирующего фильтра 18 подключены собтветственно к выходам 31 и 33 демодулятора 2 Изобретение относится к импульсной ехнике и может быть использованоя измерения коэффициента модуляции мплитудно-модулированных (АМ) сиг 5 алов.Цель изобретения,- упрощение путем исключения арифметического устройства, аналого-цифрового преобразователя и ключа, а также устранение эависи ,мости зоны нечувствителвности коэффициента модуляции от уровня несущей путем использования в качестве опор" ного напряжения сигнала, пропорционального уровню несущей. 15На фиг.1 приведена функциональная схема преобразователя; на фиг.2 - временные диаграммы его работы.Преобразователь содержит усилитель1 входного сигнала, синхронньй демо дулятор 2, формирователь 3 управляющего напряжения, выпрямитель 4 огибающей АМ-сигнала, первый и второй интеграторы 5 и 6, первый и второй компараторы 7 и 8. аналого-циФровой пре обраэователь 9, элемент И 10, пер вый, второй, третий,.четвертый и пятый ключи 11-15, эадатчик 16 режима ,измерения.Синхронньй демодулятор 2 (как пример выполнения) содержит нормальнораэомкнутьй ключ 1 и интерполирую, щий фильтр 18,Задатчик 16 режима измерения (как пример выполнения) содержит первый и второй делители 19 и 20 частоты, первый и второй дешифраторы 21 и 22, формировател 23 кода периода дискретизации, формирователь 24 кода 40 времени измерения, усилитель-ограничитель 25.Усилитель 1 входом соединен с источником входного АМ-сигнала БьИ), а выходом - с первым (сигнальным) входом 26 синхронного демодулятора 2 и через формирователь 3 управляющего напряжения с его вторым (управляющим) входом 27, а также первым входом 28 задатчика 16 режима измерения, первым выходом 29 подключенного к третьему (управляющему) входу 30 синхронного демодулятора 2, Первый выход 31 синхронного демодулятора 2 соединен с вторым входом 32 задатчика 16 режима измерения и через выпрямитель 4 и нормально разомкнутый ключ 11 подключен к первому входу интегратора 5, выходом соединенного с первыми Делитель 19 частоты входом соединен с входом 28 задатчика 16 режима измерения, а выходом через дешифратор 21, вторым входом соединенньй с выходом формирователя 23 кода периода дискретизации,- с выходом 29 задат-. чика 16. Усилитель-ограничитепь 25 входом соединен с входом 32 задатчика 16, а выходом - через делитель 20 частоты с первым входом дешифратора 22, вторым входом подключенного к вы" ходу формирователя 24 кода времени измерения. Первый и второй выходы дешифратора 22 соединены соответственно с выходами 34 и 35 задатчика 16. Ус 1- литель 1, формирователь 3 управляющего напряжения, выпрямитель 4, интеграторы 5 и 6, компараторы 7 и 8.и3 142 усилитель-ограничитель 25 могут быть выполнены на операционных усилителях.Преобразователь работает следующим образом.На вход усилителя 1 поступает входной М-сигнал вида (фиг.2.1) .Ц (й) = Ч(1 + М здпйй) здпц , (1) где Ч - амплитуда немодулированногонесущего напряжения, Я щ 2 Е - угловая частота несущей, Ю2%7 - угловая частота огибающей;М - коэффициент модуляции.Напряжение К,Ц И) поступает на вход 26 демодулятора 2 и вход формирователя 3 (К, - коэффициент передачи усилителя 1). На выходе формирователя 3 образуются прямоугольные импульсы частоты Я с фронтами, соответствующими моментам перехода через ноль напряжения несущей частоты (фиг.2.2), поступающие на управляющий вход ключа 17, демодулятора 2 и на вход делителя 19 задатчика 16. В результате с выхода дешифратора 21 на управляющий вход интврполирующего фильтра 18 поступают прямоугольные импульсы ,(фиг.2.3), следующие с периодом(2)д к,агде К " коэффициент деления, задаваемый формирователем 23.Прямоугольные импульсы частоты со,поступающие с выхода формирователя 3на управляющий вход ключа 17 демодулятора 2, открывают его в интервалахвремени, соответствующих, например,положительным полуволнам входного Чсигнала.В результате низкочастотной фильтрации интерполирующим фильтром 18вьп 1 рямленного ключом 17 напряженияна выходе 33 демодулятора 2 образуется сигнал, содержащий постоянную составляк)щую, определяемую уровнем несущей и огибающую входного АМ-напряжения (фиг.2.4).Ц,(е) - К,(МЧздпж + Ч), . (3)где К - коэффициент передачи трактаЭвход ключа 17 - выход 33демодулятора 2".Одновременно на выходе 31 демодулятора 2 образуется первая производная сигнала (3) (фиг.2,5)Ц(Е) К,К К шЧсозае, (4)где К 4: - коэффициент передачи тракта"вход ключа 17 - выход 31демодулятора 2". 9055 Минимальная частота дискретизации Йдвыбирается исходя из условия1д тд5 получения необходимой среднеквадратичной погрешности восстановления непрерывного сигнала по его дискретнымотсчетам..Напряжение (4) усилителем-ограничителем 25 преобразуется в прямоугольные импульсы (фиг,26), черезделитель 20 частоты поступающие напервый вход дешифратора 22, вторымвходом подключенного к выходу форми-.рователя 24, задающего код .времениизмерения. На выходе 34 задатчика 16формируются импульсы (фиг.2.7) длительности20 с пт, (5)где и 1,2,3,Т-- период огибающЕй1ГИмпульсы с выхода 34 задатчика 16поступают на управлянхцие входы .ключей 11-14. При этом ключи 12 и 14 винтервале - размыкаются, а ключи 11 и 13 замыкаются, и на вход интегратора 6 поступает напряжение (3),а на вход интегратора 5 - выпрямленное выпрямителем 4 (фих.2.8) напряжение (4) .На выходах интеграторов 6 и 5 образуются соответственно средневыпрям ленное Ц и среднее"Ц напряжениялЦс -Ц (й)йй = -К,К К, МЧК 31 1св , а10 с 7(й)дй - К,К 7, (7)огде с, и- постоянные времени интеграторов Ь и 5 соответственно,К - коэффициент формы оги-, 45б ающей.Напряжения (6) и (7) поступают йапервый и второй входы соответственноаналого-цифрового преобразователя 9,на выходе которого формируется код 50Цс о 1 ЩдУсргде М, 2,д - количество разрядованалогоцифрового пре обраэователя 9.Одновременно напряжения (6) и (7)поступают на первые входы компараторов 7 и 8, кроме того, напряжение (7)одновременно постунает на второй входкомпаратора 7. Компаратор 8, сравнивая напряжение (7) с уровнем опорно- гЬ напряжения П , определяет минимально допустимый уровень нопряжения несущей, а компаратор 7, сравнивая напряжение (6) с уровнем напряжения (1), определяет минимально допустимое значение коэффициента модуляции.При этом пороги срабатывания комп раторов 7 и 8 следующие(9) (10) г е К .и К - коэффициенты передачипо вторым входам компараторов 7 и 8 соответственно,Иэ (9) с учетом (7) можно получить в ажение для минимально допустимого э ачения коэффициента модуляции, КфКфПри выполнении условий (10) и (11)и, наличии единичного сигнала на выходеЭр задатчика 16 в интервале -й(Фиг.2.9) выходной сигнал элементаИ 10 открывает ключ 15, транслирующийна выход устройства код (8) . Ф о р м у л а изобретенияПреобразователь коэффициента, амитудной модуляции в код, содержащий усилитель входного сигнала, выходом подключенный к первому входу синхронЙого демодулятора и через формирователь управляющего напряжения " к вторрму входу синхронного демодулятора и к первому входу задатчика режима ,измерения, первым выходом соединенно.1 го с третьим входом синхронного демодулятора, первый выход синхронногодемодулятора подключен к второму входу эадатчика режима измерения и черезвыпрямитель и первый ключ к первомувходу первого интегратора, выходом,соединенного с первым входом первогокомпаратора и через второй ключ свторым входом интегратора, второй вы" 10 ход синхронного демодулятора черезтретий ключ прдключен к первому входувторого интегратора, выходом соединенного с первым входом второго компаратора и через четвертый ключ с 15 вторым входом второго интегратора,второй вход второго компаратора под"кпючен к шине опорного сигнала, вы, ходы первого и второго компарторовсоединены соответственно с первым и 20 вторым входами элемента И, выходомсоединенного с управлякщим входом пятато ключа, управлякщие входы перво- .го, второго, третьего и четвертогоключей подключены к второму выходу 25 задатчика режима измерения, а также,цифроаналоговый преобразователь, о тл и ч а ю щ и й с я тем, что, с цельюупрощения и устранения зависимостизоны нечувствительности коэффициента З 0 модуляции от уровня несущей, выходпервого интегратора подключен к первому входу аналого-цифрового преобра"зователя, выход второгО интегратора -к второму входу аналого-цифровогопреобразователя и к второму входупервого компаратора, третий выход задатчика режима измерения соединен стретьим входом элемента И, выход аналого-цифрового преобразователя - с 40 сигнальным входом пятого ключа выход которого является выходом преобразователя.,Муска тор В,Даик торно о Заказ 5121 4 оизводственно-полиграфическое предприятие, гУжгород, ул. Проектная Составитель Л.СорокиТехред А.ЕРавчУк Тираж 772 ВПИИПИ Государственного комит по делам изобретений и отк 3035, Москва, Ж, Раушская нПодпи та ССС ытий б., д.

СмотретьЗаявка

4206666, 05.03.1987

ПРЕДПРИЯТИЕ ПЯ М-5156

МАКСИМОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G01R 29/06

Метки: амплитудной, код, коэффициента, модуляции

Опубликовано: 07.10.1988

Код ссылки

<a href="https://patents.su/5-1429055-preobrazovatel-koehfficienta-amplitudnojj-modulyacii-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь коэффициента амплитудной модуляции в код</a>