Программное устройство для формирования адресов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

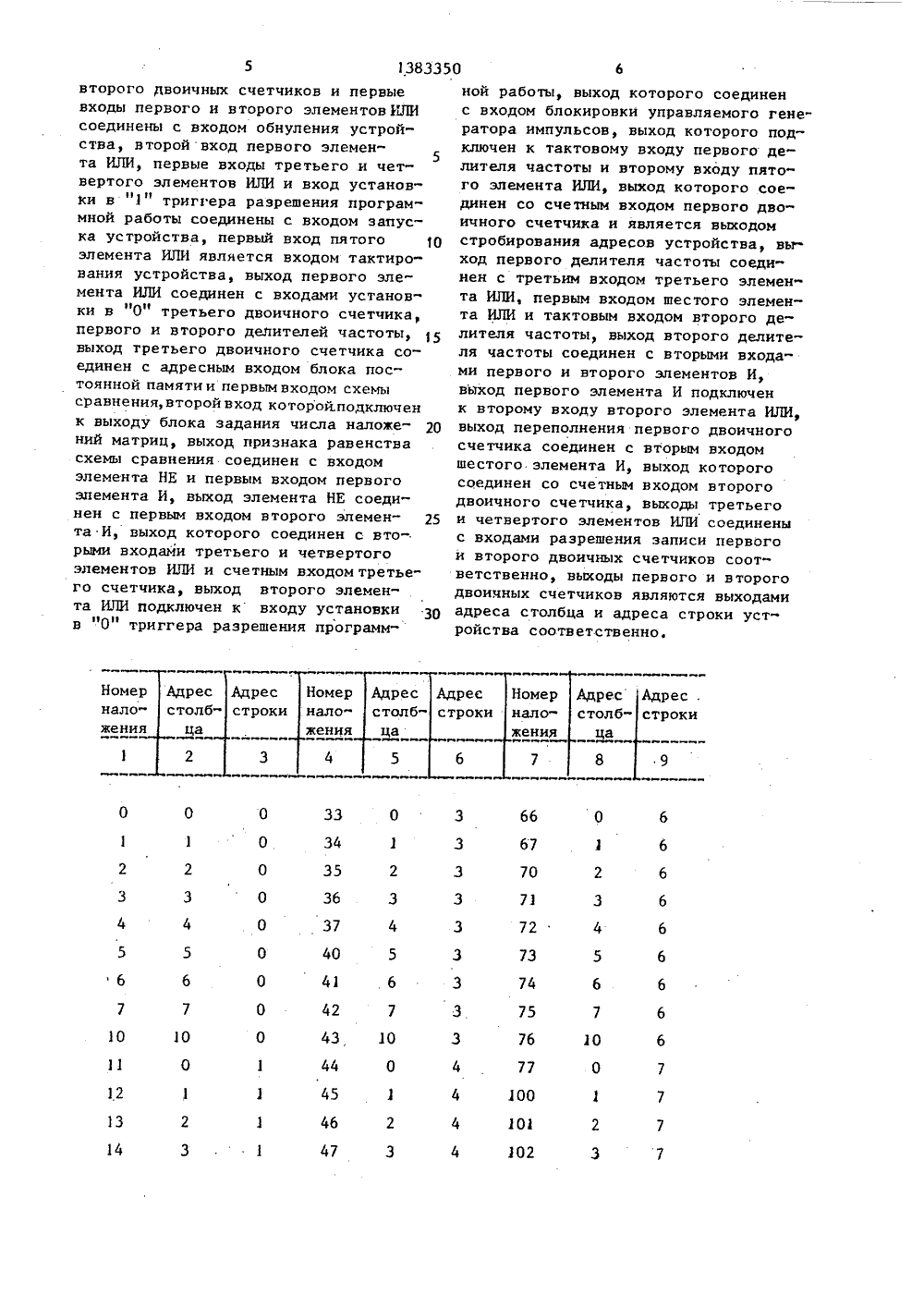

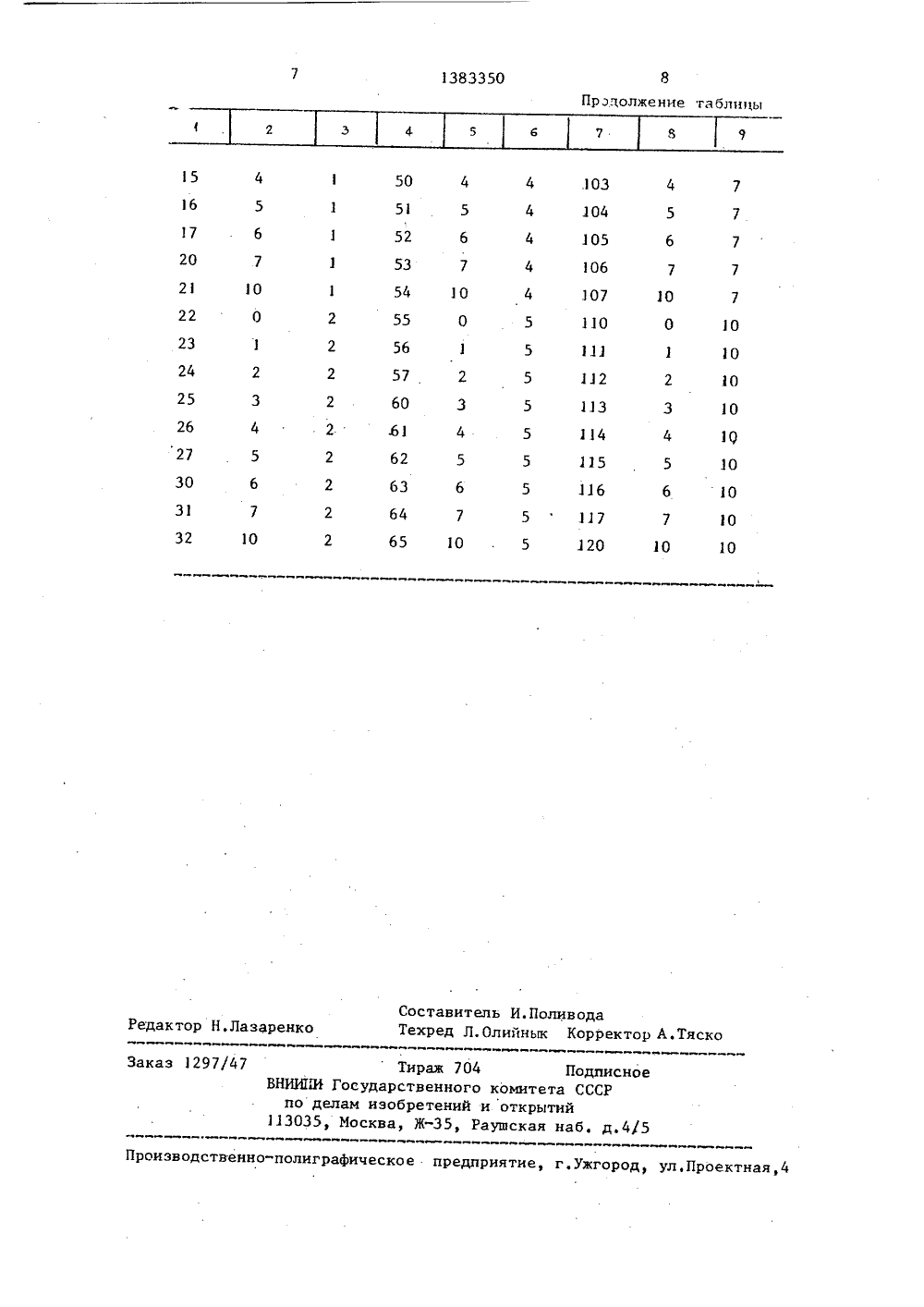

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН Я ВУ А в ячеания вательного фек оперативнтельного перройство длядержит два дв9 посто рмй ополн ания. У адресов программир ормировани оичных сче иной памят 2е 7блок упов с имп ыи генератравнения,ы 23 иатрицыения и такательного ф ыхоапуска истолбцоввходы 1 ес 03 24 ад ячеек н ма последоадр есов,15, 18,19, 20,ений мат 10 разре жн ванияирован ов ИЛИ 4,11,я числа наложНЕ 8, триггермной работы, двастоты, два злеменоичный счетчик 5рования адреса, 1 есть злеме лок 6 зада ешения програмля 3 и 14 чИ 16 и 17, двход 25 строб абл ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АНИЕ ИЗ СКОМУ СВИДЕТЕ(56) Авторское свидетельство СССР В 739533, кл. С 06 Р 9/00, 1980.Авторское свидетельство СССР В 726530, кл. С 06 Р 9/00, 1980, (54) ПРОГРАММНОЕ УСТРОИСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ(57) Изобретение относится к вычислительной технике и может быть использовано для управления записью и считыванием данных в специализирован ных вычислителях систем распознавания образов. Цель изобретения - повышение быстродействия и расширение функциональных воэможностей за счет обеспечения программного и последо 1 51) 4 С 06 Е 9/00 121 138335Изобретение относится к вычислительной технике и может быть использовано для построения блоков управления записью и считыванием данных в,1) специализированных вычислителях систем распознавания образов.Цель изобретения - повышение быстродействия и расширение функциональных возможностей за счет обеспечения программного и последовательного формирования адресов ячеек оперативной памяти без дополнительного перепрограммирования.На чертеже представлена функциональная схема. устройства.Устройство содержит вход 1 обнуления, вход 2 запуска, вход 3 тактирования режима последовательного формирования адресов, элемент ИЛИ 4, двоичный счетчик 5, блок 6 задания числа наложений. матриц, схему 7 сравнения, . элемент НЕ 8, блок 9 постоянной памяти, триггер 10 разрешения программной работы, элемент ИЛИ 11, управляемый генератор 12 импульсов, делители 13 и 14 частоты,. элемент ИЛИ 15, элементы И 16 и 17, элементы ИЛИ 18-20 двоичные счетчики 21 и 22 соответственно столбцов и строк матрицы яче- ЗО ек оперативной памяти, выходы 23 и 24 адреса соответственно столбцов и строк матрицы ячеек ОЗУ, выход 25 стробирования адреса.Описание работы программного устройства проводится применительно к матрице оперативной памяти, содержащей ИхМ элементов, где И - число столбцов матрицы; М - число строк матрицы. В случае записи данных про изводится последовательный перебор адресов ячеек матрицы из БхМ элементов но столбцам и строкам, в случае считывания данных - выработка групп адресов соседних ячеек оперативной 45 памяти, составляющих матрицу меньшего размера пхш, где и ; число столбцов малой матрицы; ш - число строк малой матрицы. Число таких групп адресных последовательностей равно чис п лу всех возможных наложений малой матрицы на большую и равно (Б-и+1)х х(М-ш+1)В исходном состоянии высокий уровень сигнала на входе 1 обнуления, поступая на входы обнуления двоичных счетчиков 21 и 22, а через элементы ИШ 1 4 и 11 соответственно на входы обнуления двоичного счетчика 5, делителей 13 и 14 частоты, триггера 10разрешения программной работы, удерживает их в нулевом состоянии. На информационном выходе блоков заданиячисла наложений матриц устанавливается код числа (Б-и+1) (1-т+1)-11.Переход уровня сигнала на входе 1в низкое состояние разрешает работуустройства.В режиме последовательного формирования адресов на вход 3 тактирования подается серия иэ МхМ прямоугольных импульсов, которые, проходя через элемент ИЛИ 15, поступают навход тактирования счета двоичногосчетчика 21 и на выход 25 стробирования адресов. Переключение двоичногосчетчика 21 происходит по спадамэтих импульсов, Емкость счетчика 21равна Б, поэтому после выработки Мадресов первой и всех последующихстрок ячеек матрицы оперативной памяти на его выходе переполнения формируется импульс, который через элемент ИЛИ 18 поступает на вход тактирования счета двоичного счетчика 22,емкость которого равна М. Второй двоичный счетчик 22, срабатывая по спадам импульсов, поступающих на еговход тактирования счета, формируетна своих информационных выходах адреса М строк ячеек матрицы оперативнойпамятиКаждый очередной импульс,поступающий на выход 25 стробированияадреса, своим передним фронтом стробирует адреса, появившиеся послеспада предыдущего импульса стробирования на выходах 23 и 24 адреса столбцов и строк матрицы оперативной памятии,Запуск программного режима формирования адресов производится подачей прямоугольного импульса на вход 2 запуска, который проходя через элемент ИЛИ 4, обнуляет двоичный счетчик 5 и делители 13 и 14 частоты, а также проходя через элементы ИЛИ 19 и 20, загружает в двоичные счетчики 21 и 22 адрес соответственно по столбцу и строке начального элемента первого наложения малой матрицы на большую, кроме того устанавливают триггер 10 разрешения программной работы в единичное состояние, которое разрешает формирование управляемым генератором 12 прямоугольных импульсов. Импульсы генератора 12 поступают через элемент ИЛИ 15 на выход 25 стробирования адреса, где своим передним фронтом стробируют сформированные программным устройством адре 5 са, Кроме того, импульсы генерато-ра 12 поступают через элемент ИЛИ 15 на вход тактирования счета двоичного счетчика 21, который, переключаясь по их спадам, вырабатывает на своих 10 информационных выходах адреса столбцов матрицы оперативной памяти, Одновременно импульсы управляемого генератора 12 пересчитываются делителем 13 частоты, на выходе которого по 15 спаду каждого п-го импульса формируются короткие импульсы. Последние, проходя через элемент ИЛИ 18, поступают на вход тактирования счета двоичного счетчика 22, вырабатывающего 20 адреса строк матрицы оперативной памяти, а также, проходя через элемент ИЛИ 19, поступают на вход стробирования параллельной загрузки .двоичного счетчика 21, фиксируя в нем25 вновь адрес столбца, на котором расположен начальный элемент первого наложения малой матрицы на большую,кроме того, пересчитываются делителем 14 частоты, на выходе которого по спаду 30 каждого ш-го входного импульса формируются короткие импульсы, Поскольку в исходном состоянии двоичный счетчик 5 обнулен, а на выходе блока 6 задания числа наложений матриц вы- ;35 ставлено значение кода, соответствующего числу (И-и+1) (М-ш+ 1) - 1, с выхода схемы 7 сравнения поступает низкий уровень сигнала, который, инвертируясь элементом НЕ 8, разрешает прохождение импульсов с выхода делителя 14 частоты через элемент И 17 на вход тактирования счета двоичного счетчика 5. Последний переключаясь по передним фронтам этих им пульсов, осуществляет счет групп адресов иначе наложенной малой матрицы на большую. Каждому номеру очередного наложения, поступающему с выхода счетчика 5 на адресные входы блока 9 постоянной памяти, в последнем поставлено в соответствие значение адресов столбца и строки начального элемента данного наложения. Импульсы выхода делителя 14 частоты, проходя через элемент И 17 и элементыИЛИ 1955 и 20, фиксируют значение адресов столбца и строки начального элемента каждого очередного наложения во втором и третьем двоичных счетчиках 21 и 22.На (Б-и+1)(М-ш+1)-1 -м наложении на выходе схемы 7 сравнения появляется высокий уровень сигнала, который разрешает прохождение очередного импульса с выхода второго делителя 14 частоты через первый элемент И 16 и второй элемент ИЛИ 11 на вход сброса триггера 10 разрешения программной работы, которьй, сбросившись, запрещает работу управляемого генератора 12 импульсов. Тем самым завершается цикл программного формирования адресов, представляющий собой однократное сканирование малой матрицей из пхш элементов .о большой матрице ОЗУ из Б х М элементов .Данные прожига блока 9 в восьмеричных кодах для Б = М = 16 и = - ш = 8 ю и(37-и+1)(М-ш+)-1 = 80, = - 120 представлены в таблице.За один цикл наложений малой матрицы на большую адреса элементов большой матрицы вырабатываются программным устройством разное число раз, в зависимости от того, в скольких наложениях малой матрицы на большую участвует каждый данный элемент матрицы оперативной памяти, т,е. осуществляется разночастотный опрос ячеек матрицы оперативной памяти.формула изобретенияПрограммное устройство для формирования адресов, содержащее два дво ичных счетчика, блок постоянной памяти, управляемый, генератор импульсов и схему сравнения, первый и второй выходы блока постоянной памяти подключены к информационным входам первого и второго двоичных счетчиков соответственно, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет обеспечения программного и последовательного формирования адресов ячеек оперативной памяти без дополнительного перепрограммирования, в него введены третий двоичный счетчик, два делителя частоты, блок задания числа наложений матрицы, триггер разрешения программной работы, два элемента И, шесть элементов ИЛИ и элемент НЕ, причем входы установки в "0" первого и1383350 10 15 20 25 30 Номе Номер Адрес нало- столб мер Адреало- стол ния ца с рес Адр олб- стр ца рок ро ло ия ц н 9 6 0 О О 3 О 2 7 6 О 7 4 5 3 3 66 6 О О О О 5второго двоичных счетчиков и первыевходы первого и второго элементов ИЛИ соединены с входом обнуления устройства, второй вход первого элемента ИЛИ, первые входы третьего и четвертого элементов ИЛИ и вход установки в "1" триггера разрешения программной работы соединены с входом запуска устройства, первый вход пятого элемента ИЛИ является входом тактирования устройства, выход первого элемента ИЛИ соединен с входами установки в "О" третьего двоичного счетчика,первого и второго делителей частоты,выход третьего двоичного счетчика соединен с адресным входом блока постоянной памятии первымвходом схемы сравнения,второйвход которойподключен к выходу блока задания числа наложений матриц, выход признака равенствасхемы сравнения соединен с входомэлемента НЕ и первым входом первогоэлемента И, выход элемента НЕ соединен с первым входом второго элемента И, выход которого соединен с вторыми входайи третьего и четвертого элементов ИЛИ и счетным входом третье" го счетчика, выход второго элемента ИЛИ подключен к входу установки в "О" триггера разрешения программной работы, выход которого соединенс входом блокировки управляемого генератора импульсов, выход которого подключен к тактовому входу первого делителя частоты и второму входу пятого элемента ИЛИ, выход которого соединен со счетным входом первого двоичного счетчика и является выходомстробирования адресов устройства, выход первого делителя частоты соединен с третьим входом третьего элемента ИЛИ, первым входом шестого элемента ИЛИ и тактовым входом второго делителя частоты, выход второго делителя частоты соединен с вторыми входами первого и второго элементов И,выход первого элемента И подключенк второму входу второго элемента ИЛИ,выход переполнения первого двоичногосчетчика соединен с вторвм входомшестого элемента И, выход которогосоединен со счетным входом второгодвоичного счетчика, выходы третьегои четвертого элементов ИЛИ соединеныс входами разрешения записи первогои второго двоичных счетчиков соответственно, выходы первого и второгодвоичных счетчиков являются выходамиадреса столбца и адреса строки устройства соответственно.. 03 16 104 17 105 20 106 10 107 21 22 110 23 24 60 3 113 2661 4 62 5 63 6 64 7 65 10 114 115 30 7 31 117 10 120 Составитель И.ПоливодаТехред Л.Олийнык Корректор А.Тяско Редактор Н.Лазаренко Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб. д.415 Эаказ 1297/47 Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная,4 50 4 5 5 52 6 53 7 54 10 55 0 56 57 2 4 75 7.6 77 710 70 101 1 О2 О3 104 105 106 107 1 О1 О 1 О

СмотретьЗаявка

4130310, 08.10.1986

ПРЕДПРИЯТИЕ ПЯ В-2725

АНДРЕЕВ БОРИС МИХАЙЛОВИЧ, ЛЕУХИН СЕРГЕЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 12/06, G06F 9/00

Метки: адресов, программное, формирования

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/5-1383350-programmnoe-ustrojjstvo-dlya-formirovaniya-adresov.html" target="_blank" rel="follow" title="База патентов СССР">Программное устройство для формирования адресов</a>

Предыдущий патент: Сумматор в знакоразрядной позиционно-остаточной системе счисления

Следующий патент: Устройство переменного приоритета

Случайный патент: Устройство для ориентирования датчиков в скважине