Устройство управления для процессора быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1270775

Авторы: Карташевич, Ходосевич

Текст

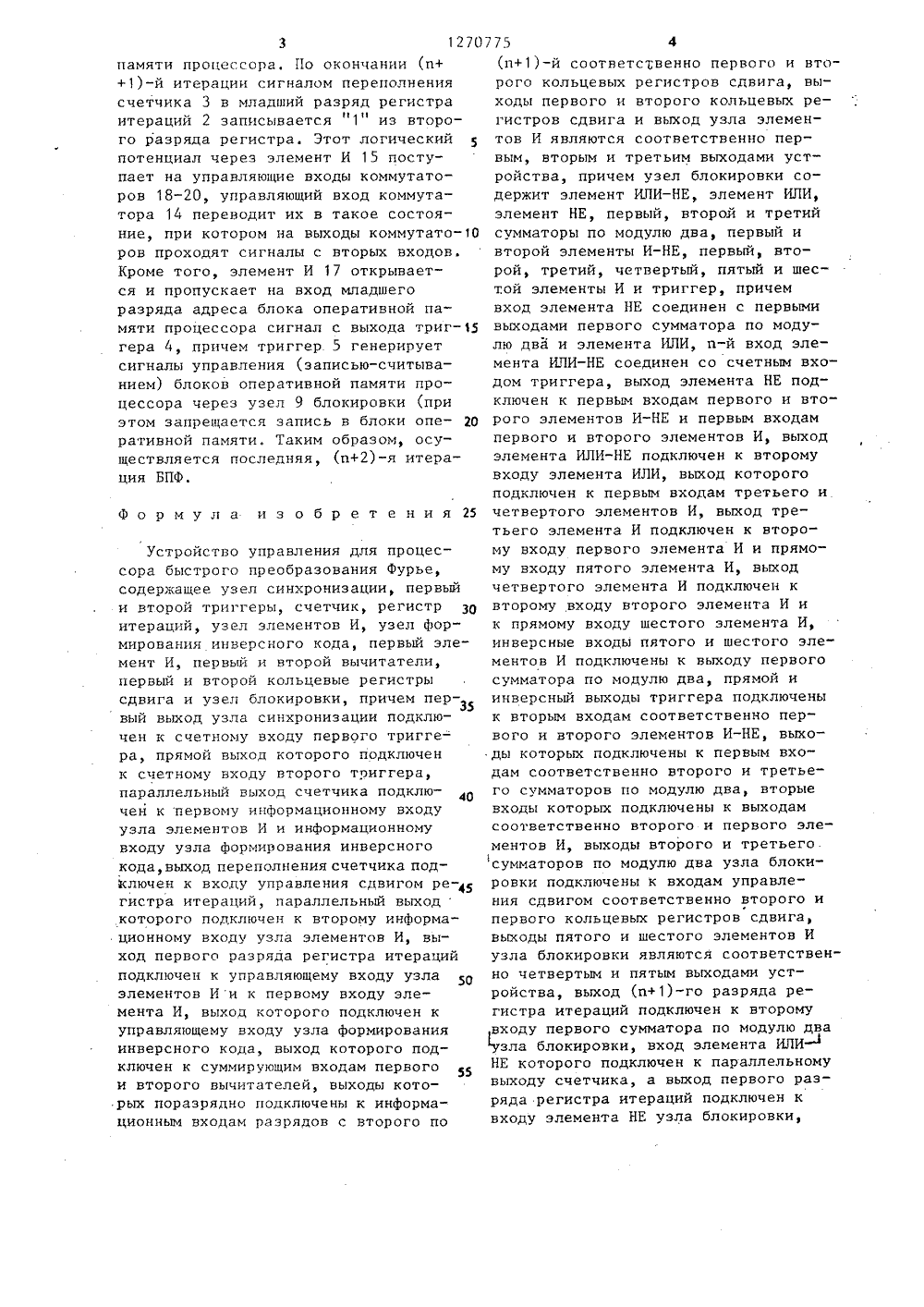

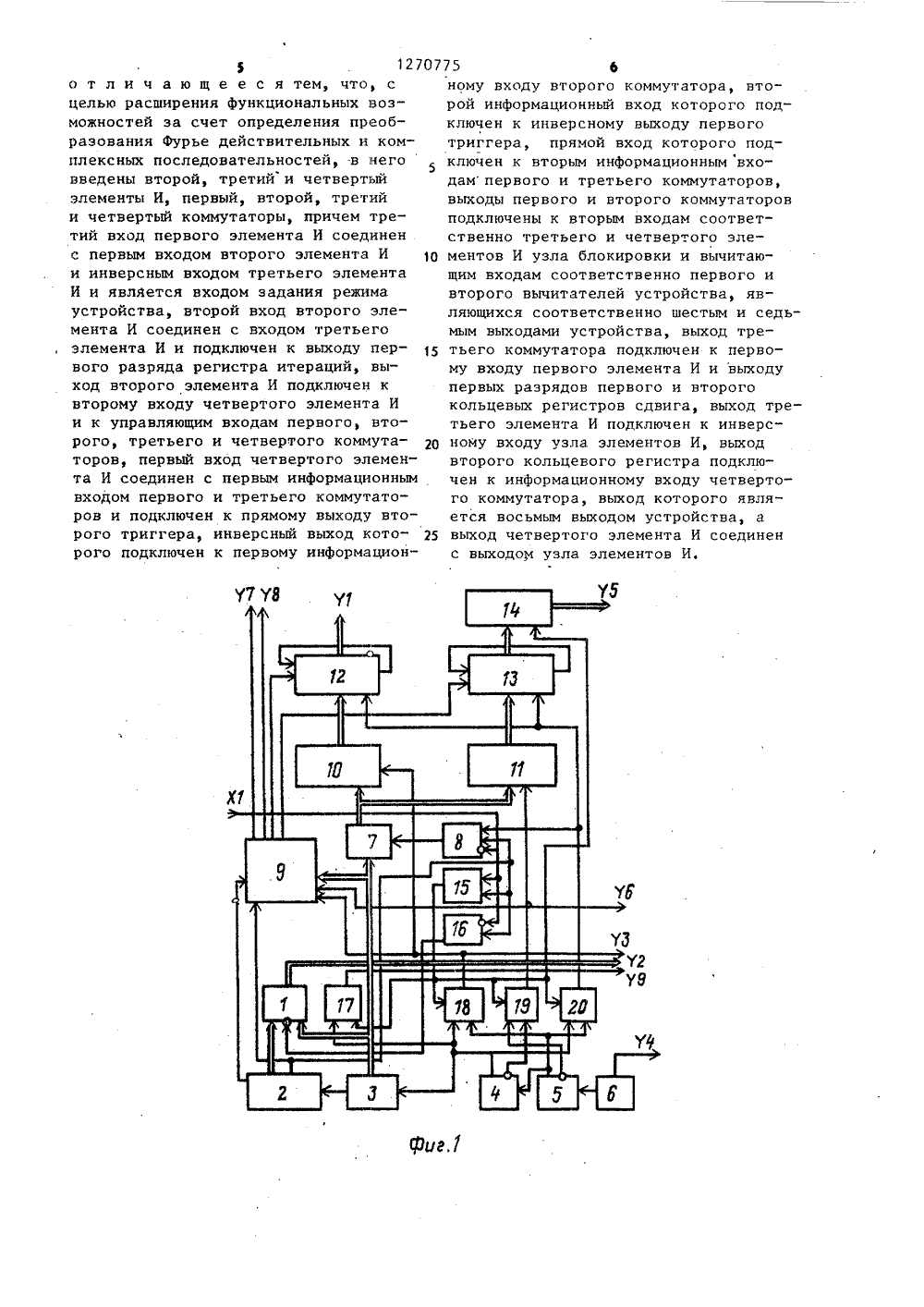

(51) 4 С 06 Р 15/3 ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(7 1) Специальное конструкторско- технологическое бюро с опытным производством при Белорусском государственном университете им. В.И.Ленина (72) А.Н.Карташевич и А.И.Ходосевич (53) 681.32(0888)(56) Рабинер Л Гоулд Б. Теория и применение цифровой обработки сигналов. М.: Мир, 1978.Авторское свидетельство СССР 9 1056206, кл. С 06 Р 15/332, И 82,(54) УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ,801270 и может быть использовано для решения задач спектрально-корреляционнойобработки последовательностей действительных и комплексных выборок. Целью изобретения является расширениефункциональных возможностей за счетвычисления преобразования Фурье действительных и комплексных последовательносрей. Устройство содержит узелэлементов И, регистр итераций, счетчик, два триггера, узел синхронизации, узел формирования инверсного кода, четыре элемента И, узел блокировки, два вычитателя, два кольцевыхрегистра сдвига и четыре коммутатора.Указанная совокупность признаков позволяет достигнуть цели изобретения.2 ил.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано для решения задачспектрально-корреляционной обра.боткипоследовательностей действительных икомплексных выборок.Целью изобретения является расширение функциональных возможностей засчет определения преобразования Фурьедействительных и комплексных последовательностей.На фиг. 1 представлена функпиональная схема предлагаемого устройстваупранленкя для процессора. быстрогопреобразования Фурье 1,БПФ) для действительных и комплексных массивовданных, на фкг. 2 -. схема узла блокировки.Устройство 1,тттг. 1) сопержит узелэлеглептов И 1, ретттстр 2 итераций, 20счетчик 3 триггеры 4 и 5, узел бсинхронизации, узел 7 формированияинверсного кода, элемент И 8,узел 9блокировки, вычитатели 10 и 11, кольцевые регистры 12 и 13 сгнттга, коммутатор 14. элементы И 15-17, коммутаторы 18-20,Уэен 9 блокировки (фиг, 2) содержит элементы И-НЕ 21 и 22, элементы И 23-28, сумматоры 29-31 пс модулю два, элемент Н 1, 32, элемент ИЛИ33, трт;ггер 34, э:темент ИЛИ - НЕ 35,Устрсйсттзо работает следующим образом.В случае обработки действительных последовательностей на вход И 1 поступает сигнал тО, открывающий элементы И 8 и 16 и закрывающий элемент И 1 о. На. выходе элемента И 15 устанавлива)е т ся ,пс гич е с кий потенциал 0 , кото О рык бдгтотсттруеэлеттетт 117 и уттранл)т - ет коммутаторами 8-20 так, что на их выходах гтоятзлгпотся сигналыттервых входов. В такое же состояние устанавливается и коммутатор 4, 45На прямых выходах триггеров 4 и 5 устанавливается потенциал 0 , а нат выход х р а з р ядо н счетчика 3) р а 2 итераций - также по т е нпиа г 0 Выхс)п трттггс ра 4 являюгся ныхсдамк 5 О устройства и определяют режим работы для блотссв оперативной памяти процессора ,"0" - считывание, т 11 - зались).Сс.рия тактогых импульсстз с первого выхоца узна 6 синхронизации гтоступает на счс.тный вход триггера 5 т формирует на выходах тразря)тстз счетчика 3 и прям)м выходе триггера 5 ттсхсдттйй двоичный код, преобразуемый нычитателями 10 и 11 и кольцевыми регистрами 12 и 13 .двига в адресный код обращения к блокам о:теративной памятипроцессора,На первом и пятом выходах устройства формируются коды адресов, а на третьем и шестом выходах - сигналыуправления записью - считыванием операндов для блоков оперативной памяти процессора. На втором выходе устройства формируются коды адресов экспоненциальньгх коэффициентов Х, считываемых из блока постоянной памяти процессора.В случае обработки одной комплексной последовательности цапных на вход И 1 процессора поступает сигнал который блокирует -.5 емсцты И 8 и 1 б и открывает элемен" И 15.Перные и+1 итераций вьтчттсзетия БПФ происходят аналогично случаю обработки 4 действительных массивов. При этом узел б синхронизации генерирует серию импульсов поступающих на тактовый вход триггера 5, на выходе которого, а также па выходах разрядного счетчика формируется исходный код адреса обращенкя к блокам оперативной памяти тпзоцессора. Данное адресное слово через узел 7 формирования инверсного кода поступает на входы элемента И 1 б нычитателей 10 и 11, преобразуется по сигналам уп.равления с прямого и инверсного вь)ходов триггера 4 и заносится в кольцевые регистры 12 и 13 сдвига, режимом работы которых упрагзляет узел 9 блокировки. Сигналы с входов разрядов кольцевого регистра 12 сдвига и через коммутатор 19 кольце)загс реги.тра 13 сдвига постуттантт на адресные входы блоков оперативной памяти процессора и задают порядок за.тиси и счт 7 ьтвания операндов. Признаком перехода к вычис.пению последующей итс.рации БПФ служит сигнал переполнения счетчика 3, поступающий на ".актоньтт вход (и+1)-разрядного регистра 2 терапий,по котторому происходит запись 1 в старший разряд регистра 2 итераций при сдтзиге хранимой инфсрмацкк в сторону младпкх рттз 1 зядсв, Ситпалы с нь ходов разрядов регистра. 2 итераций либо блокируют, либо разрешают прохождение исходного кода с вьгзодол разрядов счетчика 3 через узел этемеетов И 1 на а)тресный вход блска постоянной3 127(. памяти процессора. По окончании (п+ +1)-й итерации сигналом переполнения счетчика 3 в младший разряд регистра итераций 2 записывается "1" из второго разряда регистра. Этот логический потенциал через элемент И 15 поступает на управляющие входы коммутаторов 18-20, управляющий вход коммутатора 14 переводит их в такое состояние, при котором на выходы коммутатоО ров проходят сигналы с вторых входов. Кроме того, элемент И 17 открывается и пропускает на вход младшего разряда адреса блока оперативной памяти процессора сигнал с выхода триггера 4, причем триггер 5 генерирует сигналы управления (записью-считыванием) блоков оперативной памяти процессора через узел 9 блокировки (при этом запрещается запись в блоки опе ративной памяти. Таким образом, осуществляется последняя, (п+2)-я итерация БПФ. Формула изобретения 25 Устройство управления для процессора быстрого преобразования Фурье, содержащее узел синхронизации, первый и второй триггеры, счетчик, регистр ЗО итераций, узел элементов И, узел формирования инверсного кода, первый элемент И, первый и второй вычитатели, первый и второй кольцевые регистры сдвига и узел блокировки, причем первый выход узла синхронизации подключен к счетному входу первого тригге- ра, прямой выход которого подключен к счетному входу второго триггера, параллельный выход счетчика подклю чен к первому информационному входу узла элементов И и информационному входу узла формирования инверсного кода, выход переполнения счетчика подКлючен к входу управления сдвигом ре-гистра итераций, параллельный выходкоторого подключен к второму информационному входу узла элементов И, выход первого разряда регистра итерацийподключен к управляющему входу узлаэлементов Ии к первому входу элемента И, выход которого подключен куправляющему входу узла формированияинверсного кода, выход которого подключен к суммирующим входам первогои второго вычитателей, выходы которых поразрядно подключены к информационным входам разрядов с второго по 1775 4(и+1)-й соответственно первого и второго кольцевых регистров сдвига, выходы первого и второго кольцевых регистров сдвига и выход узла элементов И являются соответственно первым, вторым и третьим выходами устройства, причем узел блокировки содержит элемент ИЛИ-НЕ, элемент ИЛИ,элемент НЕ, первый, второй и третийсумматоры по модулю два, первый ивторой элементы И-НЕ, первый, второй, третий, четвертый, пятый и шестой элементы И и триггер, причемвход элемента НЕ соединен с первымивыходами первого сумматора по модулю два и элемента ИЛИ, и-й вход элемента ИЛИ-НЕ соединен со счетным входом триггера, выход элемента НЕ подключен к первым входам первого и второго элементов И-НЕ и первым входам первого и второго элементов И, выход элемента ИЛИ-НЕ подключен к второму входу элемента ИЛИ, выход которого подключен к первым входам третьего и четвертого элементов И, выход третьего элемента И подключен к второму входу первого элемента И и прямому входу пятого элемента И, выход четвертого элемента И подключен к второму входу второго элемента И и к прямому входу шестого элемента И, инверсные входы пятого и шестого элементов И подключены к выходу первого сумматора по модулю два, прямой и инверсный выходы триггера подключены к вторым входам соответственно первого и второго элементов И-НЕ, выходы которых подключены к первым входам соответственно второго и третьего сумматоров по модулю два, вторые входы которых подключены к выходам соответственно второго и первого элементов И, выходы второго и третьего. сумматоров по модулю два узла блокировки подключены к входам управления сдвигом соответственно второго и первого кольцевых регистров сдвига, выходы пятого и шестого элементов И узла блокировки являются соответственно четвертым и пятым выходами устройства, выход (и+ 1)-го разряда регистра итераций подключен к второму входу первого сумматора по модулю два узла блокировки, вход элемента ИЛИ НЕ которого подключен к параллельному выходу счетчика, а выход первого разряда регистра итераций подключен к входу элемента НЕ узла блокировки, 5 12707 о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет определения преобразования Фурье действительных и комплексных последовательностей, в него введены второй, третий и четвертый элементы И, первый, второй, третий и четвертый коммутаторы, причем третий вход первого элемента И соединен с первым входом второго элемента И 1 О и инверсным входом третьего элемента И и является входом задания режима устройства, второй вход второго элемента И соединен с входом третьего элемента И и подключен к выходу первого разряда регистра итераций, выход второго элемента И подключен к второму входу четвертого элемента И и к управляющим входам первого, второго, третьего и четвертого коммутаторов, первый вход четвертого элемента И соединен с первым информационным входом первого и третьего коммутаторов и подключен к прямому выходу второго триггера, инверсный выход кото- р 5 рого подключен к первому информацион 75ному входу второго коммутатора, второй информационный вход которого подключен к инверсному выходу первого триггера, прямой вход которого подключен к вторым информационным входампервого и третьего коммутаторов, выходы первого и второго коммутаторов подключены к вторым входам соответственно третьего и четвертого элементов И узла блокировки и вычитающим входам соответственно первого и второго вычитателей устройства, являющихся соответственно шестым и седьмым выходами устройства, выход третьего коммутатора подключен к первому входу первого элемента И и выходу первых разрядов первого и второго кольцевых регистров сдвига, выход третьего элемента И подключен к инверсному входу узла. элементов И, выход второго кольцевого регистра подключен к информационному входу четвертого коммутатора, выход которого является восьмым выходом устройства, а выход четвертого элемента И соединен с выходом узла элементов И.1270775 ФиаГ Составитель А,БарановРедактор Ю.Середа Техред Н.Глущенко Корректо мар Зака оизводственно-полиграфическое предприяти жгород, ул, Проектная, 4 6971 Тир ВНИИПИ Государстпо делам иэобр 113035, Москва,ж 671 Подписноеенного комитета СССРтений и открытий

СмотретьЗаявка

3685736, 05.01.1984

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО С ОПЫТНЫМ ПРОИЗВОДСТВОМ ПРИ БЕЛОРУССКОМ ГОСУДАРСТВЕННОМ УНИВЕРСИТЕТЕ ИМ. В. И. ЛЕНИНА

КАРТАШЕВИЧ АЛЕКСАНДР НИКОЛАЕВИЧ, ХОДОСЕВИЧ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, преобразования, процессора, фурье

Опубликовано: 15.11.1986

Код ссылки

<a href="https://patents.su/5-1270775-ustrojjstvo-upravleniya-dlya-processora-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления для процессора быстрого преобразования фурье</a>

Предыдущий патент: Устройство для выделения остатка по переменному модулю

Следующий патент: Функциональный аналого-цифровой преобразователь

Случайный патент: Ролик