Генератор векторов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1257698

Авторы: Куликов, Птаховский

Текст

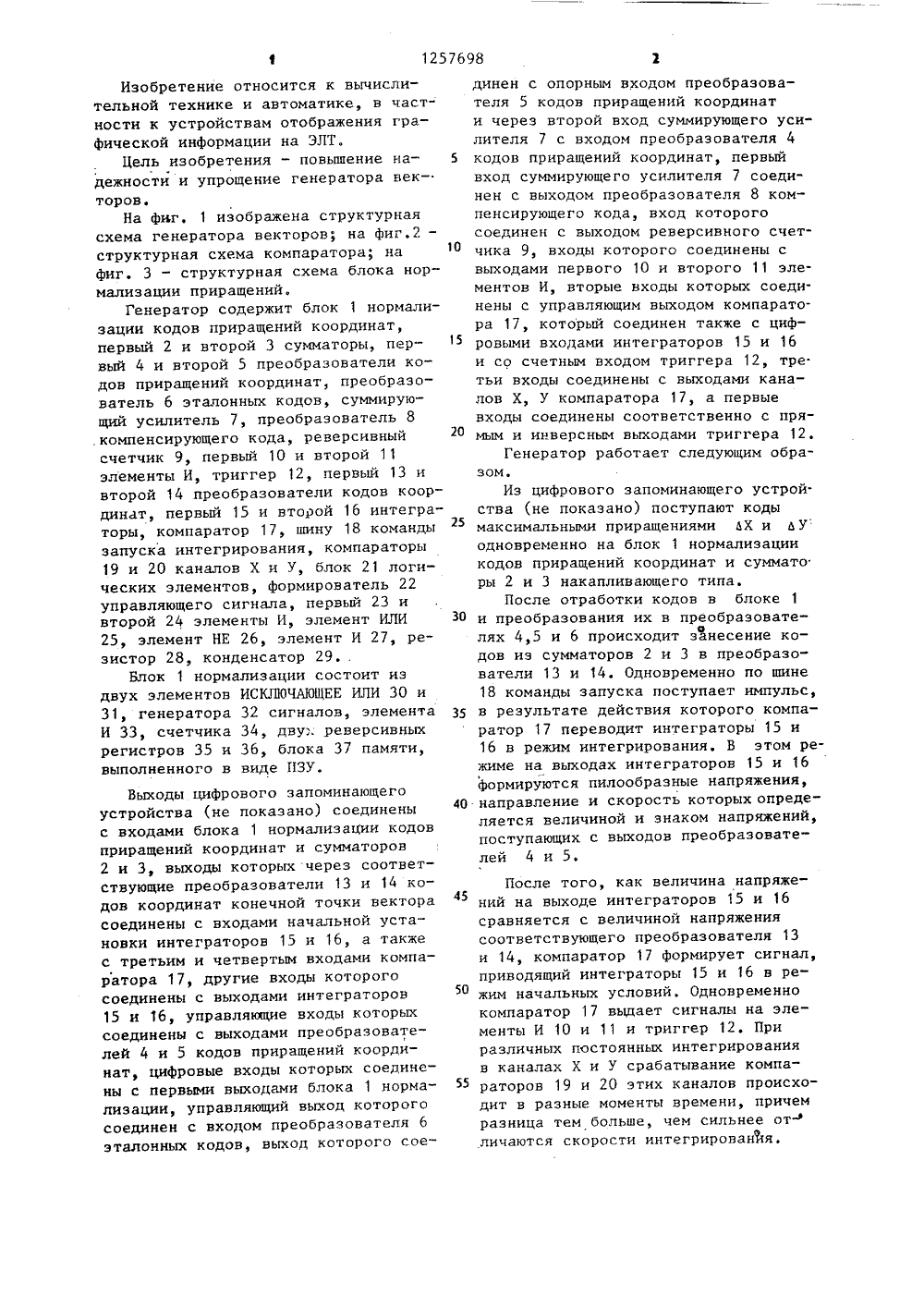

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 76 А 09 С 1/08 ЕНИЯ иисли. в частния граЦельюие нак норГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИЕ И ВТОРСКОМУ СВИДЕТЕ(56) Авторское свидетельство СССРУ 432543, кл. С 09 С 1/08, 1974.Авторское свидетельство СССРМф 1019483, кл. С 09 С 1/08, 1981.(57) Изобретение относится к вьтельной технике и автоматике,ности к устройствам отображефической информации на ЭЛТ.изобретения является повышендежности и упрощение генератора второв, Генератор содержит бло мализации кодов приращений координат,два сумматора, два преобразователякодов приращений координат, преобразователь эталонных кодов, суммирую"щий усилитель, преобразователь компенсирующего кода, реверсивный счетчик, два элемента И, триггер, двапреобразователя кодов координат,дваинтегратора и компаратор. В генерато.ре векторов разница в постоянных времени интегрирования в каналах Х и Уопределяется с помощью интегратораи триггера, а устраняется с помощьюдвух элементов И, реверсивного счетчика, преобразователя компенсирующего кода и суммирующего усилителя.3 илИзобретение относится к вычислительной технике и автоматике, в частности к устройствам отображения графической информации на ЭЛТ.Цель изобретения - повышение надежности и упрощение генератора векторов.На фиг. 1 изображена структурнаясхема генератора векторов; на Фиг.2 -структурная схема компаратора; нафиг. 3 - структурная схема блока нормализации приращений,Генератор содержит блок 1 нормализации кодов приращений координат,первый 2 и второй 3 сумматоры, первый 4 и второй 5 преобразователи кодов приращений координат, преобразователь 6 эталонных кодов, суммирующий усилитель 7, преобразователь 8компенсирующего кода, реверсивныйсчетчик 9, первый 10 и второй 11элементы И, триггер 12, первый 13 ивторой 14 преобразователи кодов координат, первый 15 и второй 16 интеграторы, компаратор 17, шину 18 командызапуска интегрирования, компараторы19 и 20 каналов Х и У, блок 21 логических элементов, формирователь 22управляющего сигнала, первый 23 ивторой 24 элементы И, элемент ИЛИ25, элемент НЕ 26, элемент И 27, резистор 28, конденсатор 29.,Блок 1 нормализации состоит издвух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 30 и31, генератора 32 сигналов, элементаИ 33, счетчика 34, дву:, реверсивныхрегистров 35 и 36, блока 37 памяти,выполненного в виде ПЗУ.Выходы цифрового запоминающего устройства (не показано) соединены с входами блока 1 нормализации кодов приращений координат и сумматоров 2 и 3, выходы которых через соответствующие преобразователи 13 и 14 кодов координат конечной точки вектора соединены с входами начальной установки интеграторов 15 и 16, а также с третьим и четвертым входами компаратора 17, другие входы которого соединены с выходами интеграторов 15 и 16, управляющие входы которых соединены с выходами преобразователей 4 и 5 кодов приращений координат, цифровые входы которых соединены с первыми выходами блока 1 нормализации, управляющий выход которого соединен с входом преобразователя 6 эталонных кодов, выход которого сое 5 1 О 15 20 25 30 динен с опорным входом преобразователя 5 кодов приращений координат и через второй вход суммирующего усилителя 7 с входом преобразователя 4 кодов приращений координат, первый вход суммирующего усилителя 7 соединен с выходом преобразователя 8 компенсирующего кода, вход которого соединен с выходом реверсивного счетчика 9, входы которого соединены с выходами первого 10 и второго 11 элементов И, вторые входы которых соединены с управляющим выходом компарато. ра 17, который соединен также с цифровыми входами интеграторов 15 и 16 и со счетным входом триггера 12, тре тьи входы соединены с выходами каналов Х, У компаратора 17, а первые входы соединены соответственно с прямым и инверсным выходами триггера 12.Генератор работает следующим образом.Из цифрового запоминающего устрой. ства (не показано) поступают коды максимальными приращениями ЬХ и ЬУ одновременно на блок 1 нормализации кодов приращений координат и суммато ры 2 и 3 накапливающего типа,После отработки кодов в блоке 1и преобразования их в преобразователях 4,5 и 6 происходит занесение коОдов из сумматоров 2 и 3 в преобразователи 13 и 14. Одновременно по шине 18 команды запуска поступает импульс, в результате действия которого компаратор 17 переводит интеграторы 15 и 16 в режим интегрирования. В этом режиме на выходах интеграторов 15 и 16 формируются пилообразные напряжения,ляется величиной и знаком напряжений, поступающих с выходов преобразователей 4 и 5,После того, как величина напряжений на выходе интеграторов 15 и 16 сравняется с величиной напряжения соответствующего преобразователя 13 и 14, компаратор 17 формирует сигнал, приводящий интеграторы 15 и 16 в режим начальных условий. Одновременно компаратор 17 выдает сигналы на элементы И 10 и 11 и триггер 12, При различных постоянных интегрирования в каналах Х и У срабатывание компараторов 19 и 20 этих каналов происходит в разные моменты времени, причем разница тем больше, чем сильнее от-ф личаются скорости интегрирования,45 5055 40 направление и скорость которых опреде 1257698Это вызывает появление ошибки на стыках векторовВ начале процесса коррекции скорости интегрирования осуществляется перевод интеграторов 15 и 16 в режим 5 начальных условий по сигналу компаратора 19 канала Х, При этом анализируется состояние компаратора 20 канала У на его выходе У. Затем наоборот остановка режима интегрирования и пере-О вод интеграторов 15 и 16 в режим задания начальных условий производится по сигналу компаратора 20 канала У. При этом анализируется состояние компаратора 19 канала Х на его выходе Х. Триггер 12 работает в счетном режиме, осуществляя переключения элементов И 1 О и 11. В качестве счетных импульсов используются сигналы, поступающие с выхода компаратора 17, В первый такт шага коррекции открыт элемент И 11 и закрыт элемент И 10, во второй такт наоборот открыт элемент И 10 и закрыт элемент И 11.Если скорость интегрирования в канале Х вьппе, чем в канале У, то к тому времени, когда сработает и выдаст нулевой логический сигнал ком,паратор 19 канала Х, высокий уровень сигнала на выходе компаратора 20 ка нала У будет показывать наличие рассогласования или ошибку.При этом через открытый элемент И 11 проходит сигнал компаратора 17 и вызывает соответствующее изменение З 5 кода на выходе реверсивного счетчика 9. Изменившееся состояние кода на выходе реверсивного счетчика 9 вызывает изменение напряжения на выходе преобразователя Ь и соответственно 40 на выходе суммирующего усилителя 7, подключенного к опорному входу преобразователя 4 кодов приращений координат канала Х, что приводит к уменьшению уровня напряжения на вхо де интегратора 15 и к уменьшению скорости интегрирования канала Х, Если скорость интегрирования в канале У выше, чем в канале Х, то сигнал компаратора 17 будет проходить через открытый элемент И 10, вызывая изменение кода на выходе реверсивного счетчика 9, приводящее к увеличению уровня напряжения на входе интегратора 15 и к увеличению скорости интегрирования канала Х.Описанный двухтактный режим работы узла коррекции скорости интегрирования оказывается возможным благодаря медленному изменению этой скорости под воздействием внешних климатических факторов.Точность узла коррекции определяется только чувствительностью компаратора 17 и не зависит от другихэлементов схемы, В генераторе автоматическая коррекция скорости интегрирования канала может производитьсяпериодически в начале кадра регенерации,Если скорости интегрирования вканалах Х и У увеличены, то включает-ся схема коррекции.1,Переход на двухтактный режим коррекции позволяет отказаться от рядаэлементов прототипа, что упрощаетсхему и повышает надежность.,Формула изобретенияГенератор векторов, содержащий блок нормализации кодов приращений координат, первый и второй входы ко-. торого являются соответственно первым и вторым входами устройства, которые соединены соответственно с вхо дами первого и второго сумматоров, первый и второй выходы блока нормализации кодов приращений координат подключены к первым входам соответст венно первого и второго преобразователей кодов приращений координат, .третий выход блока нормализации кодов приращений координат подключен к входу преобразователя эталонных ко. дов, выход которого подключен к второму входу второго преобразователя кодов приращений координат и к первому входу суммирующего усилителя, выход которого подключен к второму входу первого преобразователя кодов приращений координат, второй вход суммирующего усилителя подключен к выходу преобразователя компенсирующего кода, вход которого подключен к выходу реверсивного счетчика, первый и второй входы которого подключены к выходам соответственно первого и вто. рого элементов И, первый вход первого элемента И подключен к первому выходу триггера, выходы первого и второго сумматоров подключены соответственно через первый и второй преобразователи кодов координат к первым входам соответственно первого и второго интеграторов, вторыевходы которых подключены к выходамсоответственно первого и второгопреобразователей кодов приращенийкоординат, третьи входы первого ивторого интеграторов подключены кпервому выходу компаратора, выходпервого интегратора является первымвыходом генератора, соединенным спервым входом компаратора, второйвход которого подключен к выходувторого интегратора, который является вторым выходом генератора,третий и четвертый входы компаратораподключены к выходам соответственно первого и второго преобразователей кодов координат, пятый вход компаратора является третьим входом генератора, о т л и ч а ю щ и й с я тем, что, с целью повышения надежности и упрощения генератора, первый выход компаратора подключен к входу триггера и к вторым входам первого и второго элементов И, второй выход триг гера подключен к первому входу второго элемента И, второй и третий выходы компаратора подключены к третьим входам соответственно первого и второго элементов И.125698Составитель Л.Абросимов Редактор Е,Копча Техред Л.Олейник КорректорВ.Синицкая Заказ 4963/50 Тираж 455 Подписное ВНИИПИ Государственного комитета СССР .по делам изобретений и открытий113035, Москва, Ж, Раушская наб., д.4/5 Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4

СмотретьЗаявка

3845067, 19.12.1984

ПРЕДПРИЯТИЕ ПЯ В-2672

ПТАХОВСКИЙ ИГОРЬ ГАВРИЛОВИЧ, КУЛИКОВ ГЕОРГИЙ ПАВЛОВИЧ

МПК / Метки

МПК: G09G 1/08

Опубликовано: 15.09.1986

Код ссылки

<a href="https://patents.su/5-1257698-generator-vektorov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор векторов</a>

Предыдущий патент: Информационное табло

Следующий патент: Органная приставка

Случайный патент: Способ хранения корнеклубнеплодов в буртах