Компаратор формы сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

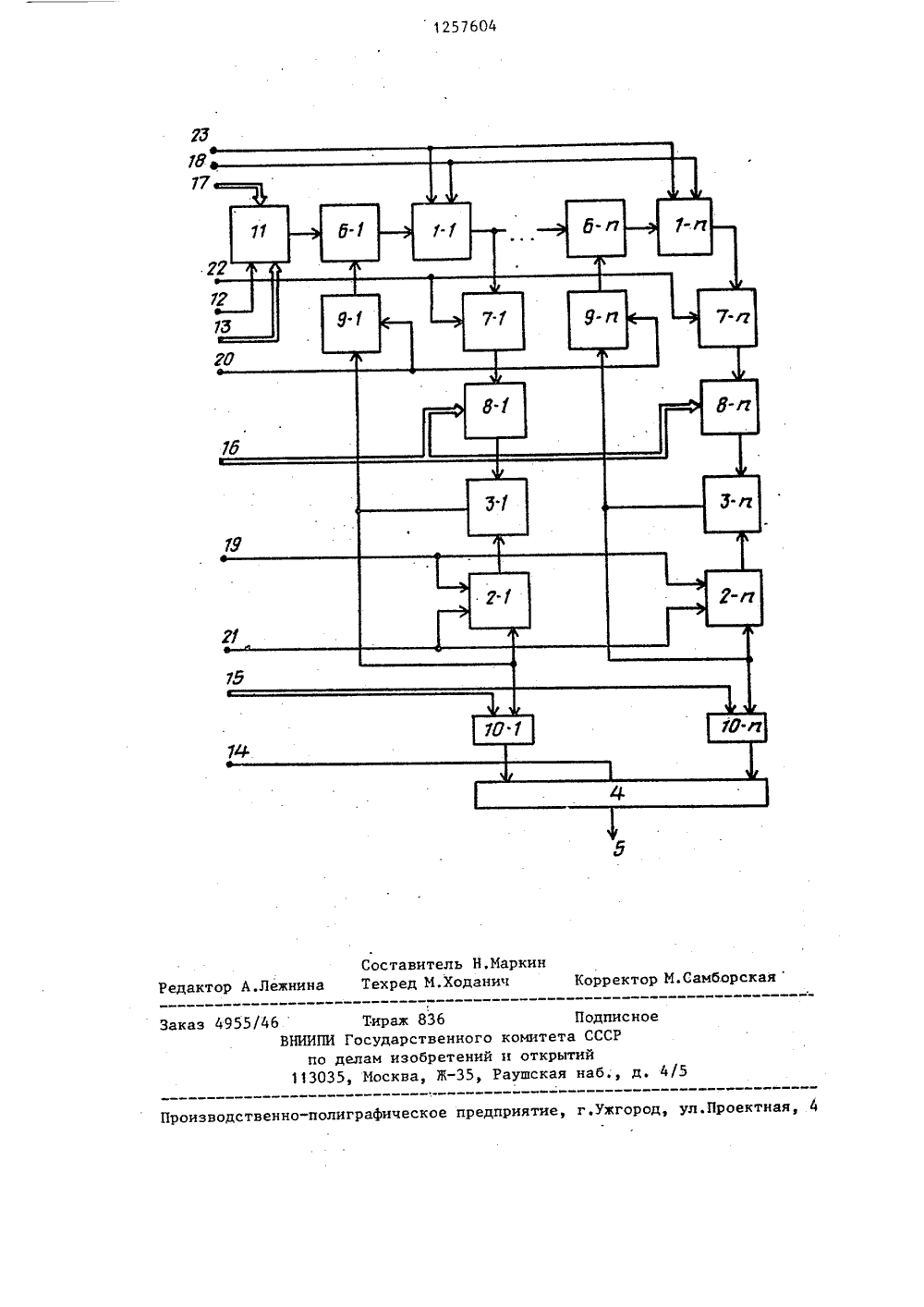

(59 4 С 4 5/2 01 Н 03 ЕННЫЙ КОМИТЕТ СССРЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОСУДА ПО ДЕЛ ОБРЕТЕНИЯЛЬСТВУ К АВТОРСКОМУ(56) Макаров Р.А, Средства технической диагностики машин. М,: Наука, 1981, с. 1.25-126.Авторское свидетельство СССР У 111521, кл. Н 03 К 5/22, 04,01.82. (54) КОМПАРАТОР ФОРМЫ СИГНАЛОВ (57) Изобретение относится к измерительной технике и может быть использовано, в частности, при контроле микросхем по форме переходного процесса динамического тока потребления. Цель изобретения - повышение точности сравнения формы сигналов и расширение ПИСАНИЕ ИЗ(46) 15,09,86, Бюл . Ке 34 (72) И,В.Дягель, А,Г.Рыжевс и Д,ВеШабалов 801257604 А 1 области применения. Устройство содержит группы интеграторов, элемент И,элементы сравнения, сумматоры, ана"логовые запоминающие элементы, усилители, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ,коммутатор и шины исследуемого и эталонного сигналов. Наличие шины разрешения сравнения, шины программирования результата сравнения, шины программирования чувствительности, шинывыбора режима работы, шины разреше.ния интегрирования входных сигналов,шины .компенсации мультипликативнойпогрешности, шины слежения-запоминания формы сигнала с компенсацией ади"ативной погрешности, шины начальнойустановки, шины запоминания интегральных значений и шины подготовкии интегрированию и соединение ин с Сш,элементами устройства компенсируетпогрешности и расширяет динамический Бдиапазон сравниваемых, сигналов засчет дифференциального сравненияформ сигналов. 1 ил,СлИзобретение относится к измери-. тельной технике и может быть использовано в радиоэлектронных системах обработки и анализа формы сигналов, в частности при контроле микросхем по форме переходного процесса динамического тока потребления,Целью изобретения является повышение, точности сравнения формы сигналов за счет компенсации погрешностей и расширение области применения путем расширения динамического диапазона сравниваемых сигналов за счет дифференциального сравнения форм ,сигналов.На чертеже приведена структурная схема компаратора формы сигналов.Компаратор формы сигналов содержит и интеграторов первой группы 1-1.1-п, и интеграторов второй группы 2-1. 2-п, и элементов сравнения 3-1. З-п, элемент И 4, вы" 1 ход которого является выходом 5 устройства, выход каждого п-го интегратора второй группы 2-и подключен к первому входу и-го элемента сравне- . ния З-п, сумматоры 6-16-п, аналоговые запоминающие элементы 7-1,7-п, усилители с программируемым коэффициентом усиления 8-1 Я-п, интеграторы третьей группы 9-1, ,9-п, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10-1,.10-п, коммутатор 11, входы которого подключены к шинам исследуемого 12 и эталонных 13 сигналов, а выход подключен к первому входу первого сумматора 6-1 цепи последовательно-поочередно соединенных сумматоров 6-1. ,6-и и интеграторов первой группы 1-11-п, при этом выход каждого и-го интегратора первой группы 1-п через последовательно соединенные и-й аналоговый запоминающий элемент 7-и и и-й усилитель с программируемым коэффициентом усиления 8-и подсоединен к второму входу и-го элемента сравнения З-п, а выход и-го элемента сравнения 3-и подклю"; чен к первому входу и-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10-и и информационным входам и-х интеграторов второй 2-и и третьей 9-и групп, причем выход и-го интегратора третьей группы 9-и подсоединен к второму входу и-го сумматора 6-п, а выходы всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10-1 10-и подключены к входам элемента И 4, дополнительный вход которого подсоеди", с шиной 20 слежения-запоминания формы сигнала с компенсацией аддитивной 25 35 40 45 50 55 нен к шине 14 разрешения сравнения,вторые входы элементов ИСКЛЮЧАЮЩЕЕИЛИ 10-1 10-п подключены к шинам 15 программирования результата сравнения, управляющие входы усилителейс программируемым коэффициентом уси-:ления 8-1,,8-и соединены с шинами 16 программирования чувствительности, управляющие входы коммутатора 11 подключены к шинам 17 выбора режима работы, входы разрешения интегрирования интеграторов первой группы 1-1, , 1-и соединены с шиной 18 разрешения интегрирования входных сигналов, входы разрешения интегрирования интеграторов второй группы 2-2, ,2-и - с шиной 19 компенсации мультипликативной погрешности, а входы разрешения интегрирования интеграторов третьей группы 9-1. 9-и -погрешности, входы сброса интеграторов второй группы 2-1 2-и подключены к шине 21 начальной установки, управляющие входы аналоговых запоминающих элементов 7-1.7-и соединены е шиной 22 запоминания интегральных значений, входысброса интеграторов первой группы1-11-п подключены к шине 23 подготовки к интегрированию. Компаратор Формы сигналов работает следующим образом.Для запоминания формь эталонного сигнала на шины 17 выбора режима работы подается комбинация управляющих сигналов, обеспечивающая подключение через коммутатор 11 к цепи последовательно соединенных сумматоров и первых интеграторов соответственно 6-16-п и 1-11-п эталонного сигнала Г с шины 13. На шину 20 слежения запоминания формы сигнала подается сигнал управления, соответствующий слежению, т.е. сигнал разрешения интегрирования интеграторами третьей группы 9-1-9-п разности интегральных значений на выходах первых интеграторов и нулевого уровня сигнала, обеспечиваемого сбросом интеграторов второй группы 2-1 2-и при подаче на шину 21 сигнала, соответствующего начальной установке устройстваПроцесс слежения осуществляется за определенное количество циклов интегрирования эталонного входного сигнала Г до тех пор, 1257604пока на выходах интеграторов первойгруппы 1-1, ,1-и не установятсянулевые значения. При этом на выходах интеграторов третьей группы 9-1;,9-и образуются средние за время 5интегрирования интегральные значенияс обратным знаком, которые соответствуют средним интегральным значениям эталонного сигнала с учетомаддитивной погрешности всего трактапреобразования и сравнения. Каждыйцикл интегрирования обеспечиваетсявыполнением последовательно следующих операций: сброса интеграторовпервой группы 1-1 ., 1-и по шине 23 15подготовки к интегрированию; интегрирования при подаче сигнала по шине18 разрешения интегрирования входных сигналов; запоминания интегральных значений с их переписью в аналоговые запоминающие элементы 7-17-и при подаче соответствующего сигнала по шине 22 устройства на их управляющие входы с последующим переходом из режима выборки в режим хранения,Процесс слежения заканчивается подачей на шину 20 в определенный момент времени сигнала, соответствую 30 , щего переходу интеграторов третьейгруппы 9-19-и в режим запомина,ния. Компенсация нестабильности коэффициентов преобразования, зависящей, в основном, от нестабильности интеграторов первой группы 1-1,,1-и, 35 осуществляется регулировкой уровней уставок, значения которых задаются интеграторами второй группы 2-1 2-и. При подаче на входы 17 выбора режима работы устройства комбинации 40 сигналов, обеспечивающей подключение через коммутатор 11 эталонного сигнала Г + ЬЙ, после каждого цикла интегрирования на выходах интеграторов первой группы 1-1 1-и образуются 45 интегральные значения, соответствующие сигналу Ь Г, Подачей управляющих сигналов на шины 16 программирования чувствительности осуществляется задание определенных уровней уставок, которые отслеживаются интеграторами второй группы 2-1,2-и, на входы разрешения интегрирования которых по шине 19 компенсации мультипликативной погрешности подается соответ ствующий уровень сигнала. При этом сигнал на шине 21 начальной установки снимается. В определенный момент времени установки ьса выходах интеграторов второй группы 2-12-итребуемых значений уставок снимаетсясигнал на шине 19 устройства и интеграторы второй группы 2-1. ,2-ипереходят в рехссщ запоминания. Такимобразом, устройство подготовлено ксравнению формы эталонного сигналаи исследуемого Г, так как на интеграторах третьей группы 9-19-и запомнены значения, соответствующие средним интегральным значениямэталонного сигнала с обратным знакомс учетом аддитивной составляющей погрешности, а на интеграторах второйгруппы 2-12-и - уровни установоксравнения с учетом мультипликативнойсоставляющей погрешности такта преобразования. При подаче на шины 17 выбора режима работы устройства комбинации сигналов, обеспечивающей подключение через коммутатор 11 исследуемого сигнала Г, после первогоцикла интегрирования на выходах интеграторов первой группы 1-11-и образуются интегральные значения,соответстьующие раэностному сигналуй-Г. Подачей на шины 16 программирования чувствительности наперед заданной комбинации сигналов осуществляется масштабирование ожидаемогоотличия формы сигнала по отношению ксигналу 6 Г. В зависимости от логикиработы последующих устройств можетбыть интересным не только результатсовпадения формы сигналов, но и ихопределенные отличия, что обеспечивается заданием соответствующих сигналов йо вторым входам элементов ИСКЛЮ 1 АЮЩЕЕ ИЛИ 10-110-и. С учетомзадерясек, вносимых элементами устройства, с появлением установившегосярезультата сравнения на вход 14 разрешения сравнения подается управляющий сигнал, обеспечивающий выдачурезультата сравнения,Таким образом, за счет идентичности трактов преобразования эталонно. ои исследуемого сигналов обеспечивается возможность компенсации погрешностей и расширения динамическогодиапазона преобразования разностного .сигнала.формула изобретенияКомпаратор формы сигналов., содержащий шины входного и исследуемого3 1257604 6сигналов, и интеграторов пеРвой груп- динен к второму входу и-го элемента 1 пы, и интеграторов второй группы, сравнения, а выход и-го элемента и элементов сравнения, элемент И, сравнения подсоединен к первому вховыход которого является выходом уст- ду п-го элемента ИСКЛЮЧАЮ 1 ЕЕ ИЛИ и ройства, выход каждого и-го интегра информационным входам п интеграторов тора второй группы подсоединен к пер- второй и третьей групп, причем выход вому входу и-го элемента сравнения, п-го интегратора третьей группы подо т л и ч а ю щ и й с я тем, что с соединен к второму входу и-го сумма- целью повышения точности сравнения и тора, а выходы всех элементов ИСКЛЮ- расширения области применения за 10 ЧАЮЩЕЕ ИЛИ подсоединены к соответсчет увеличения динамического диапа- ствующим входам элемента И, доползона сравниваемых сигналов, в него нительный вход которого подсоединен дополнительно введены шина разреше- к шине разрешения сравнения. вторые ния сравнения, шины программирования входы элементов ИСКПЮЧА 0 ЩЕЕ ИЛИ подрезультата сравнения, шины программи соединены к шинам программирования рования чувствительности, шины выбо- результата сравнения, управляющие ра режима работы, шина разрешения входы усилителей с программируемым интегрирования, шина компенсации коэффициентом усиления соединены с мультипликативной погрешности, шина шинами программирования чувствительслежения-запоминания формы сигнала 20 ности, управляющие входы коммутатора с компенсацией аддитивной погрешнос- подключены к шинам выбора режима рати, шина начальной установки, шина боты, входы разрешения интегрировазапоминания интегральных значений, ния интеграторов первой группы соешина подготовки к интегрированию, динены с шиной разрешения интегриросоответственно п сумматоров, и ана вания входных сигналов, входы разрелоговых запоминающих элементов, и шения интегрирования интеграторов усилителей с программируемым коэффи- второй группы - с шиной компенсации циентом,усиления, п интеграторов мультипликативной погрешности, а третьей группы, п элементов ИСКЧЮЧА- входы разрешения интед рирования ин цЕЕ ИЛИ, коммутатор, входы которого З 0 теграторов третьей группы - с шиной подключены к шинам исследуемого и слежения-запоминания формы сигнала эталониых сигналов, а выход подсое- с компенсацией аддитивной погрешносдинен к первому входу первого сумма- ти, входы сброса интеграторов второй тора цепи последовательно-поочередно группы подсоединены к шине начальной соединенных и сумматоров и и интег- З 5 установки, управляющие входы аналогораторов первой группы, при этом вы- вых запоминающих элементов соединены ход каждого и-го интегратора первой с шиной запоминания интегральных знагруппы через последовательно соеди- чений, входы сброса интеграненные п-й аналоговый запоминающий торов первой группы подсоедиэлемент и и-й усилитель с программи пены к шине подготовки к инруемым коэффициентом усиления подсое тегрированию.1257604 Составитель Н,МаркиТехред М,Ходанич ректор И.СамборскаяРедактор А.Лежнина аказ 495 Подписноеа СССР иинаб., д. 4( Производственно-полиграфическое предприятие, г.ужгород роект О 78 17 Тираж 836 НИИПИ Государственного комнт по делам изобретений и отк 13035, Москва, Ж, Раушск

СмотретьЗаявка

3853689, 08.02.1985

ВСЕСОЮЗНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ОРГАНИЗАЦИОННОЙ ТЕХНИКИ, НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "АВТОГРАФ"

ДЯГЕЛЬ ИГОРЬ ВЛАДИМИРОВИЧ, РЫЖЕВСКИЙ АЛЕКСЕЙ ГОРДЕЕВИЧ, ШАБАЛОВ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G05B 1/01, H03K 5/22, H03K 5/24

Метки: компаратор, сигналов, формы

Опубликовано: 15.09.1986

Код ссылки

<a href="https://patents.su/5-1257604-komparator-formy-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Компаратор формы сигналов</a>

Предыдущий патент: Устройство для определения момента формирования стандартного импульса

Следующий патент: Нелинейное корректирующее устройство

Случайный патент: Рабочий орган смесителя