Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1239863

Авторы: Заболотских, Мешков, Штин

Текст

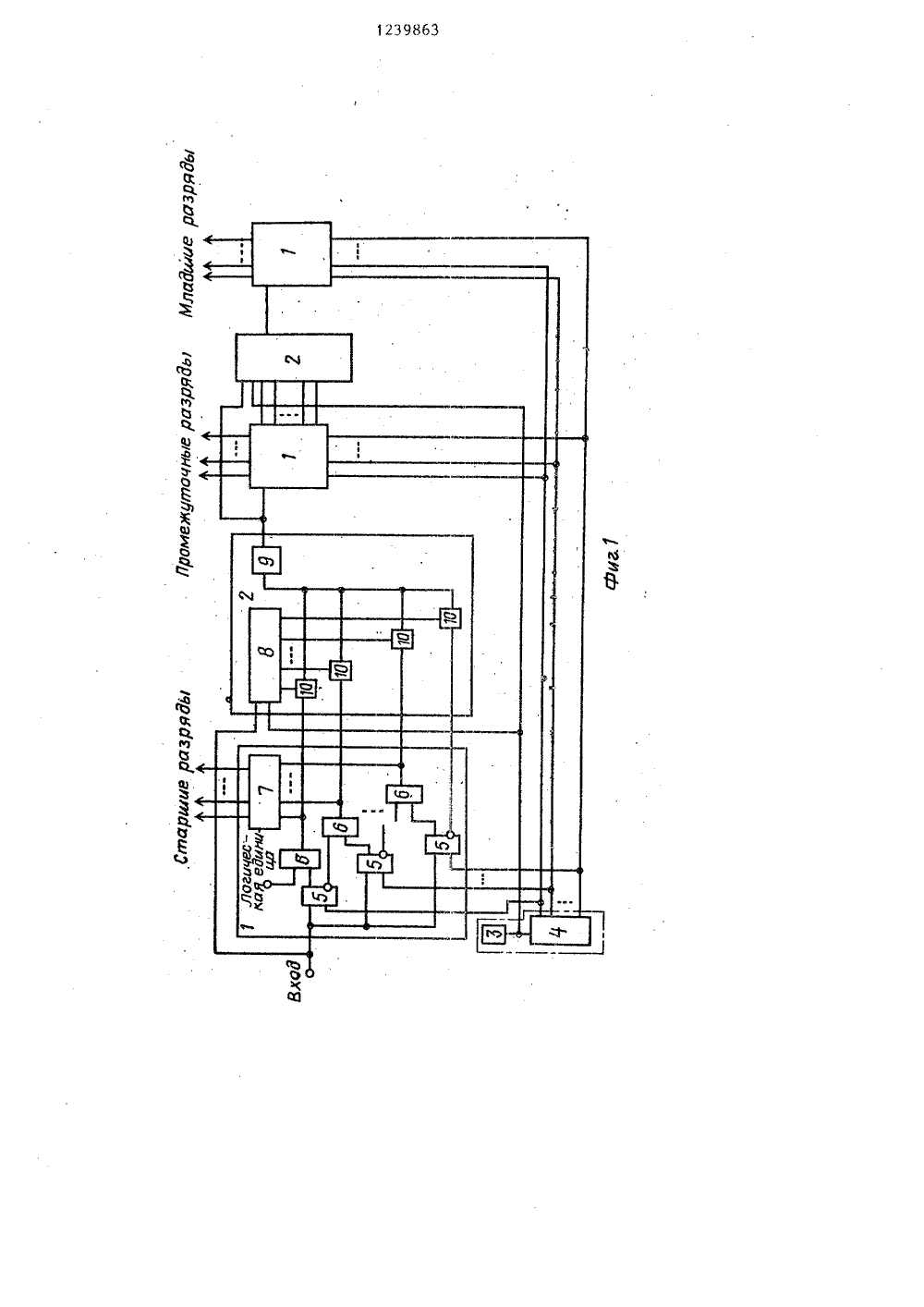

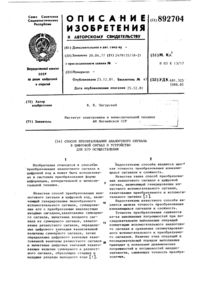

(19) (11) 51) 4 Н 03 М 1/14 ГОСУД АРСПО ДЕЛ ВЕННЫЙ КОМИТЕТ ССС ИЗОБРЕТЕНИЙ И ОТКРЫ ВСЕ(О(1.3. Я13,; .,1 ВИЬЛИОТЫА ПИСАНИЕ ИЗОБРЕТЕНИЯ ТЕЛЬСТВ Н АВТОРСКОМ 23 М.Мешков(54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к вычислительной технике и может быть использовано в быстродействующих аналогоцифровых вычислительных устройствах, Изобретение позволяет повысить быстродействие устройства. Это достигается за счет того, что в устройство, содержащее последовательно соединенные блоки преобразования, содержащие блок аналого-цифрового преобразования, блок цифроаналогового преобразования, источник пороговых напряжений, выполненный на источнике опорного напряжения, делителе напряжения, блок цифроаналогового преобразования.содержит (п+1) ключей, усилитель разностного сигнала, элемент И и вычитающий усилитель. Быстродействие достигается за счет того, что получение разностного сигнала в блоке цифроанас логового преобразования происходит Ж параллельно с получением кода в аналого-цифровом преобразователе. 1 з ф 2 С:1 12Изобретение относится к вычислительной технике и мОжет быть использовано в быстродействующих аналого цифровых вычислительных устройствахи устройствах контрольно-измерительной техники.Цель изобретения - повышение быстродействия,На фиг.1 приведена функциональнаясхема параллельно-последовательногоаналого-цифрового преобразователя.На фиг.2 - принципиальная электрическая схема цычитающего усилителя.Преобразователь содержит блок 1аналого-цифрового преобразования(аналго - цифровые преобразователи),блоки 2 цифроаналогового преобразования., источник 3 опорного напряжения,делитель 4 напряжения. Аналого-цифровой преобразователь 1 содержит и-компараторов 5 и и-элементов Иб, формирователь 7 выхоцного кода, источник3 и делитель 4 образуют источник пороговых напряжений,блок 2 содержит вычитающий усилитель 8, усилитель 9 разностного сигнала (и+1) ключей 10. Вычитающий уси;литель 8 содержит операционный усилитель 11, резистивный делитель 12 на, пряжения, содержащий (в+1) последовательно соединенных одинаковых резисторов 13, резисторы 14-17. Блоки 1 и2 образуют блоки преобразования. Устройство работает, следующим образом,39863его в старшие разряды выходного двоичного кода.Одновременно с преобразованием аналога в параллельном АЦП 1 вычитающийусилитель 8 формирует (и+1) разностный сигнал, а позиционный код с выхода элементов 6 подается на управляющие входы ключей 10, вызывая срабатывание одного из них. В результате на 1 О вход усилителя 9 подается напряжениеЦ, равное разности между напряжениемвходного сигнала и ближайшим меньшимзначением опорного напряжения. Усилитель 9 усиливает разностный сигнал и 15 подает его на следующий блок преобразования.Напряжение на выходе резистивногогде 1 = 1, 2, , и+1при условии, что к прямому и инверсному входам операционного усилителя 25 подключены по два одинаковых по величине резистораТаким образом, вычитающий усилитель 8 при подаче на его соответствующие входы преобразуемого и опорного ЗО напряжений формирует на выходах (и+1)разностное напряжение, равное разностям между П и величинами напряжений,снимаемых с делителя 4, причем на входусилителя 9 подается разность междувходным напряжением и ближайшим меньшим по величине уровнем опорного на Напряжение входного сигнала, подлежащего преобразованию, подается одновременно на первые входы компараторов 5 и на соответствующий вход вычитаю- щего усилителя Я первого блока преобразования. Ка вторые входы компараторов э подаются соответствующие уровни опорых напряжений с делителя 4, а на соответствующий первый вход вычитаю. щега усилителя 8 подается опорное напряжение с выхода источника 3, Часть компараторов 5 срабатывает, их выходные сигналы образуют унитарный код результата преобразования, который далее с помощью элементов 6 преобразуется в позиционный код, т. е, срабатывает тот элемент 6,. второй вход которого подключен к неинвертирующему выходу верхнего (фиг.1) сработавшего коипаратора 5. Позиционный код с выходов элементов 6 подается на входы формирователя 7, который преобразует пряженияБыстродействие повьmдается за счет того, что получение разностного сигнала происходит одновременно с преобразованием аналога в код в, параллельном АЦП 1 и подключением разностного сигнала на вход усилителя 9.Время преобразования определяетсябольшей из двух величин Т,= Т,+ Тили Т = Т. + Т + Т + Тгде Т - время установления разности ввычитающем усилителе Я,вычитающем усилителе 8;Т - время установления выходногонапряжения в усилителе 9;Т - время срабатывания компараторов 5,Т - время срабатывания элементовс6;Ть. - время срабатывания ключей 10,т. е. определяется только одной издвух компонент общего времени.1. Параллельно-последовательный ,аналого-цифровой преобразователь, содержащий источник пороговых напряжений и последовательно соединенные блоки преобразования, состоящие каждый из блока аналого-цифрового преобразования, выполненного на и компараторах (где и = 2 - 1, ш - число разрядов), 1 О (и). элементах И и формирователе выходного кода и, кроме .последнего, из блока цифроаналогового преобразования, выполненного на (и+1) ключах и усилителе разностного сигнала, первые вхо ды компараторов в каждом блоке аналого-цифрового преобразования объединены и являются входной шиной каждого блока преобразования, вторые входы компараторов первого блока преобразо вания соединены с соответствующими первыми выходамиисточника пороговых напряжений, прямые выходы компараторов в каждом блоке аналого-цифрового преобразования, кроме первого компа ратора, соединены с соответствующими первыми входами (и) элементов И, инверсные выходы компараторов, кроме и-го компаратора, соединены соответственно с вторыми входами (и) элеЗО ментов И, выходы (и) элементов И соединены соответственно с (и) входами формирователя выходного кода, выходы которого являются выходными шинами данного блока аналого-цифрового35 преобразования, первые входы и ключей в каждом блоке цифроаналогового преобразования объединены с соответствующими входами формирователя выходного, кода данного блока преобразования, а40 выходы (и+1) ключей объединены и соединены с входом усилителя разностного сигнала, выход которого является выходной шиной каждого блока преобразования, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия в каждый блок аналого-цифрового преобразования введен дополнительный элемент И,ав каждый блок цифроаналоговоо преобразования введен вычитающий усилитель, первые входы всех вычитающих усилителей объединены и соединены с вторым выходом источника пороговых напряжений, второй вход каждого вычитающего усилителя является входной шиной соответствующего блока преобразования, (и+1) выходов вычитающего усилителя соединены соответственно с вторыми входами п ключей и первым входом (а+1)-го ключа, выход дополнительного элемента И соединен с первым входом первого ключа, первый вход дополнительного элемента И является шиной логической единицы, а второй вход соединен с прямым выходом первого компаратора, первые выходы источника пороговых напряжений соединены с соответствующими вторыми входами компараторов каждого блока аналого-цифрового преобразователя, кроме первого, второй вход (и+1)-го ключа соединен с инверсным выходом п-компаратора. 2, Преобразователь по п.1, о т л ич а ю щ и й с я тем, что вычитающий усилитель выполнен на операционном усилителе, четырех резисторах, резистивном делителе напряжения, содержащем (и+1) последовательно соединенных резисторов, первый вход операционногоусилителя соединен с первыми выводами,первого и второго резисторов, второйвывод первого резистора является первым входом вычитающего усилителя, второй вывод второго резистора объединенс первым входом резистивного делителянапряжения и является вторым входом вычитающего усилителя, (и+1) выходов резистивного делителя .напряжения являются (и+1) выходами вычитающегоусилителя, второй вход резистивного делителя напряжения непосредственносоединен с выходом операционного усилителя и через третий резистор - свторым входом операционного усилителя и первым выводом четвертого резистора, второй вывод которого являетсяобщей шиной, 239863-Их Составитель А.Тит Техред Л.Олейник Корректор В.Бутяга дактор А.С Заказ 3409/ Подписи по 113035, 5 изводственно-полиграфическое предприятие, г. Ужгород ектная, 4 Тираж 816 Государственного елам изобретений осква, Ж, Рауш митета ССоткрытийая наб

СмотретьЗаявка

3720866, 04.04.1984

ПРЕДПРИЯТИЕ ПЯ А-3791

ЗАБОЛОТСКИХ ВИКТОР ГЕОРГИЕВИЧ, МЕШКОВ БОРИС МАКСИМОВИЧ, ШТИН ВАДИМ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 1/14

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.06.1986

Код ссылки

<a href="https://patents.su/5-1239863-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Устройство для контроля преобразователей перемещения

Следующий патент: Фотоэлектрический преобразователь угла поворота вала в код

Случайный патент: Способ изготовления светофильтров для коррекции освещенности при экспонировании экранов цветных кинескопов